ZHCUBV0 March 2024 DLPC964

- 1

- 摘要

- 商标

- 1概述

- 2Apps FPGA 模块

- 3功能配置

-

4附录

- 5.1 Vivado Chipscope 捕获结果

- 5.2 DLPC964 Apps 位流加载

- 5.3

使用 Aurora 64B/66B 连接到 DLPC964 控制器

- 5.3.1 工作原理

- 5.3.2 概述

- 5.3.3

Aurora 64B/66B TX 内核和 RTL 生成

- 5.3.3.1 从 IP Catalog 中选择 Aurora 64B66B

- 5.3.3.2 配置 Core Options

- 5.3.3.3 信道配置

- 5.3.3.4 Shared Logic 选项

- 5.3.3.5 生成示例设计文件

- 5.3.3.6 RTL 文件列表

- 5.3.3.7 单通道 3 信道 Aurora 内核 RTL 包装器

- 5.3.3.8 四通道 12 信道顶层 RTL 包装器

- 5.3.3.9 块以块控制字开始

- 5.3.3.10 块以 DMDLOAD_REQ 完成

- 5.3.3.11 DMDLOAD_REQ 建立时间要求

- 5.3.3.12 单通道传输模式

- 5.3.3.13 DMD 块阵列数据映射

- 5.3.3.14 Xilinx IBERT

- 5缩略语和首字母缩写词

- 6米6体育平台手机版_好二三四 (TI) 相关文档

2.16 关键定义

- 块:一个块是 DMD 的一个包含 136 行 x 4096 像素的部分。DMD 分为 16 个这样的块,因此 DMD 的总图像尺寸为 2176 行 x 4096 像素。在 DLPC964 Apps FPGA 中可以对这些块单独寻址 (0x0 - 0xF)。

- 段:每个块有四个段(A、B、C 和 D)。每个段包含 136 行 x 1024 像素。在正常运行中,所有 4 个段同时载入。在慢速模式下,每个段单独载入。

- 组:在双通道模式或四通道模式下,块将分组进行更新。下表列出了这些组。请注意,在双通道模式或四通道模式下,用户必须启用一个组中的所有块或禁用一个组中的所有块,这一点非常重要。

| 块载入地址 | 0x0 | 0x1 | 0x2 | 0x3 | 0x4 | 0x5 | 0x6 | 0x7 | 0x8 | 0x9 | 0xA | 0xB | 0xC | 0xD | 0xE | 0xF |

| 双通道模式组 | 0x0 | 0x2 | 0x4 | 0x6 | 0x8 | 0xA | 0xC | 0xE | ||||||||

| 四通道模式组 | 0x0 | 0x4 | 0x8 | 0xC | ||||||||||||

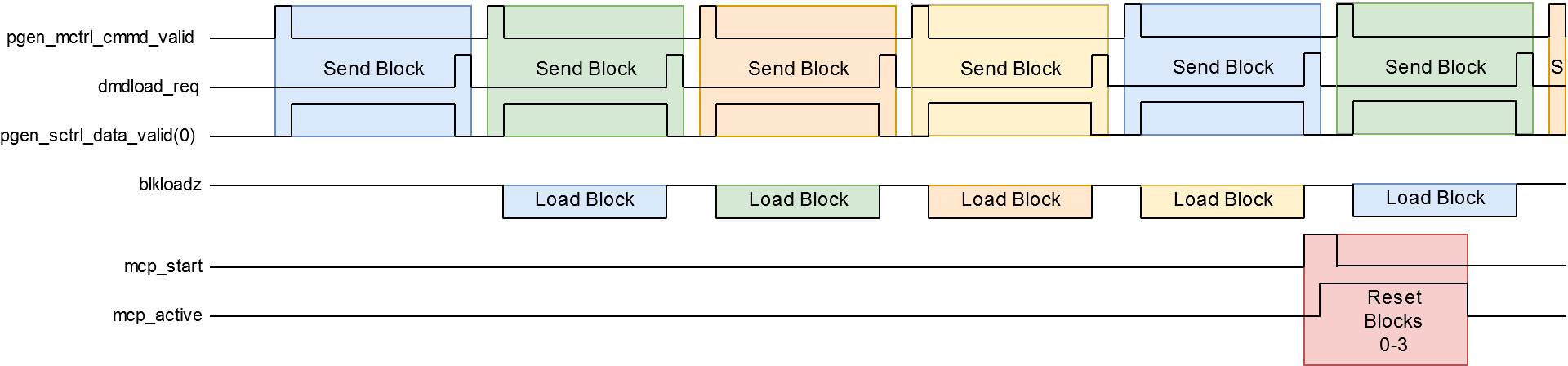

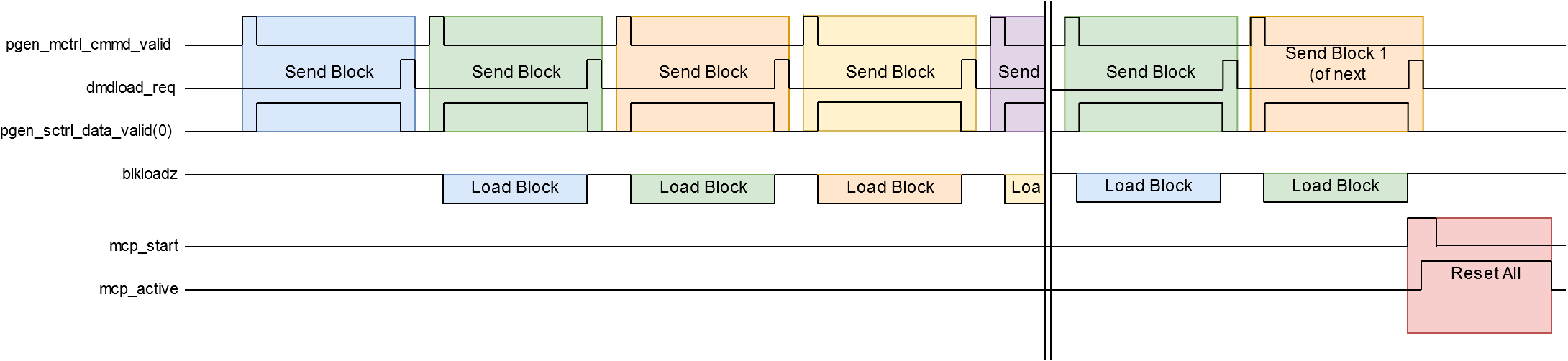

下面是在 x4 模式和全局模式下发送块的简单时序示例。

图 2-9 x4 模式

图 2-9 x4 模式 图 2-10 全局模式

图 2-10 全局模式- DLPC964 Apps:载入了 Apps FPGA 位流的 Xilinx VC707。

- DLPC964:与 DMD 连接的 DLPC964 控制器。

- 模式:有 4 种模式:单通道 (0x0) 模式、双通道或 x2 (0x1) 模式、四通道或 x4 (0x2) 模式和全局 (0x3) 模式。下面和节 3中详细介绍了这些模式。

- 单通道 (0x0) 模式:在单通道模式下,每个块中加载数据,一旦 DLPC964 完成将单个块加载到 DMD 的过程,DMD 就会通过 MCP_Start 信号进行更新。由于每个块可单独更新,因此有效的块模式地址为 0x0 - 0xF。

- 双通道 (0x1) 模式:双通道模式意味着,一旦 DLPC964 在一个组的 2 个块中加载了数据,DMD 就会使用单个 MCP_Start 信号更新这两个块。由于一次更新 2 个块,因此有效的块模式地址为 0x0、0x2、0x4、0x6、0x8、0xA、0xC 和 0xE。注: 请注意,在双通道模式中启用和禁用块时,必须启用或禁用组中的所有块。

- 四通道 (0x2) 模式:四通道模式意味着,一旦 DLPC964 在一个组的 4 个块中加载了数据,DMD 就会使用单个 MCP_Start 信号更新所有这 4 个块。由于一次更新 4 个块,因此有效的块模式地址为 0x0、0x4、0x8 和 0xC。

- 全局 (0x3) 模式:这是默认启动模式。在全局模式下,所有已启用的块都会加载,一旦 DLPC964 完成,MCP_Start 信号就会一次性更新所有块。由于已经一次性更新所有块,因此下一个负载操作需要等待,直至微镜达到稳定状态。注: 这一时间称为微镜稳定时间,必须约为 8us。

- 块加载类型:使用 Aurora GTX 接口中的 user-k 在数据之前先发送块加载类型。DMD 支持 3 种不同类型的加载:正常 (0x0)、清除 (0x1) 和置位 (0x2)。

- 正常 (0x0):这是默认的块加载类型。正常加载类型指示 DLPC964 在 DMD 中加载出现在 user-k 数据之后的任何数据。

- 清除 (0x1):清除加载类型不发送任何数据。这是因为当 DLPC964 接收到清除加载类型时,DLPC964 会将指定块中的微镜设置为关闭状态 (0)。

- 置位 (0x2):置位加载类型不发送任何数据。这是因为当 DLPC964 接收到置位加载类型时,DLPC964 会将指定块中的镜像设置为开启状态 (1)。

- MCP_Start:MCP_Start(微镜时钟脉冲启动)指示 DMD 以发送的任何数据更新微镜。DLPC964 根据所选模式和块模式地址确定要更新的块。

- 像素行/行:像素行是指 4096 个像素的水平行。这可以看作是 DMD 上的 y 位置。

- 像素列/列:像素列是指 2176 个像素的垂直列。这可以看作是 DMD 上的 x 位置。

- 快速/慢速模式:默认情况下启用快速模式。快速模式在 4 个 Aurora GTX 通道上并行发送一个块的所有 4 个段。慢速模式仅使用第一个 GTX 通道并按顺序发送段。更多有关段排序的详细信息,请参阅“图形模式”部分。

- Load2 模式:默认情况下禁用 Load2 模式。在 Load2 模式下,DLPC964 Apps 仅发送指定行数的一半(请求 136 行时,仅发送 68 行)。这是因为在该模式下,DMD 每 2 行加载一次相同的数据。