ZHCUBV0 March 2024 DLPC964

- 1

- 摘要

- 商标

- 1概述

- 2Apps FPGA 模块

- 3功能配置

-

4附录

- 5.1 Vivado Chipscope 捕获结果

- 5.2 DLPC964 Apps 位流加载

- 5.3

使用 Aurora 64B/66B 连接到 DLPC964 控制器

- 5.3.1 工作原理

- 5.3.2 概述

- 5.3.3

Aurora 64B/66B TX 内核和 RTL 生成

- 5.3.3.1 从 IP Catalog 中选择 Aurora 64B66B

- 5.3.3.2 配置 Core Options

- 5.3.3.3 信道配置

- 5.3.3.4 Shared Logic 选项

- 5.3.3.5 生成示例设计文件

- 5.3.3.6 RTL 文件列表

- 5.3.3.7 单通道 3 信道 Aurora 内核 RTL 包装器

- 5.3.3.8 四通道 12 信道顶层 RTL 包装器

- 5.3.3.9 块以块控制字开始

- 5.3.3.10 块以 DMDLOAD_REQ 完成

- 5.3.3.11 DMDLOAD_REQ 建立时间要求

- 5.3.3.12 单通道传输模式

- 5.3.3.13 DMD 块阵列数据映射

- 5.3.3.14 Xilinx IBERT

- 5缩略语和首字母缩写词

- 6米6体育平台手机版_好二三四 (TI) 相关文档

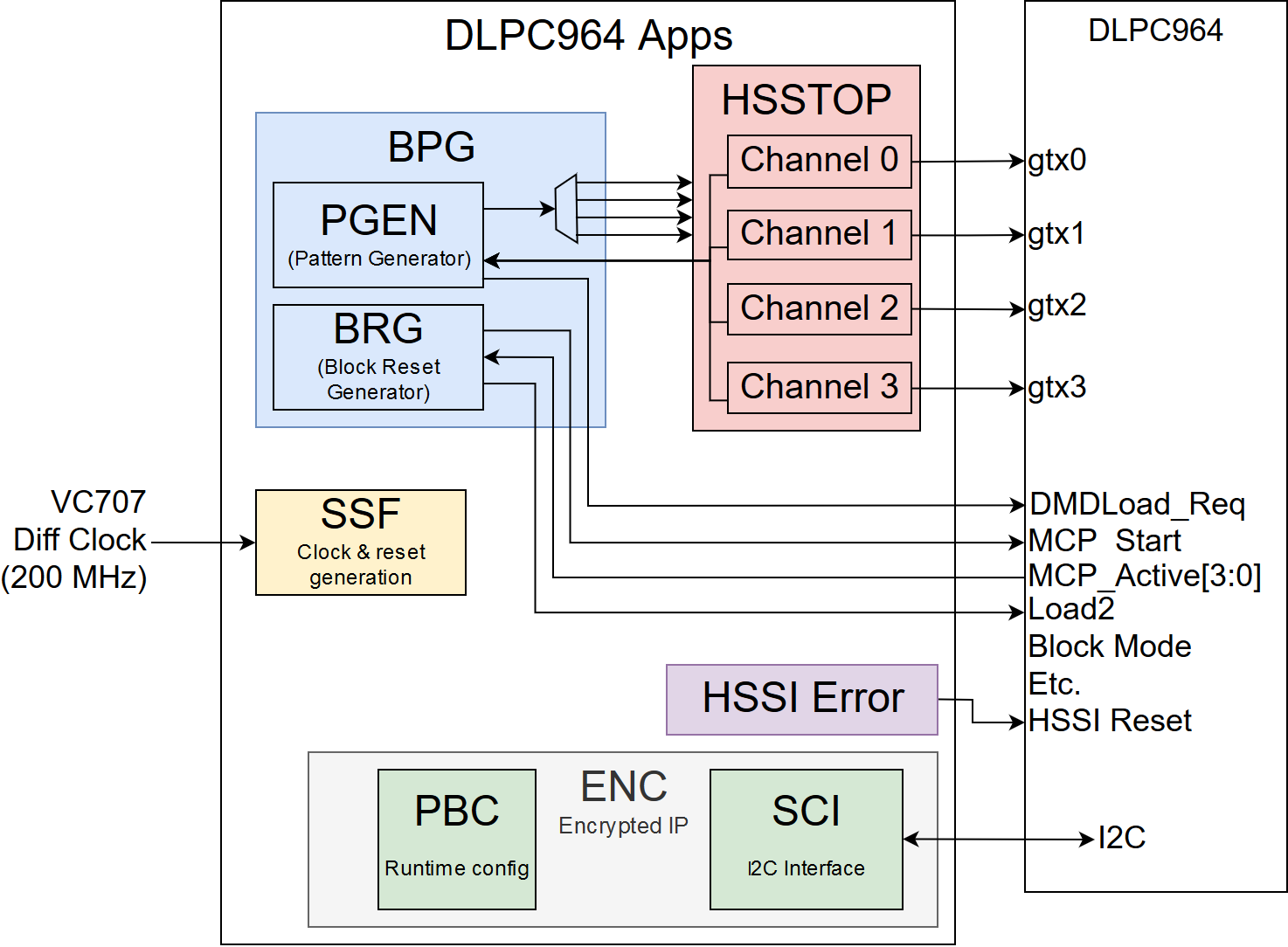

2.1 Apps FPGA 方框图

图 2-1 展示了包含不同模块的 Apps FPGA 硬件方框图。每个模块都在将位平面数据传输至 DLPC964 控制器的过程中发挥着重要作用。DLPC964 接收来自外部前端源 (AMD Xilinx Virtex-7 VC-707) 的高速位平面数据,并对该数据进行格式转换,然后再加载到 DLPLCR99EVM 中,以便在 DLP991U DMD 上显示。

与 DLPC964 Apps FPGA 连接的主要模块是位平面图形发生器 (BPG),有助于监测从 PGEN 加载到 DLPC964 控制器的位平面数据。块复位发生器 (BRG) 有助于在控制器不繁忙时启动发送到 DLPC964 的 PGEN 数据,繁忙状态由来自 DLPC964 控制器的 mcp_active 信号确定。

一旦准备好将数据加载到 PGEN 中,便会通过 HSSTOP 发送位平面数据,HSSTOP 是所有四个 GTX 通道 (gtx0 - gtx3) 的包装器。每个通道都有助于将位平面数据发送到 DLPC964 控制器,每个通道的速度高达 10Gbps。下面将进一步详细说明这些模块。

图 2-1 Apps FPGA 硬件方框图

图 2-1 Apps FPGA 硬件方框图