ZHCUBV0 March 2024 DLPC964

- 1

- 摘要

- 商标

- 1概述

- 2Apps FPGA 模块

- 3功能配置

-

4附录

- 5.1 Vivado Chipscope 捕获结果

- 5.2 DLPC964 Apps 位流加载

- 5.3

使用 Aurora 64B/66B 连接到 DLPC964 控制器

- 5.3.1 工作原理

- 5.3.2 概述

- 5.3.3

Aurora 64B/66B TX 内核和 RTL 生成

- 5.3.3.1 从 IP Catalog 中选择 Aurora 64B66B

- 5.3.3.2 配置 Core Options

- 5.3.3.3 信道配置

- 5.3.3.4 Shared Logic 选项

- 5.3.3.5 生成示例设计文件

- 5.3.3.6 RTL 文件列表

- 5.3.3.7 单通道 3 信道 Aurora 内核 RTL 包装器

- 5.3.3.8 四通道 12 信道顶层 RTL 包装器

- 5.3.3.9 块以块控制字开始

- 5.3.3.10 块以 DMDLOAD_REQ 完成

- 5.3.3.11 DMDLOAD_REQ 建立时间要求

- 5.3.3.12 单通道传输模式

- 5.3.3.13 DMD 块阵列数据映射

- 5.3.3.14 Xilinx IBERT

- 5缩略语和首字母缩写词

- 6米6体育平台手机版_好二三四 (TI) 相关文档

4.3.3.8 四通道 12 信道顶层 RTL 包装器

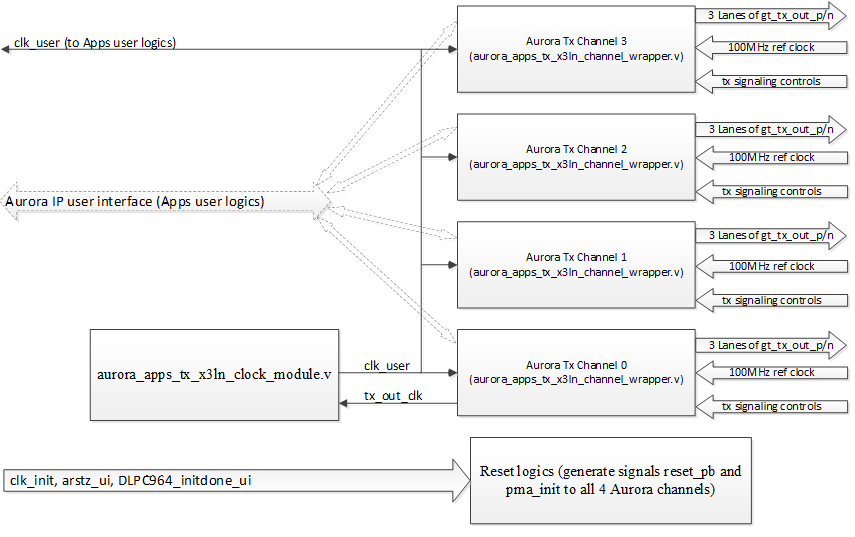

图 4-17 所示的 aurora_apps_tx_x12ln.v 具有模块 aurora_apps_tx_x3ln_channel_wrapper.v 的四个实例,旨在形成四个 Aurora TX 通道实体。

通道 0 的 tx_out_clk 会馈送到 aurora_apps_tx_x3ln_clock_module.v 中以生成用于驱动 Apps FPGA 和 Aurora 用户逻辑接口的 clk_user。请参阅 Xilinx 应用手册的第 2 章表 2-7:Aurora 64B/66B 内核时钟端口 和第 3 章图 3-1 Aurora 64B/66B 时钟架构,了解有关 tx_out_clk 和 clk_user 的信息。

复位逻辑会为四个 Aurora TX 通道生成复位信号 reset_pb 和 pma_init。如需了解有关生成 reset_pb 和 pma_init 的规格,请参阅 Xilinx 应用手册的第 3 章图 3-5 Aurora 64B/66B 单工正常运行复位序列。

图 4-17 Aurora_apps_tx_x12ln.v RTL 方框图

图 4-17 Aurora_apps_tx_x12ln.v RTL 方框图| 名称 | 方向 | 时钟域 | 说明 |

|---|---|---|---|

| clk_init | 输入 | clk_init | 用于为 Aurora 内核生成复位信号的 100MHz 自由运行时钟。 |

| arstz_ui | 输入 | async | 低电平有效复位输入。输入低电平将触发 Aurora 内核的复位操作。 |

| dlpc964_initdone_ui | 输入 | async | DLPC964 控制器 INIT_DONE 状态信号。低电平使 Aurora 内核保持复位状态。 |

gt0_txout_n[0:2] |

输出 | async | 连接到 DLPC964 控制器的通道 0 10Gbps 差分输出信道 0、1 和 2。 |

| gt1_txout_p[0:2] |

输出 | async | 连接到 DLPC964 控制器的通道 1 10Gbps 差分输出信道 0、1 和 2。 |

| gt2_txout_p[0:2] |

输出 | async | 连接到 DLPC964 控制器的通道 2 10Gbps 差分输出信道 0、1 和 2。 |

| gt3_txout_p[0:2] |

输出 | async | 连接到 DLPC964 控制器的通道 3 10Gbps 差分输出信道 0、1 和 2。 |

| gt0_refclkin_p |

输入 | async | 来自低抖动振荡器的通道 0 100MHz 差分收发器外部基准时钟。 |

| gt1_refclkin_p |

输入 | async | 来自低抖动振荡器的通道 1 100MHz 差分收发器外部基准时钟。 |

| gt2_refclkin_p |

输入 | async | 来自低抖动振荡器的通道 2 100MHz 差分收发器外部基准时钟。 |

| gt3_refclkin_p |

输入 | async | 来自低抖动振荡器的通道 3 100MHz 差分收发器外部基准时钟。 |

| gt_txpostcursor_in[4:0] | 输入 | async |

收发器后标 TX 预加重控制,对于 TI EVM 硬件,设置为“00000”。 客户必须执行 IBERT 眼图扫描以确定硬件的最佳设置。 |

| gt_txdiffctrl_in[3:0] | 输入 | async |

收发器 TX 驱动器摆幅控制,对于 TI EVM 硬件,设置为“1000”(807mV 差分峰峰值摆幅)。 客户必须执行 IBERT 眼图扫描以确定硬件的最佳设置。 |

| gt_txmaincursor_in[6:0] | 输入 | async | 收发器主标 TX 控制,对于 TI EVM 硬件,设置为“0000000”。客户必须执行 IBERT 眼图扫描以确定硬件的最佳设置。 |

| gt_txprecursor_in[4:0] | 输入 | async | 收发器前标 TX 预加重控制,对于 TI EVM 硬件,设置为“00000”。客户必须执行 IBERT 眼图扫描以确定硬件的最佳设置。 |

| clk_user | 输出 | clk_user | 连接到 Aurora 内核的用户接口的 156.25MHz 时钟。 |

| clk_user_not_locked_uo | 输出 | async | 处于高电平时,表示 clk_user 未被锁定,如果 clk_user 在上电或系统复位条件下锁定松动,则可用于将用户逻辑保持在复位状态。 |

| gt(0,1,2,3)_s_axi_tx_tdata[191:0] | 输入 | clk_user | 要通过 Aurora 链路发送的 DMD 像素数据。 |

| gt(0,1,2,3)_s_axi_tx_tvalid | 输入 | clk_user | 用户逻辑将此信号置为高电平有效以向 Aurora 内核指示 DMD 像素数据有效,因此可进行发送。Aurora 内核在 tvalid 为低电平时会忽略数据。请参阅 Xilinx 应用手册,了解 AXI4-stream tready 信号行为。 |

| gt(0,1,2,3)_s_axi_tx_tready | 输出 | clk_user | 当接受 DMD 像素数据时,Aurora 内核将此信号置为高电平有效。当忽略像素数据时(例如内核未准备好接受数据),置为无效。请参阅 Xilinx 应用手册,了解 AXI4-stream tready 信号行为。 |

| gt(0,1,2,3)_s_axi_user_k_tx_tdata[191:0] | 输入 | clk_user | 要通过 Aurora 链路发送的 user-k 控制字数据。 |

| gt(0,1,2,3)_s_axi_user_k_tx_tvalid | 输入 | clk_user | 用户逻辑将此信号置为高电平有效以向 Aurora 内核指示 user-k 控制字数据有效,因此可进行发送。Aurora 内核在 tvalid 为低电平时会忽略数据。 |

| gt(0,1,2,3)_s_axi_user_k_tx_tready | 输出 | clk_user | 当接受 user-k 控制字数据时,Aurora 内核将此信号置为高电平有效。当忽略数据时(例如内核未准备好接受数据),置为无效。 |

| gt(0,1,2,3)_hard_err | 输出 | clk_user | Aurora 内核检测到硬错误时,置为高电平有效。如需了解硬错误定义,请参阅 Xilinx 应用手册中的表 2-13。 |

| gt(0,1,2,3)_soft_err | 输出 | clk_user | Aurora 内核检测到软错误时,置为高电平有效。如需了解软错误定义,请参阅 Xilinx 应用手册中的表 2-13。 |

| gt(0,1,2,3)_channel_up | 输出 | clk_user | Aurora 内核完成通道初始化序列后,置为高电平有效。 |

| gt(0,1,2,3)_lane_up[2:0] | 输出 | clk_user | 成功进行信道初始化后使每个信道置为高电平有效(每个位代表一个信道)。 |

| tp_gt0_pll_lock | 输出 | async |

Aurora 通道 0 tx_out_clk 处于稳定状态时,置为高电平有效。如前一节所述,通道 0 tx_out_clk 用于生成 clk_user。 tx_out_clk 是来自 Aurora 收发器的 312.5MHz,除以 2 形成 156.25MHz 的 clk_user。 |