ZHCUBV0 March 2024 DLPC964

- 1

- 摘要

- 商标

- 1概述

- 2Apps FPGA 模块

- 3功能配置

-

4附录

- 5.1 Vivado Chipscope 捕获结果

- 5.2 DLPC964 Apps 位流加载

- 5.3

使用 Aurora 64B/66B 连接到 DLPC964 控制器

- 5.3.1 工作原理

- 5.3.2 概述

- 5.3.3

Aurora 64B/66B TX 内核和 RTL 生成

- 5.3.3.1 从 IP Catalog 中选择 Aurora 64B66B

- 5.3.3.2 配置 Core Options

- 5.3.3.3 信道配置

- 5.3.3.4 Shared Logic 选项

- 5.3.3.5 生成示例设计文件

- 5.3.3.6 RTL 文件列表

- 5.3.3.7 单通道 3 信道 Aurora 内核 RTL 包装器

- 5.3.3.8 四通道 12 信道顶层 RTL 包装器

- 5.3.3.9 块以块控制字开始

- 5.3.3.10 块以 DMDLOAD_REQ 完成

- 5.3.3.11 DMDLOAD_REQ 建立时间要求

- 5.3.3.12 单通道传输模式

- 5.3.3.13 DMD 块阵列数据映射

- 5.3.3.14 Xilinx IBERT

- 5缩略语和首字母缩写词

- 6米6体育平台手机版_好二三四 (TI) 相关文档

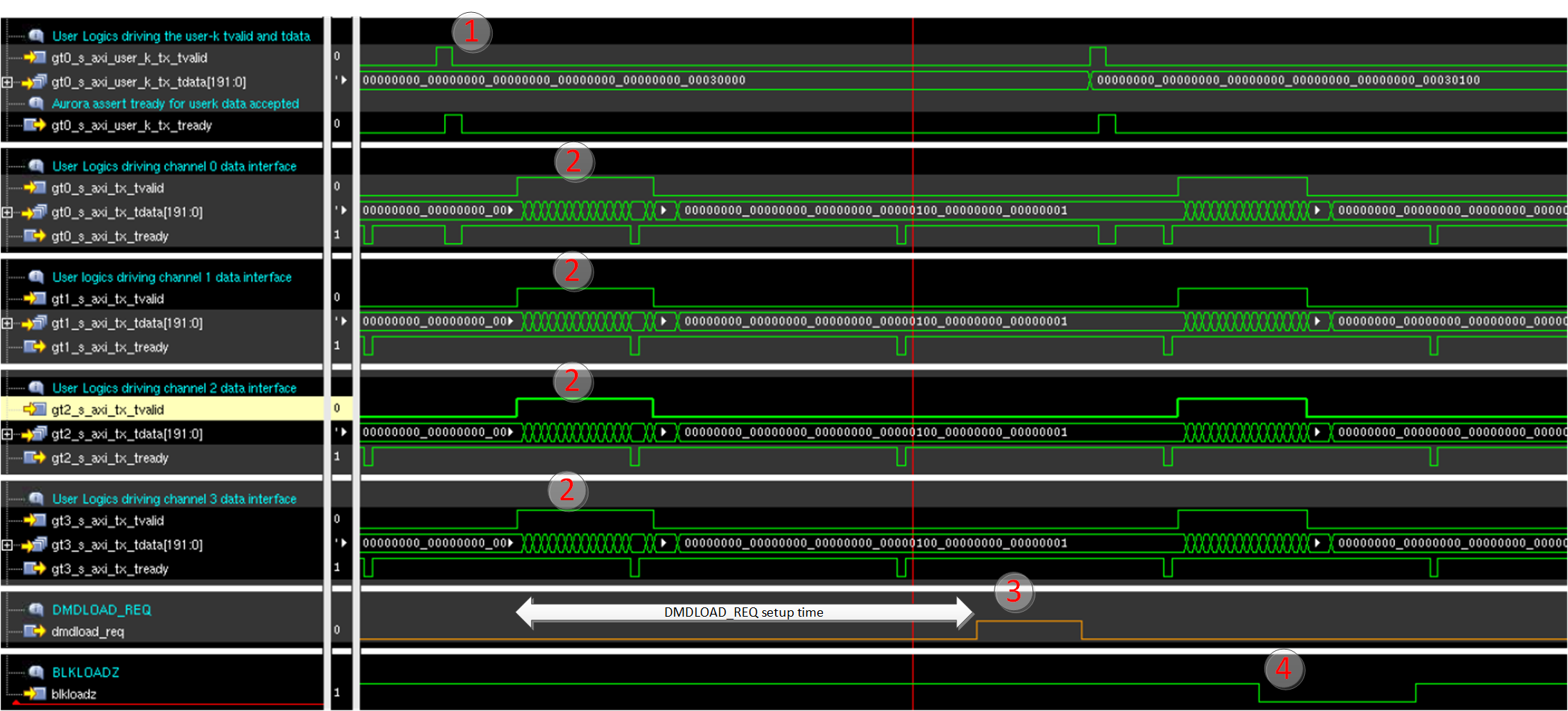

4.3.3.11 DMDLOAD_REQ 建立时间要求

在传输完一个 Aurora 块后,只要满足在发送该块的第一个数据包后至少经过了 300ns,Apps FPGA 用户逻辑即可将 DMDLOAD_REQ 信号置为有效。之所以需要这样的建立时间,是因为 Aurora TX/RX 通道路径有 300ns 的发送延时,旨在验证 DLPC964 在 Aurora 块数据到达后收到了 DMDLOAD_REQ 标志。

在大多数情况下,由于数据块足够大,因此可以确认从发送数据块的第一个有效数据包到最后一个数据包的经历时间超过 300ns,此时 Apps 能够将 DMDLOAD_REQ 信号置为有效,所以这 300ns 的建立时间要求将自然得到满足。Apps FPGA 尝试发送一个小的不完整 DMD 块时,这种情况下 300ns 的建立时间窗口变得至关重要,如图 4-21 中的示例所示,Apps FPGA 将不完整 DMD 块的总共 3 行(表 4-2,ROW_LENGTH = 3)发送到 DLPC964:

图 4-21 三个 DMD 行的加载操作的 DMDLOAD_REQ 建立时间

图 4-21 三个 DMD 行的加载操作的 DMDLOAD_REQ 建立时间- APPS FPGA 发送一个块控制字以指示 Aurora 块传输开始。

- 通过四个 Aurora 数据接口通道发送三个数据行后,Apps FPGA 等待 300ns 的建立时间到期,然后再发出 DMDLOAD_REQ。注: 300ns 是从数据接口上的第一个 TVALID 开始进行测量的。

- 一旦满足建立时间,Apps FPGA 就会将 DMDLOAD_REQ 置为有效。

- BLKLOADZ 由 DLPC964 置为有效以指示 DMD 数据加载操作正在运行。

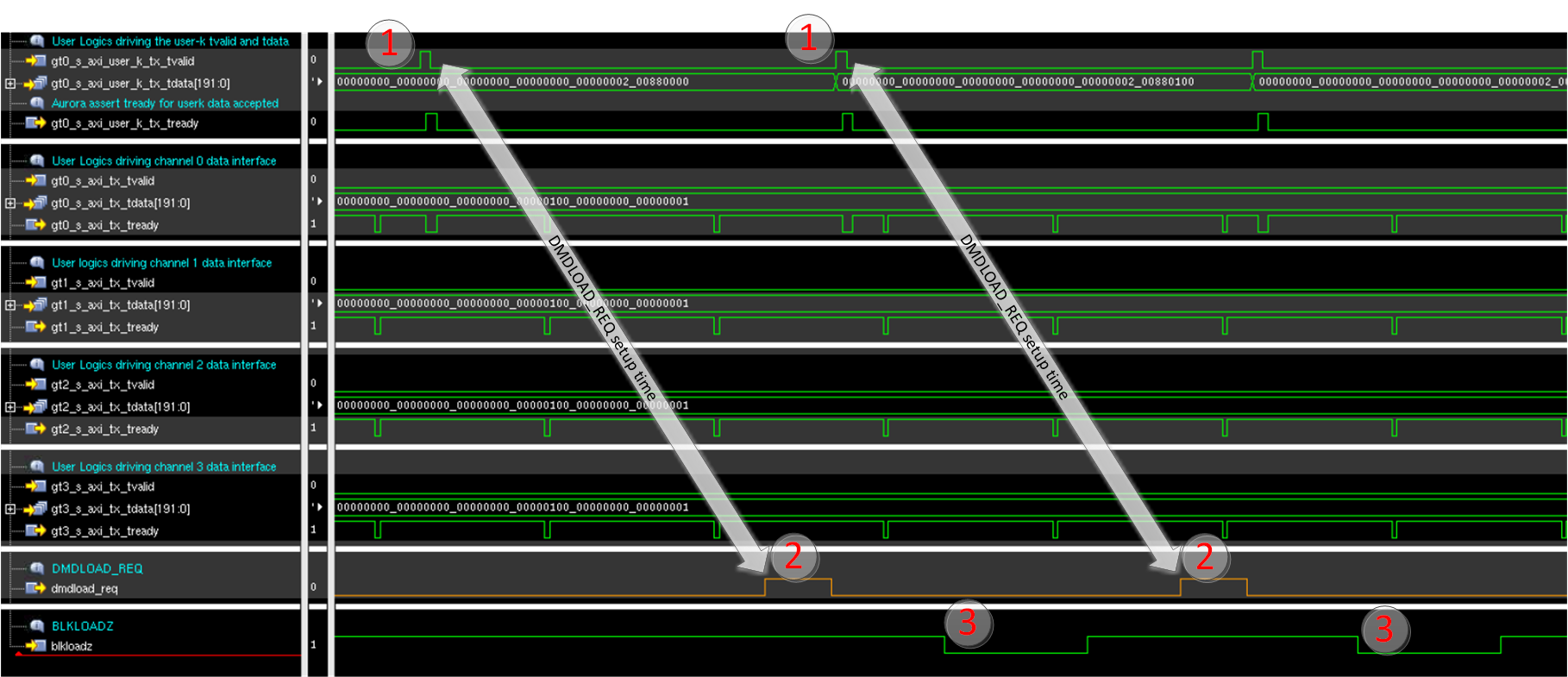

对于不需要数据包的操作,例如块清除(表 3,LOAD_TYPE = 001)和块置位(表 3,LOAD_TYPE = 010),这 300ns 的建立时间 DMDLOAD_REQ 仍然是必需的,并从块控制字数据包测得。图 4-22 是一个块置位操作的示例。

图 4-22 块置位操作的 DMDLOAD_REQ 建立时间

图 4-22 块置位操作的 DMDLOAD_REQ 建立时间- Apps FPGA 发送一个块控制字数据包以启动块置位操作。请注意,该操作不需要任何块数据,因为四个数据接口保持空闲状态 (gtX_s_axi_tx_tvalid = ‘0’)。

- Apps FPGA 在 300ns 的建立时间后将 DMDLOAD_REQ 置为有效。由于块置位操作不需要 Aurora 数据传输,因此这 300ns 的建立时间从块控制字测得。

- DLPC964 将 BLKLOADZ 置为有效以指示正在进行块置位操作。