ZHCUBV0 March 2024 DLPC964

- 1

- 摘要

- 商标

- 1概述

- 2Apps FPGA 模块

- 3功能配置

-

4附录

- 5.1 Vivado Chipscope 捕获结果

- 5.2 DLPC964 Apps 位流加载

- 5.3

使用 Aurora 64B/66B 连接到 DLPC964 控制器

- 5.3.1 工作原理

- 5.3.2 概述

- 5.3.3

Aurora 64B/66B TX 内核和 RTL 生成

- 5.3.3.1 从 IP Catalog 中选择 Aurora 64B66B

- 5.3.3.2 配置 Core Options

- 5.3.3.3 信道配置

- 5.3.3.4 Shared Logic 选项

- 5.3.3.5 生成示例设计文件

- 5.3.3.6 RTL 文件列表

- 5.3.3.7 单通道 3 信道 Aurora 内核 RTL 包装器

- 5.3.3.8 四通道 12 信道顶层 RTL 包装器

- 5.3.3.9 块以块控制字开始

- 5.3.3.10 块以 DMDLOAD_REQ 完成

- 5.3.3.11 DMDLOAD_REQ 建立时间要求

- 5.3.3.12 单通道传输模式

- 5.3.3.13 DMD 块阵列数据映射

- 5.3.3.14 Xilinx IBERT

- 5缩略语和首字母缩写词

- 6米6体育平台手机版_好二三四 (TI) 相关文档

2.7 PGEN_SCTRL 模块

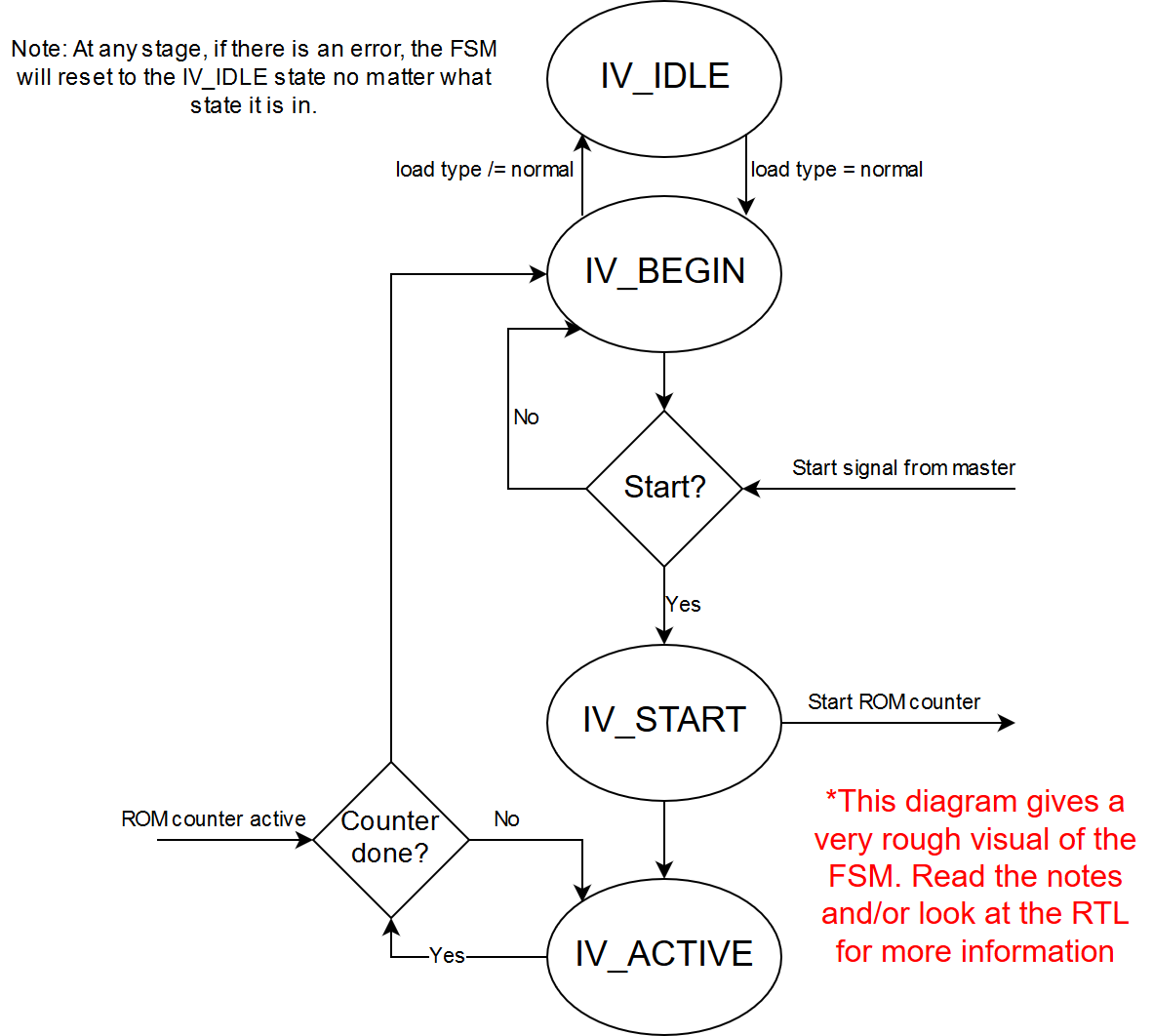

辅助控制模块有四个由主控制模块控制的副本。每个辅助模块负责发送正确长度的数据有效信号并使 ROM 地址递增。数据有效信号进入 Aurora 接口以将发送的数据标记为有效。Aurora 接口能够在不同的时间将就绪信号置为无效,因此辅助模块必须将这一点考虑在内,即需要保存这些值和有效信号直到就绪信号重新置为有效。主控制模块将最大 ROM 地址发送到辅助模块。辅助模块可递增计数至该值,从而允许 ROM 以用户指定的数量发出相应行数。图 2-7 展示了主要的辅助 FSM,其中每个状态机的定义如下:

- IV_IDLE:当不需要辅助模块时(例如,当选择的加载类型为清除或置位时),辅助模块将保持在这种空闲状态。如果需要数据(加载类型 = 正常),则 FSM 进入下一个状态。

- IV_BEGIN:等待主模块发送启动信号。收到之后,辅助模块进入下一状态。否则,FSM 会保持此状态,直到 FSM 接收到启动信号或加载类型发生变化。

- IV_START:FSM 会启动发送有效信号和 ROM 地址的过程。有效信号会延迟几个时钟周期以便使 ROM 输出与有效信号对齐。

- IV_ACTIVE:一旦启动辅助模块,输出 ROM 地址的过程将继续运行,直到辅助模块到达了主模块发送的 ROM 地址。一旦到达该值,FSM 就会根据指示进入起始状态。

图 2-7 PGEN_SCTRL FSM

图 2-7 PGEN_SCTRL FSM