ZHCUBV0 March 2024 DLPC964

- 1

- 摘要

- 商标

- 1概述

- 2Apps FPGA 模块

- 3功能配置

-

4附录

- 5.1 Vivado Chipscope 捕获结果

- 5.2 DLPC964 Apps 位流加载

- 5.3

使用 Aurora 64B/66B 连接到 DLPC964 控制器

- 5.3.1 工作原理

- 5.3.2 概述

- 5.3.3

Aurora 64B/66B TX 内核和 RTL 生成

- 5.3.3.1 从 IP Catalog 中选择 Aurora 64B66B

- 5.3.3.2 配置 Core Options

- 5.3.3.3 信道配置

- 5.3.3.4 Shared Logic 选项

- 5.3.3.5 生成示例设计文件

- 5.3.3.6 RTL 文件列表

- 5.3.3.7 单通道 3 信道 Aurora 内核 RTL 包装器

- 5.3.3.8 四通道 12 信道顶层 RTL 包装器

- 5.3.3.9 块以块控制字开始

- 5.3.3.10 块以 DMDLOAD_REQ 完成

- 5.3.3.11 DMDLOAD_REQ 建立时间要求

- 5.3.3.12 单通道传输模式

- 5.3.3.13 DMD 块阵列数据映射

- 5.3.3.14 Xilinx IBERT

- 5缩略语和首字母缩写词

- 6米6体育平台手机版_好二三四 (TI) 相关文档

4.3.3.9 块以块控制字开始

Aurora 是没有 DMD 块概念的通用数据传输链路。要定义 DMD 块的开始,Apps 用户逻辑必须在数据传输之前通过通道 0 Aurora user-k 端口发送块控制字数据包。

如需有关 Aurora user-k 接口端口的详细信息,请参阅 Xilinx 应用手册第 2 章的表 2-10。总之,user-k 接口端口用于实现特定于应用的控制功能,独立于数据接口,且优先级高于数据接口。如表 4-2 所示,RTL 包装器 aurora_apps_tx_x12ln.v 有四个 user-k 端口接口通道向 Apps FPGA 用户逻辑公开。

| 信号名称 | 信号方向 | DLPC964 应用使用情况 |

|---|---|---|

| gt0_s_axi_user_k_tx_tdata[191:0] | Aurora 通道 0 的输入 | 要发送的 192 位块控制字数据包 |

| gt0_s_axi_user_k_tx_tvalid | Aurora 通道 0 的输入 |

用户逻辑将此信号置为高电平有效以向 Aurora 内核指示块控制字有效,因此可进行发送。 Aurora 内核在 tvalid 为低电平时会忽略字。 |

| gt0_s_axi_user_k_tx_tready | Aurora 通道 0 的输出 |

当接受块控制字时,Aurora 内核将此信号置为高电平有效。 当忽略字时(例如内核未准备好接受输入字),置为无效。 |

| gt1_s_axi_user_k_tx_tdata[191:0] | Aurora 通道 1 的输入 | 未使用 |

| gt1_s_axi_user_k_tx_tvalid | Aurora 通道 1 的输入 | 未使用 |

| gt1_s_axi_user_k_tx_tready | Aurora 通道 1 的输出 | 未使用 |

| gt2_s_axi_user_k_tx_tdata[191:0] | Aurora 通道 2 的输入 | 未使用 |

| gt2_s_axi_user_k_tx_tvalid | Aurora 通道 2 的输入 | 未使用 |

| gt2_s_axi_user_k_tx_tready | Aurora 通道 2 的输出 | 未使用 |

| gt3_s_axi_user_k_tx_tdata[191:0] | Aurora 通道 3 的输入 | 未使用 |

| gt3_s_axi_user_k_tx_tvalid | Aurora 通道 3 的输入 | 未使用 |

| gt3_s_axi_user_k_tx_tready | Aurora 通道 3 的输出 | 未使用 |

表 4-3 介绍了 192 位块控制字中的各种字段。块控制字不仅定义了 DMD 块的开始,还包含关于 DLPC964 控制器如何处理 DMD 块数据接收的指导说明和信息。

| 字段位置 | 字段类型 | 字段说明 |

|---|---|---|

| gt0_s_axi_user_k_tx_tdata[7:0] | USER_BLOCK_NUMBER | 必须设置为零 (0x00)。0x00 以外的值均无效,如果此字段不为零,DLPC964 控制器会忽略整个 192 位控制字。 |

| gt0_s_axi_user_k_tx_tdata[11:8] | BLOCK_ADDRESS |

指示 DLPC964 将操作应用到的 DMD 块地址。 0000:DMD 块 0 0001:DMD 块 1 0010:DMD 块 2 ….…. 1111:DMD 块 15 |

| gt0_s_axi_user_k_tx_tdata[15:7] | 保留,未使用。 | |

| gt0_s_axi_user_k_tx_tdata[24:16] | ROW_LENGTH | DLPC964 加载用户数据的行数。DLP991U DMD 在每个块中有 136 行,因此有效范围为 1-136。包括 0 在内的所有其他值均无效。设置为 136 表示执行全块的操作。值 1 至 135 表示非全块的操作。 注: 在 LOAD_TYPE 为 000 时使用此字段。 |

| gt0_s_axi_user_k_tx_tdata[34:32] | LOAD_TYPE |

000:块加载。DLPC964 将用户数据加载到由 BLOCK_ADDRESS 和 ROW_LENGTH 定义的 DMD 阵列区域中。 001:块清除。DLPC964 将 DMD 阵列中由 BLOCK_ADDRESS 定义的整个块清零。 010:块置位。DLPC964 将 DMD 阵列中由 BLOCK_ADDRESS 定义的整个块设置为 1。其他值:保留,请勿使用。 注: 在 001(块清除)或 010(块置位)操作中,ROW_LENGTH 和 NORTH_SOUTH_FLIP 字段会被忽略,因为清除和置位操作会影响整个 DMD 块阵列。换句话说,块置位/清除操作不支持非全块的操作。

|

| gt0_s_axi_user_k_tx_tdata[36] | NORTH_SOUTH_FLIP |

控制 DMD 块内的数据加载方向。 0:DLPC964 从第 1 行开始加载数据并向上计数。 1:DLPC964 从第 136 行开始加载数据并向下计数。 |

| gt0_s_axi_user_k_tx_tdata[29:28] | DMD_SEGMENT |

当 SINGLE_CHANNEL_MODE =“1”时,选择 DLC964 将操作应用到的 DMD 段。 如果 SINGLE_CHANNEL_MODE =“0”,DLPC964 控制器会忽略此字段。 |

| gt0_s_axi_user_k_tx_tdata[30] | SINGLE_CHANNEL_MODE |

1:单通道运行模式。仅使用 Aurora 通道 0 运行 DMD 阵列。 0:正常运行模式。使用所有四个 Aurora 通道运行 DMD 阵列。 |

| gt0_s_axi_user_k_tx_tdata[191:31] | 保留,未使用。 |

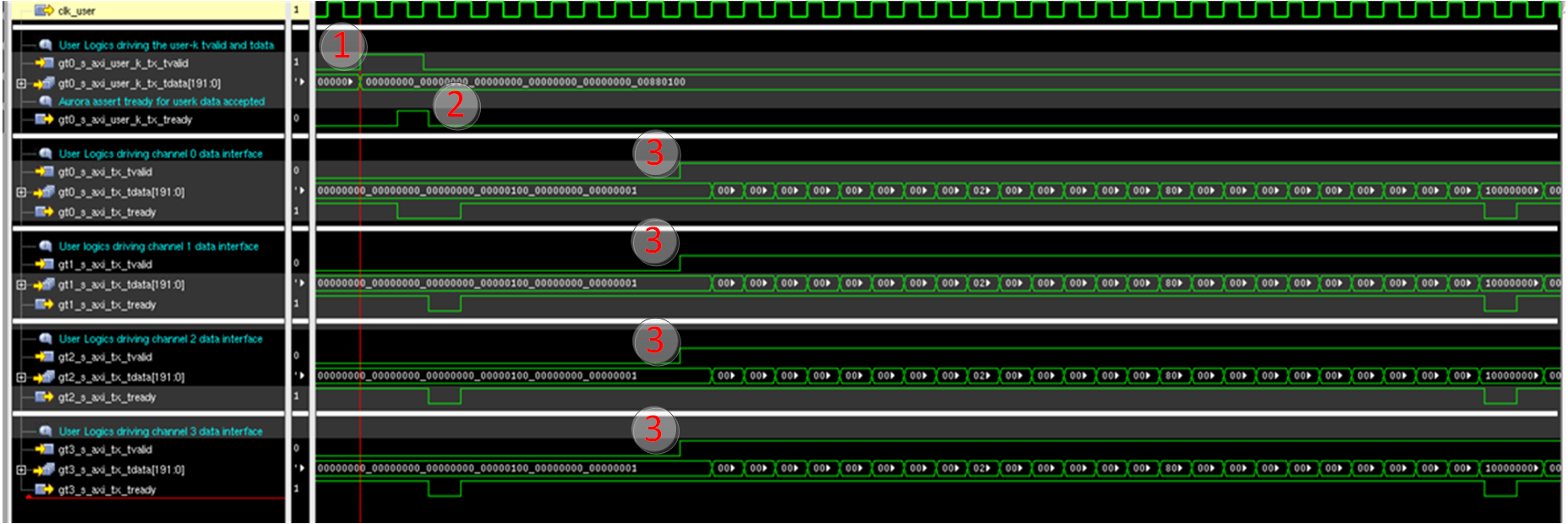

图 4-18 显示了 Aurora 块发送开始时通过通道 0 user-k 端口发送 192 位块控制字(本例中加载 DMD 块 1 的全部 136 行)。

图 4-18 块以块控制字开始的波形

图 4-18 块以块控制字开始的波形- 通过在 gt0_s_axi_user_k_tx_tdata[191:0] 总线上使用正确的块控制字,Apps FPGA 用户逻辑将 TVALID 标志 (gt0_s_axi_user_k_tx_tvalid) 置为有效,并等待 Aurora 内核的响应。

- Aurora 将 TREADY 标志 gt0_s_axi_user_k_tx_tready 置为有效,指示内核已接受 192 位 user-k 数据。

- 发送块控制字后,Apps FPGA 用户逻辑开始在全部四个数据接口上进行 Aurora 块传输。