ZHCUBV0 March 2024 DLPC964

- 1

- 摘要

- 商标

- 1概述

- 2Apps FPGA 模块

- 3功能配置

-

4附录

- 5.1 Vivado Chipscope 捕获结果

- 5.2 DLPC964 Apps 位流加载

- 5.3

使用 Aurora 64B/66B 连接到 DLPC964 控制器

- 5.3.1 工作原理

- 5.3.2 概述

- 5.3.3

Aurora 64B/66B TX 内核和 RTL 生成

- 5.3.3.1 从 IP Catalog 中选择 Aurora 64B66B

- 5.3.3.2 配置 Core Options

- 5.3.3.3 信道配置

- 5.3.3.4 Shared Logic 选项

- 5.3.3.5 生成示例设计文件

- 5.3.3.6 RTL 文件列表

- 5.3.3.7 单通道 3 信道 Aurora 内核 RTL 包装器

- 5.3.3.8 四通道 12 信道顶层 RTL 包装器

- 5.3.3.9 块以块控制字开始

- 5.3.3.10 块以 DMDLOAD_REQ 完成

- 5.3.3.11 DMDLOAD_REQ 建立时间要求

- 5.3.3.12 单通道传输模式

- 5.3.3.13 DMD 块阵列数据映射

- 5.3.3.14 Xilinx IBERT

- 5缩略语和首字母缩写词

- 6米6体育平台手机版_好二三四 (TI) 相关文档

摘要

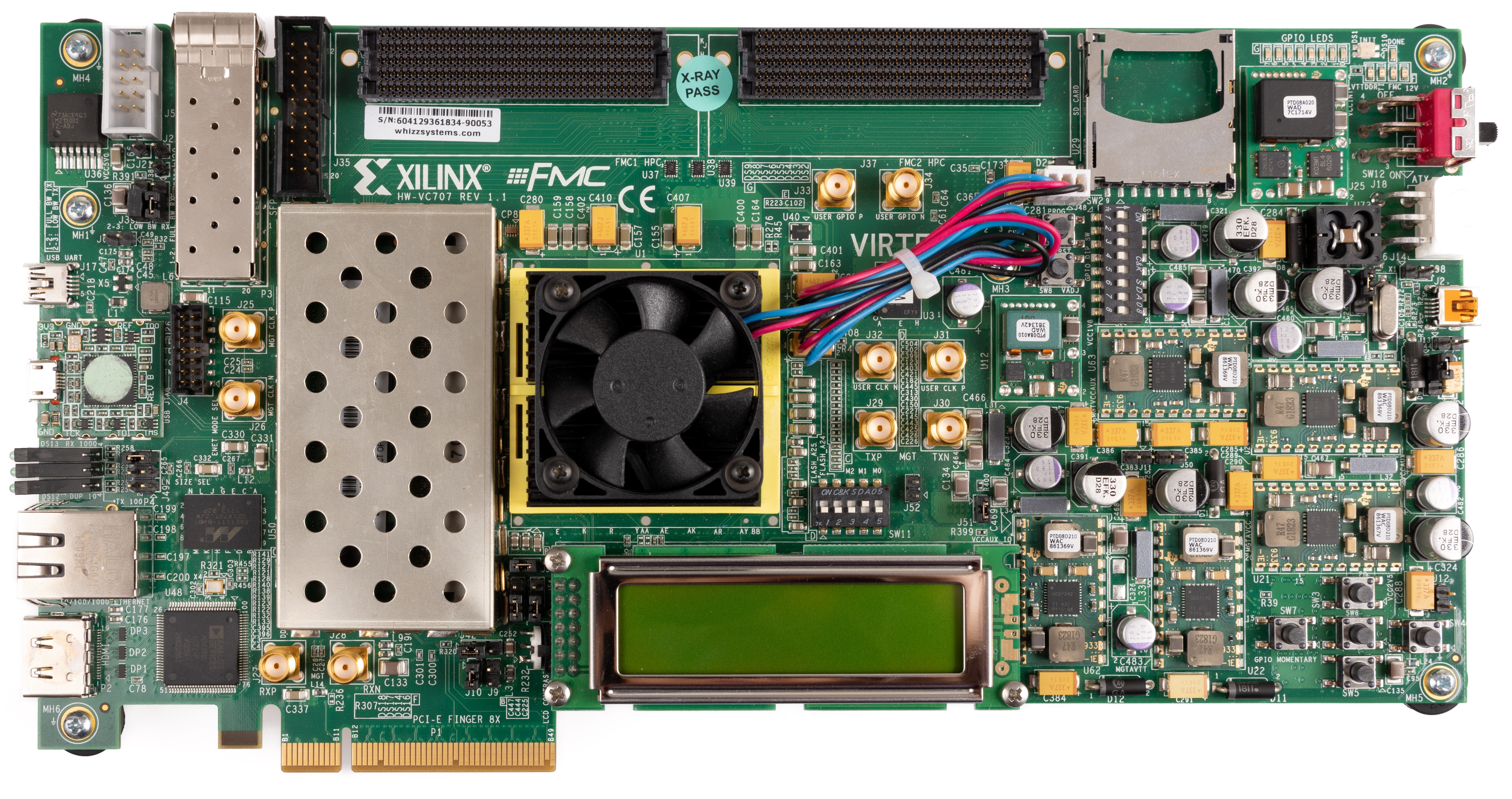

AMD Xilinx™ Virtex™-7 VC-707 Apps FPGA 旨在与 DLPC964 控制器和受支持的 DMD 配合使用。DLP® DLPC964 Apps FPGA 只是用于与 DLPLCRC964EVM 和 DLPLCR99EVM 连接的前端电路板的一个示例。DLPC964 Apps FPGA 用户指南将详细介绍 DLPC964 Applications FPGA (Apps FPGA) 的功能和寄存器以及所用的 VHDL 代码的组织结构。

图 1-1 AMD Xilinx Virtex-7 VC707 评估模块

图 1-1 AMD Xilinx Virtex-7 VC707 评估模块