ZHCUC02 May 2024 LMX1860-SEP

4.3 SYSREF 延迟发生器

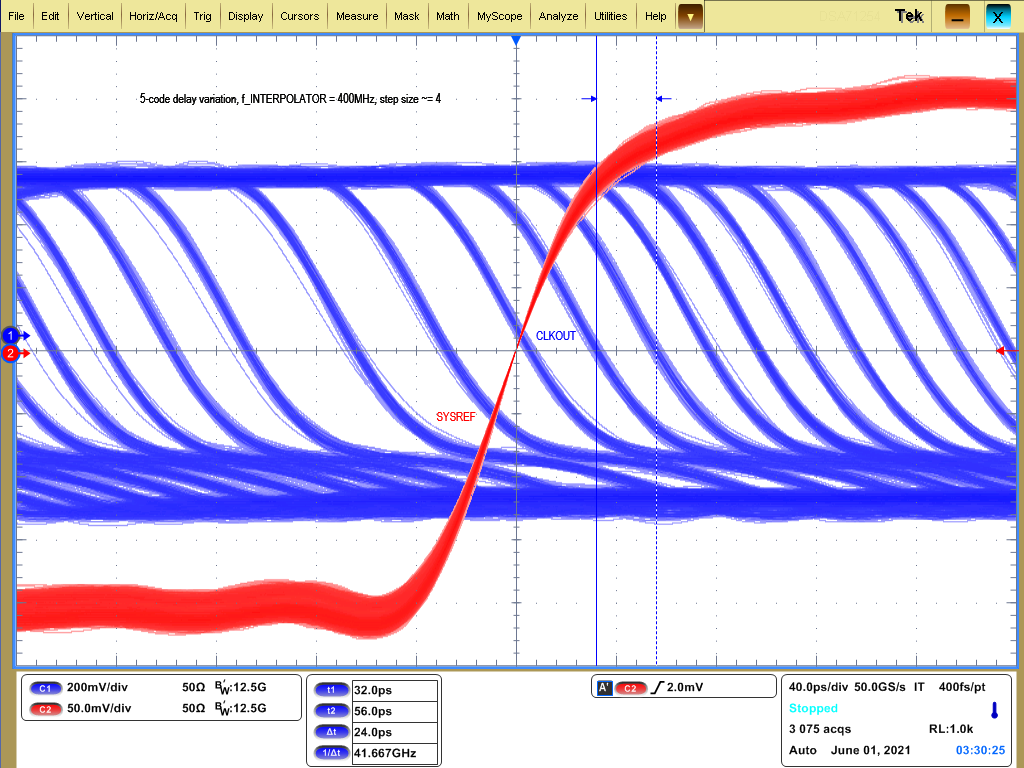

在发生器模式下,SYSREF 可按皮秒级步长延迟,以更接近地满足高频时钟输出的建立和保持要求。延迟分频器 SYSREF_DELAY_DIV 生成内插器频率 fINTERPOLATOR,通常在 400MHz 至 800MHz 范围内。该内插器频率进一步细分为 512 个延迟代码,在大部分 CLKIN 频率范围内允许大约 2.5ps 至 5ps 的延迟步长。

每个通道都有可输入的延迟代码。延迟代码算法记录在数据表中。为了简化延迟计算,GUI 提供了估计的相对延迟:输入相对延迟,GUI 会计算正确的步长值以尽可能实现所请求的延迟。或者,基于寄存器的延迟字段可以通过步进或编程来实现相同的结果。

图 4-6 SYSREF 5 代码步长延迟

图 4-6 SYSREF 5 代码步长延迟