ZHCUC02 May 2024 LMX1860-SEP

4.2 SYSREF 生成

SYSREF 生成电路包括 SYSREF 预分频器和后分频器、脉冲量可编程的脉冲发生器和中继器模式旁路。SYSREF 发生器模式将 SYSREF 信号重新定时到输出时钟,验证 SYSREF 输出是否接近具有默认延迟设置的时钟输出的下降沿。中继器模式时序仅由器件的传播延迟决定。

要激活 SYSREF 生成电路,必须满足以下条件:

- SYSREFREQ_MODE 字段必须设置为 SYSREF 模式。

- SYSREF_MODE 字段必须设置为适当的条件:连续、脉冲发生器或中继器。

- 在发生器模式(连续或脉冲发生器)下,必须验证 FINTERPOLATOR % FSYSREF = 0。

- 必须针对生成器或中继器模式正确配置 SYSREF_DELAY_BYP 字段(每当设置 SYSREF_MODE 时,GUI 自动设置条件通常会验证这一点)。

- SYSREFREQ_VCM 字段必须设置为直流耦合模式才能实现连续或脉冲发生器输出。在中继器模式输出中,SYSREF 输入可以是交流或直流耦合,并且必须相应地设置 SYSREFREQ_VCM。

- 对于连续模式,必须在 SYSREFREQ 引脚上连续看到高电平信号。对于脉冲发生器模式,必须在 SYSREFREQ 引脚上看到低电平到高电平的转换才能触发脉冲发生器。对于中继器模式,输出遵循输入状态。

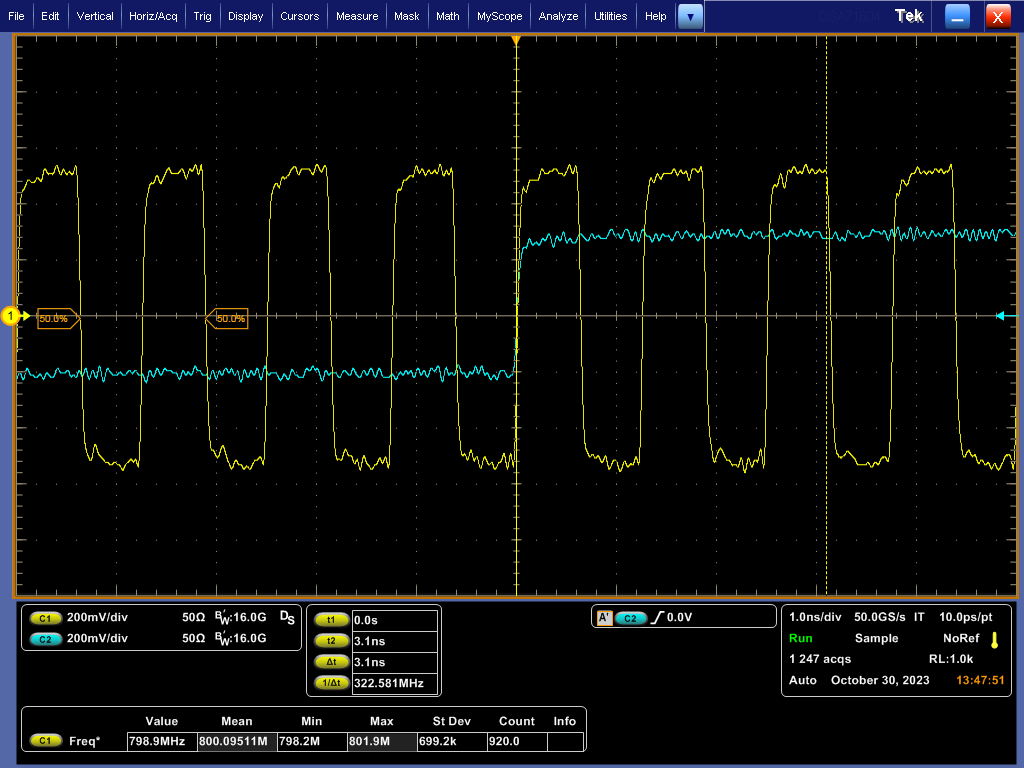

图 4-5 具有 10MHz SYSREF 的缓冲器模式

图 4-5 具有 10MHz SYSREF 的缓冲器模式