ZHCUC05A November 2022 – May 2024 AFE7900 , AFE7903 , AFE7906 , AFE7920 , AFE7921 , AFE7950

5 添加 Microblaze 和 SPI IP 以便在 Vitis 中用于嵌入式开发

- 打开现有的 Vivado 工程或创建新工程。

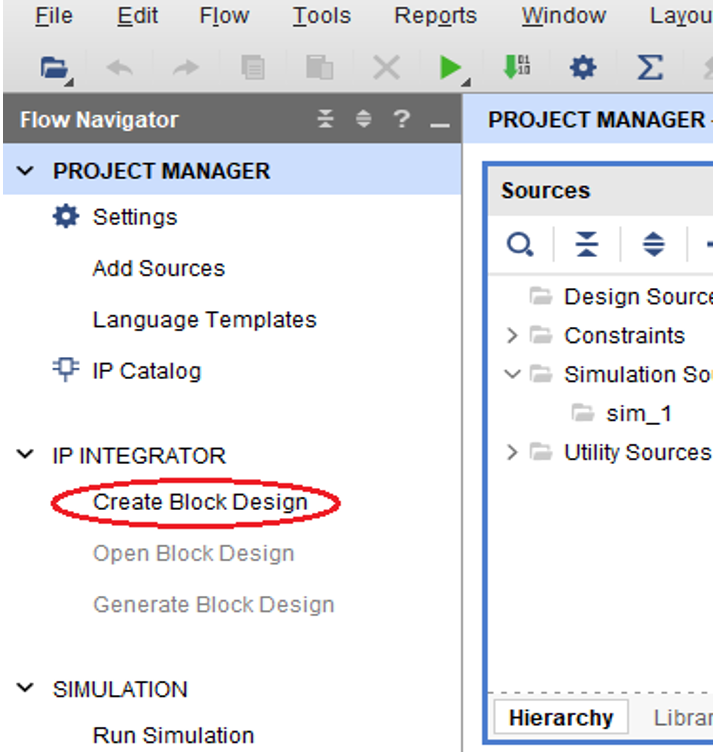

- 在左窗格中的“IP Integrator”下,点击“Create Block Design”。

图 5-1 创建块设计

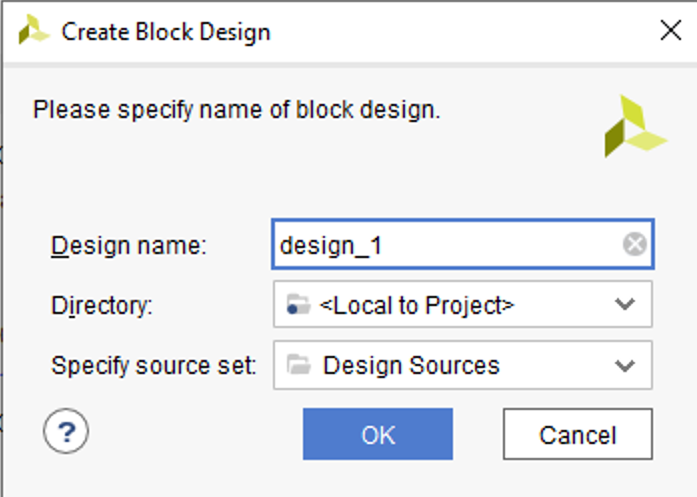

图 5-1 创建块设计 - 为块设计命名并点击“OK”。

图 5-2 命名块设计

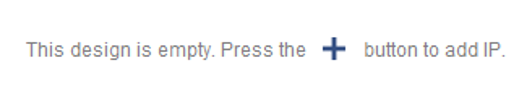

图 5-2 命名块设计 - 在新添加的块设计中,点击“+”以添加 IP。

图 5-3 向块设计中添加 IP

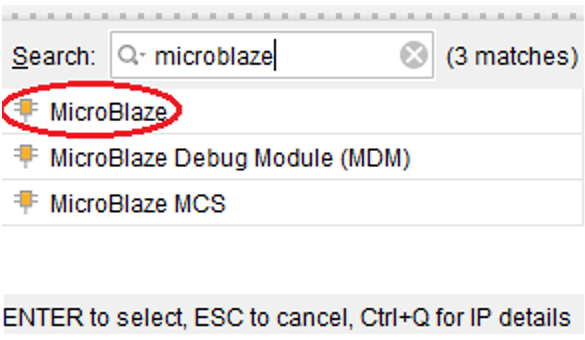

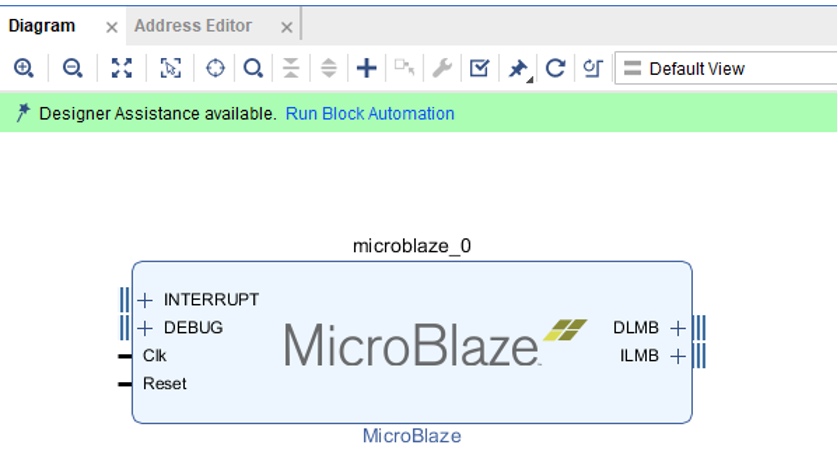

图 5-3 向块设计中添加 IP - 搜索 Microblaze 并将“Microblaze”添加到块设计。

图 5-4 向块设计中添加 Microblaze

图 5-4 向块设计中添加 Microblaze - 点击“Run Block automation”,然后点击“OK”。

图 5-5 为 Microblaze 运行块自动化

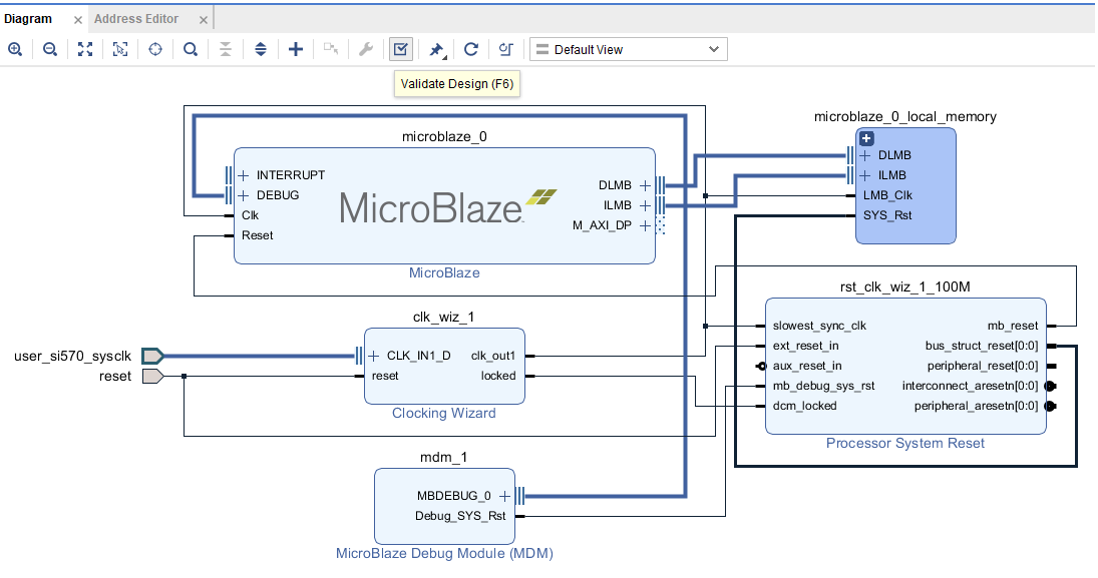

图 5-5 为 Microblaze 运行块自动化 - Vivado 会自动为 Microblaze 添加多个 IP 配套块。

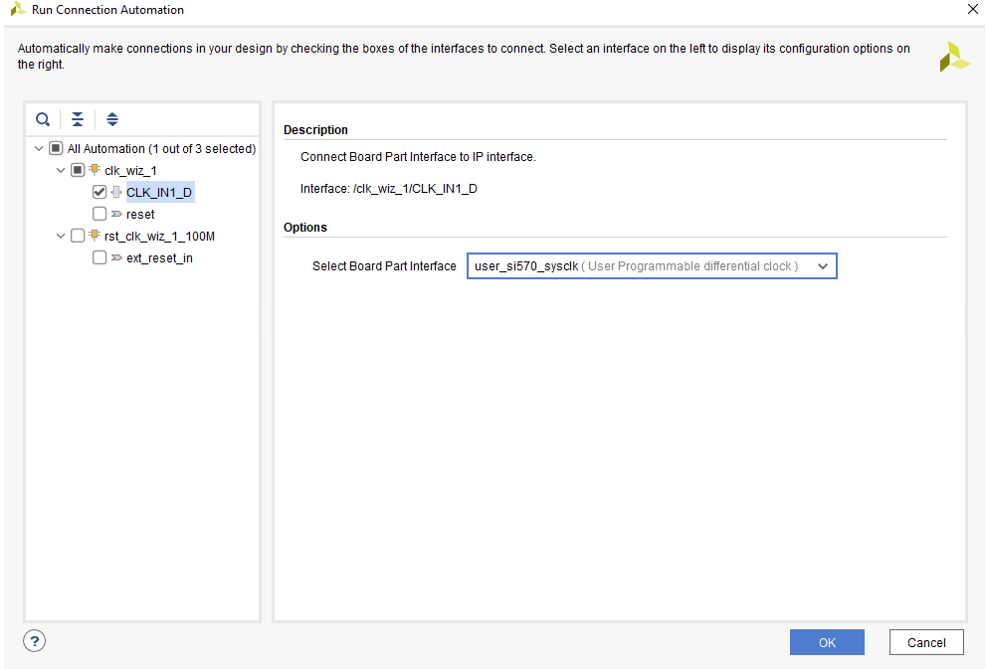

- 点击“Run Connection automation”。

- 在连接自动化弹出窗口中,选择“CLK_IN1_D”,将其映射到“user_si570_sysclk”,然后点击“OK”。

图 5-6 为 Microblaze 选择 CLKIN

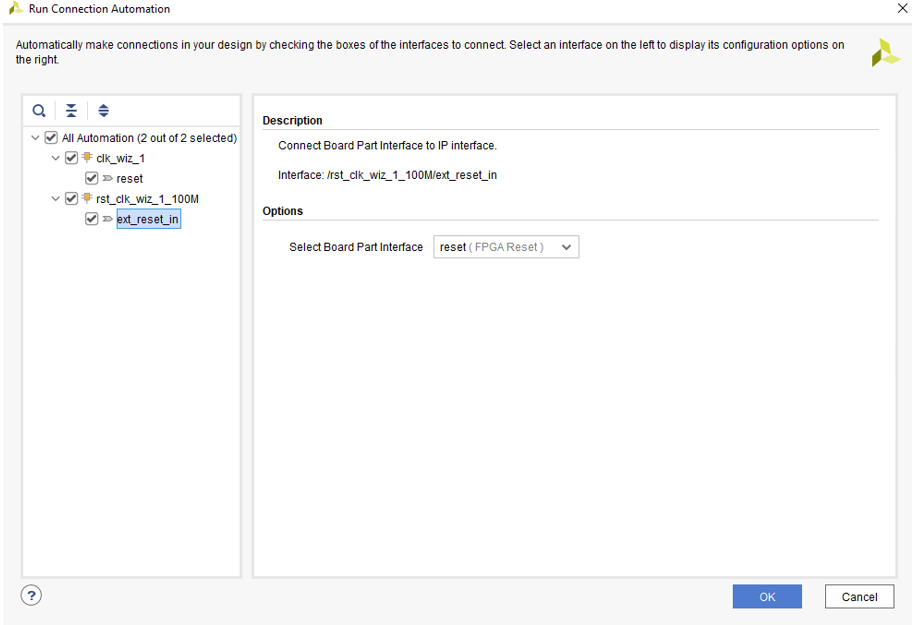

图 5-6 为 Microblaze 选择 CLKIN - 再次点击“Run Connection automation”。

- 在连接自动化弹出窗口中,选择“reset”、“ext_reset_in”,将其映射到“reset (FPGA_reset)”,然后点击“OK”。

图 5-7 为 Microblaze 复位连接

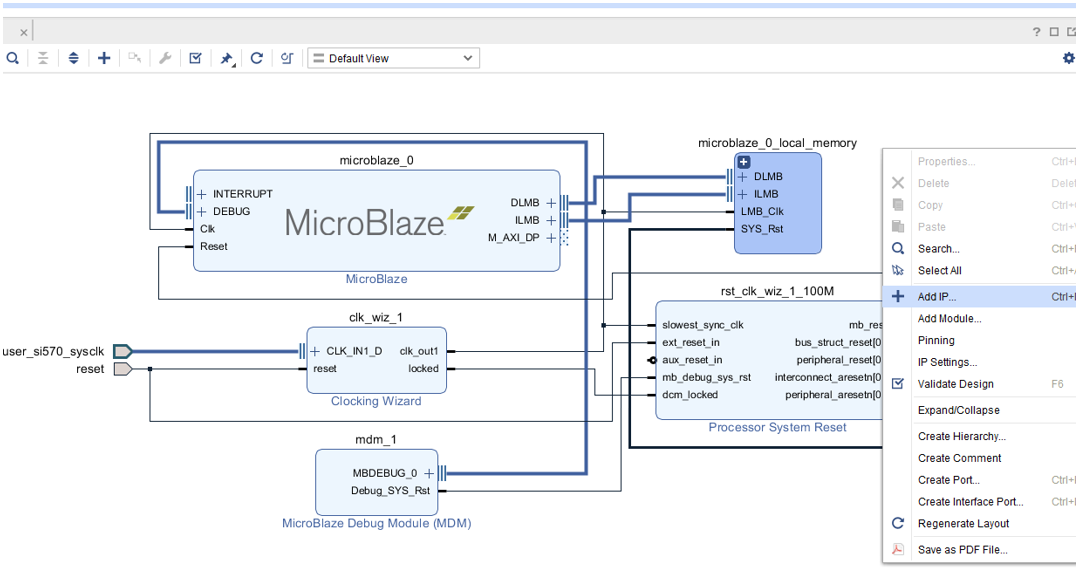

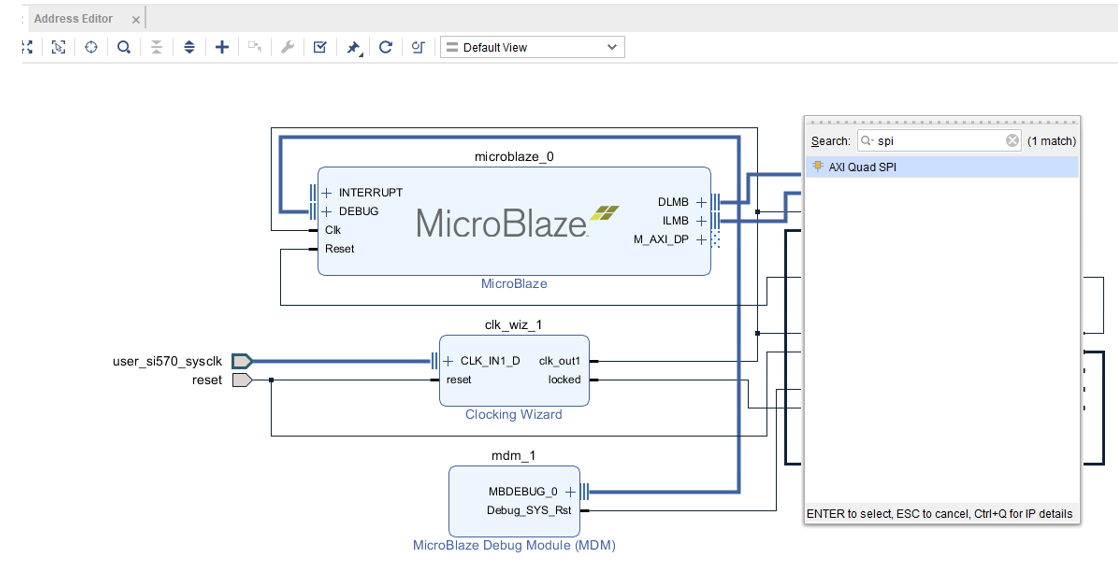

图 5-7 为 Microblaze 复位连接 - 右键点击框设计并添加“AXI Quad SPI”,如图 5-8 和图 5-9 所示。

图 5-8 向块设计中添加 IP

图 5-8 向块设计中添加 IP 图 5-9 将“AXI QUAD SPI”IP 添加到块设计中

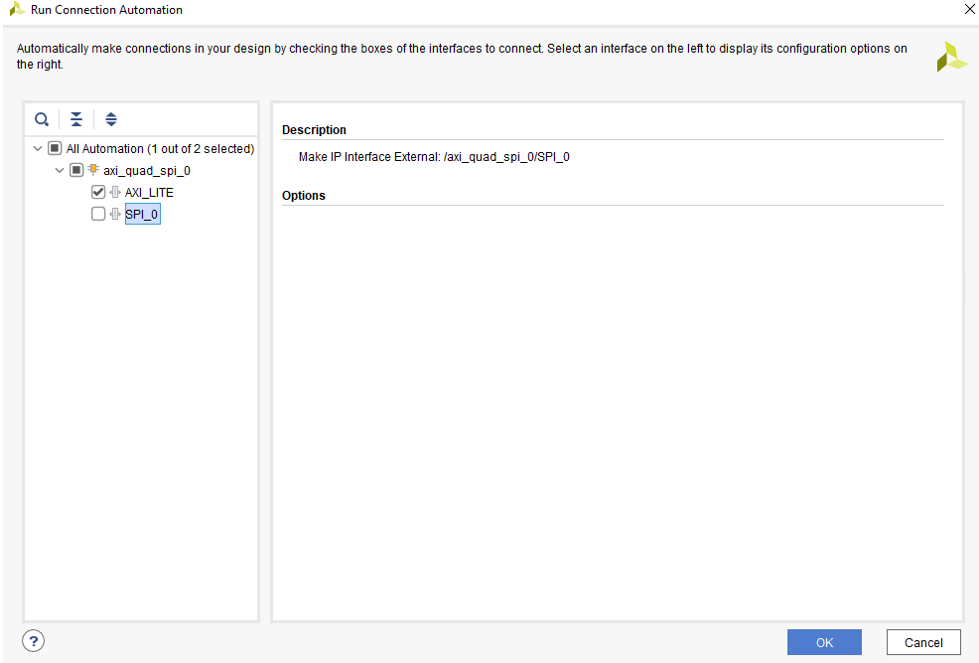

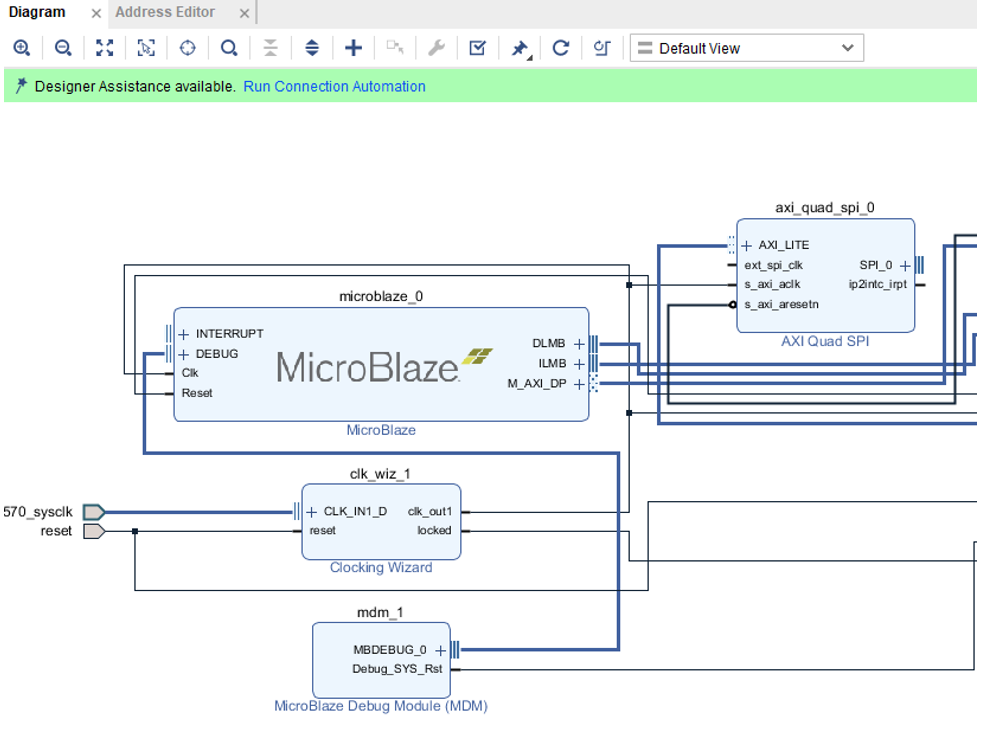

图 5-9 将“AXI QUAD SPI”IP 添加到块设计中 - 点击“Run Connection automation”。

图 5-10 针对“AXI_LITE”运行连接自动化

图 5-10 针对“AXI_LITE”运行连接自动化 - 选择“AXI_LITE”并点击“OK”。

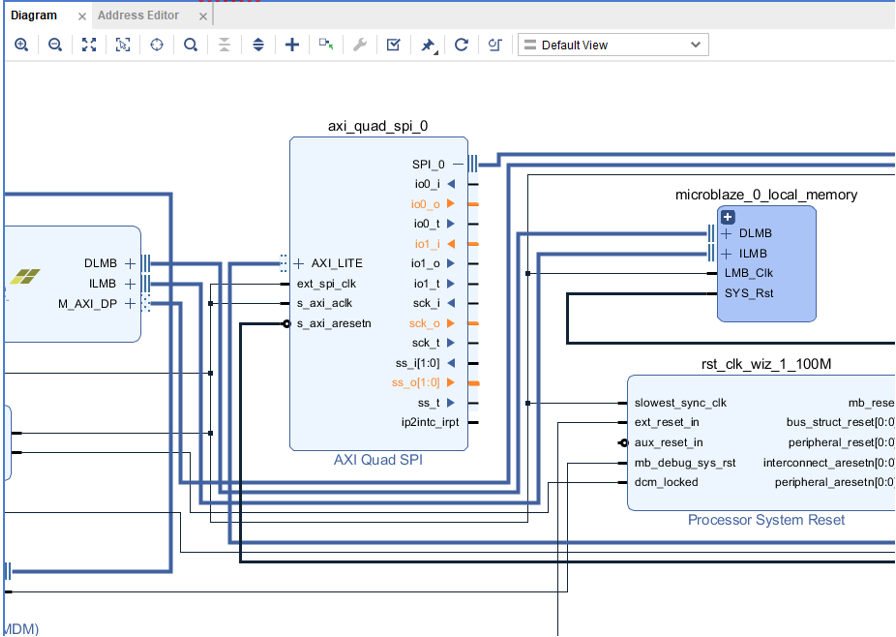

图 5-11 “ext_spi_clk”在“AXI QUAD SPI”中显示“No Connection”

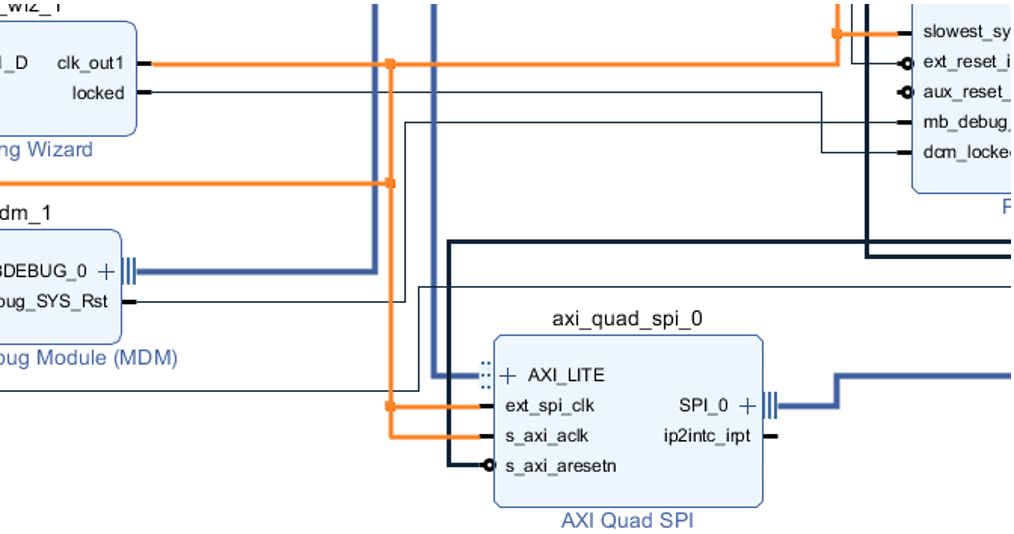

图 5-11 “ext_spi_clk”在“AXI QUAD SPI”中显示“No Connection” - 将“s_axi_aclk”连接到“ext_spi_clk”。

图 5-12 “ext_spi_clk”已连接到“s_axi_aclk”

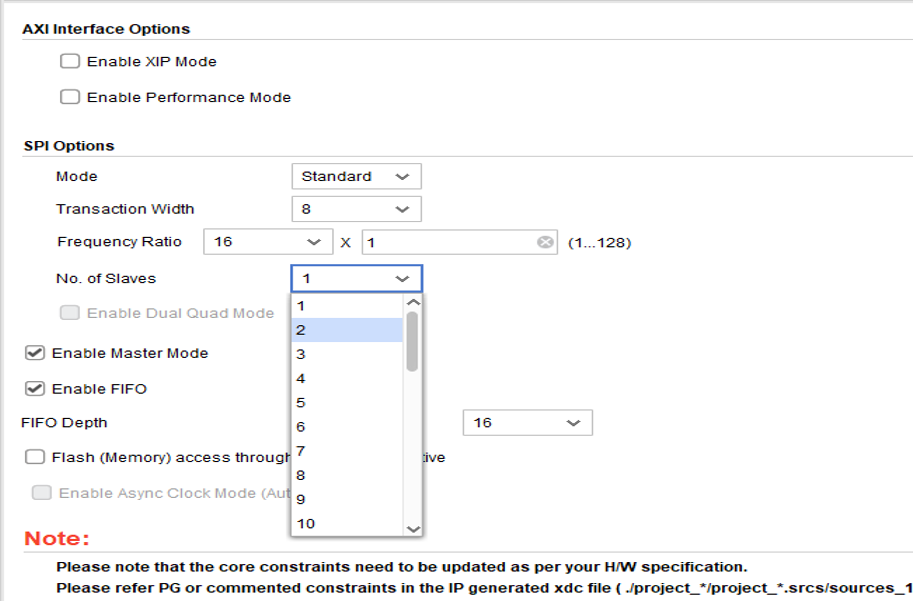

图 5-12 “ext_spi_clk”已连接到“s_axi_aclk” - 双击“AXI Quad SPI”->选择“No. of slaves”,然后点击“OK”。

图 5-13 选择 AXI QUAD SPI 中的 SPI 从站数量

图 5-13 选择 AXI QUAD SPI 中的 SPI 从站数量 - 从“Quad SPI IP”中,按以下方式映射信号:

- “io0_o”-> SPI_SDO

- “Io1_i”<- SPI_SDI

- “sck_o”-> SPI_SCL

- ss_o[1:0] -> SPI_SEN0、SPI_SEN1

- 系统将根据在步骤 16 中选择的从站数量计算“ss_o”位宽

图 5-14 在“AXI QUAD SPI”中突出显示用于外部连接的端口

图 5-14 在“AXI QUAD SPI”中突出显示用于外部连接的端口 - 验证设计以确保未出现如图 5-15 所示的错误。

图 5-15 验证块设计

图 5-15 验证块设计 - 要添加 GPIO,请从目录中添加“AXI GPIO”,并重复上述类似步骤。