ZHCUC31 May 2024

2.1 接头和测试点信息

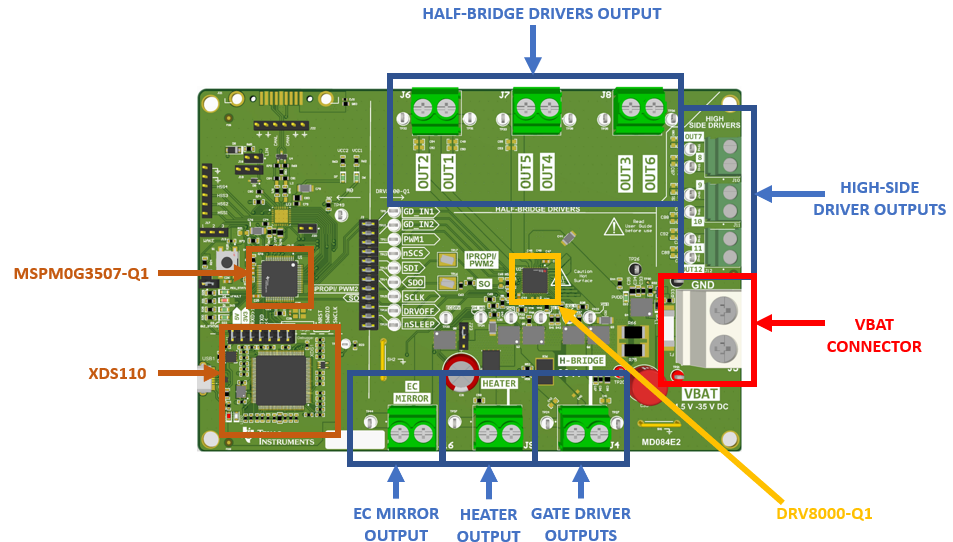

图 2-1 DRV8000-Q1EVM (MD084-001)(顶视图)

图 2-1 DRV8000-Q1EVM (MD084-001)(顶视图)警告: 表面高温。EVM 可能会用 FIRE 三角符号标记高表面温度。驱动高电流时,避免触摸标记的高温表面区域,以防止潜在的灼伤损害。

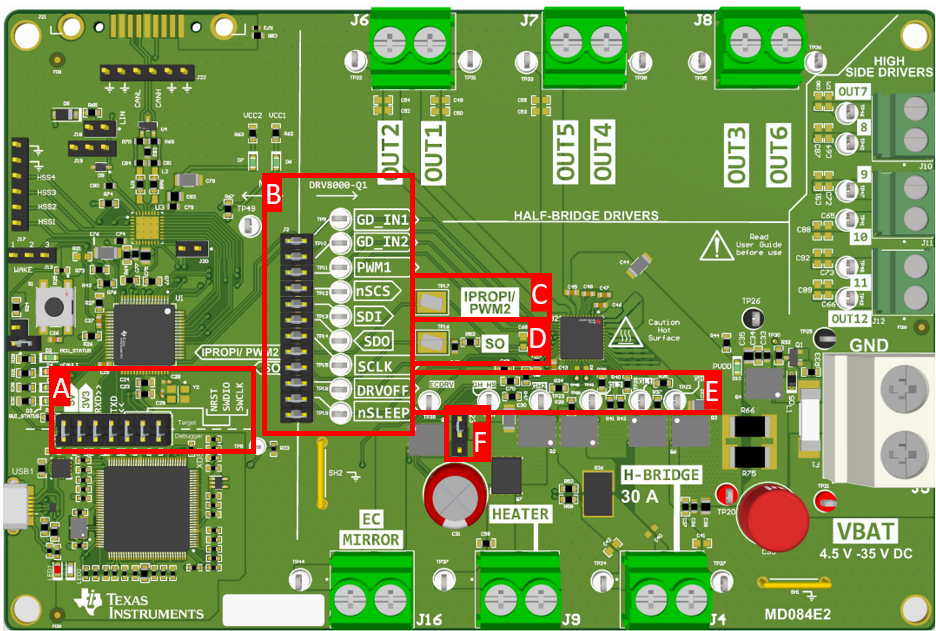

图 2-2 DRV8000-Q1EVM 接头和测试点信息

图 2-2 DRV8000-Q1EVM 接头和测试点信息表 2-1 接头和测试点说明 - DRV8000-Q1EVM

| 元件标签 | 说明 |

|---|---|

| Aee | MSP432E401Y 和 MSPM0G3507 之间的 XDS110 接头。 |

| B |

主信号接头:

|

| C |

IPROPI/PWM2 - 检测输出从任何驱动器负载电流反馈、PVDD 电压反馈或热仪表组温度反馈进行多路复用。也可针对半桥驱动器配置为第二个 PWM 引脚输入。 |

| D | SO - 分流放大器输出。 |

| E |

栅极驱动器、EC 驱动器、加热器测试点(左至右):

|

| F | 外部 EC 电压调节 FET 的漏极(从上到下):

|