ZHCUCH6A August 2024 – November 2024 F29H850TU , F29H859TU-Q1

5.1.2 MCU144E1 已知硬件问题

当 S3 和 S4 都设置为内部 VREF 模式时,ADC VREFHIAB 和 VREFHICDE 错误地短接在一起

开关 S3 和 S4 用于为 F29H85x 微控制器的 VREFHIAB 和 VREFHICDE 引脚指定 VREF 模式。

当在 S3 和 S4 上选择了内部 VREF 模式时,VREFHIAB 和 VREFHICDE 引脚会错误地短接在一起。有关 S3 和 S4 的更多信息,请参阅节 2.4.2。

需要修改硬件才能解决该问题:

- 设置 S3/S4 以实现外部模式

- 移除 R53/C79

- 移除 R57/C95

做出此更改后,电路板不会在 VREFHI 引脚上驱动任何电压。ADC 可用于内部 VREF 模式。

选择外部 VREF 模式时,VREFHIAB 和 VREFHICDE 引脚上的电压不正确

开关 S3 和 S4 用于为 F29H85x 微控制器的 VREFHIAB 和 VREFHICDE 引脚选择 VREF 模式。

选择外部 VREF 模式时,会观察到 VREFHIAB 和 VREFHICDE 上的电压不正确。

需要修改硬件才能解决该问题:

- 将电路板上的 R53 和 R57 替换为 0 欧姆电阻器。

- 移除 C78、C79、C94 和 C95

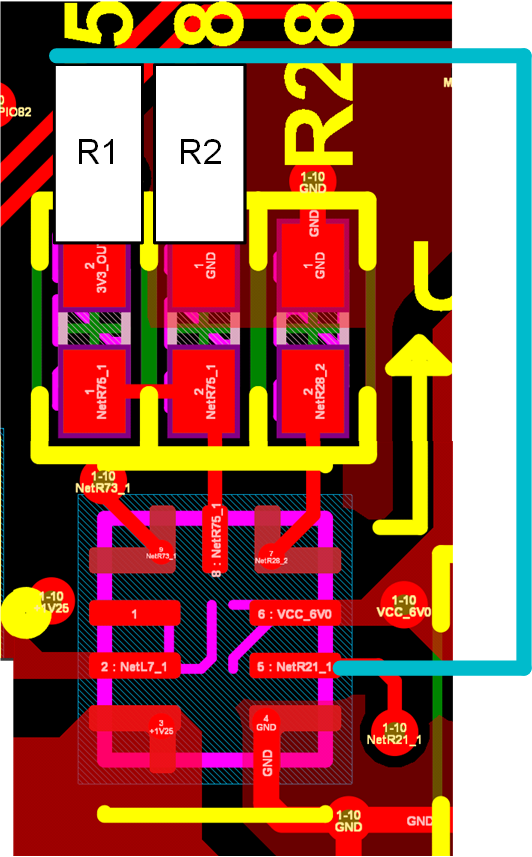

图 5-1 修改 ADC VREF 时的元件位置

图 5-1 修改 ADC VREF 时的元件位置有关 S3 和 S4 的更多信息,请参阅节 2.4.2。

VDD 和 VDDIO/VDDA MCU 电源轨的上电顺序不正确

F29H85x 和 F29P58x 实时微控制器 数据表规定 VDD 电源轨应在 VDDIO/VDDA 电源轨加电后加电。

通电源管理 IC (PMIC) 被编程为同时启动 VDD 和 VDDIO/VDD 电源轨。该错误的电源顺序可能会导致 MCU XRSn 引脚在某些 EVM 上在加电后被置为有效。在这些电路板上,Code Compose Studio 无法连接至 MCU。

需要按如下所示修改硬件才能解决该问题。

- 拆下 R22、R75、R78

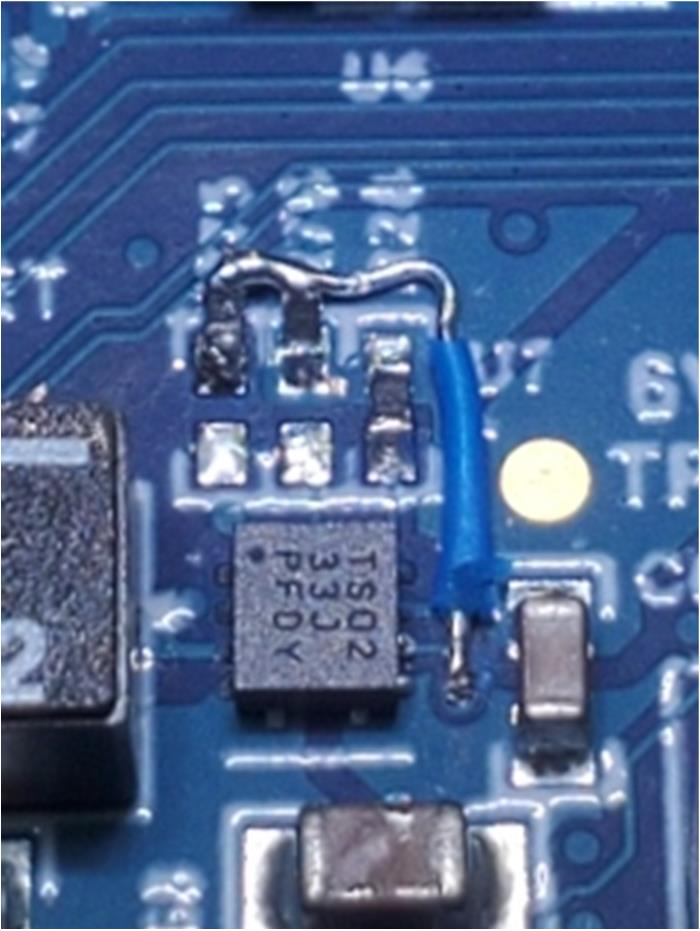

- 如图所示,添加 R1 和 R2

- R1 = 10.7K (1%),R2 = 5760 (1%)

- 如图所示,在 R1、R2 和 U7.5 之间添加蓝色导线

图 5-2 针对上电的硬件修改公告

图 5-2 针对上电的硬件修改公告 图 5-3 针对上电完成的修改公告

图 5-3 针对上电完成的修改公告已在所有 MCU144E1-002 组件上实施该硬件修改。

数据记录和跟踪连接器 (J5) 上的 FSI 信号可能会干扰某些高级调试器

数据记录和跟踪 (DLT) 接头 (J5) 包含各种用于数据记录的 FSI 信号。

J5 上这些 FSI 信号的位置可能会干扰 XDS560v2 等一些高级调试器。

默认情况下,FSI 信号未连接至 DLT 接头 (J5)。需要修改电阻器才能将 FSI 信号连接到 DLT 接头。

有关 DLT 接头的 FSI 信号支持的更多信息,请参阅节 2.4.4。