ZHCUCI3 November 2024 LMX2624-SP

4.2.3.1 SYSREF 时钟生成

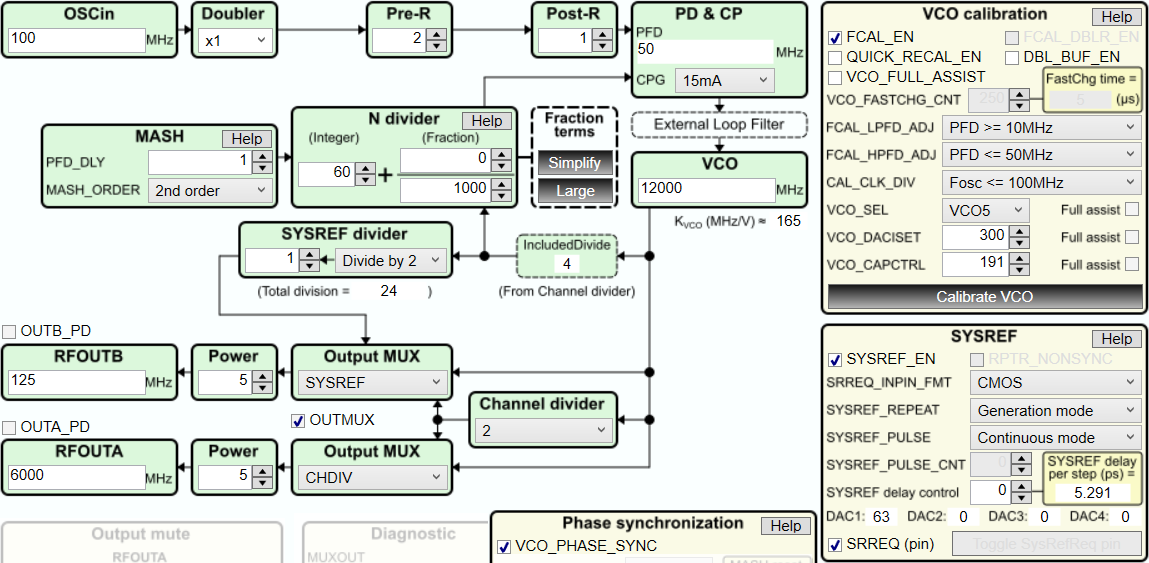

要启用 SYSREF 功能,请设置 SYSREF_EN = 1。SYSREF 运行需要一些相位同步构建块,因此也必须将 VCO_PHASE_SYNC 设置为 1。设置该位后,相位检测器频率必须等于或小于 50MHz。将 Output MUX 设置为 SYSREF,使 RFOUTB 输出为 SYSREF 时钟。要生成连续 SYSREF 时钟,请设置 SYSREF_REPEAT = Generation mode;设置 SYSREF_PULSE = Continuous mode。在 SysRefReq 引脚被拉高后,RFOUTB 将在 20ns 内输出时钟。这可以通过选中 SRREQ (pin) 复选框来实现。使用 SYSREF divider 来调整输出 SYSREF 时钟频率。

图 4-20 SYSREF 连续时钟生成

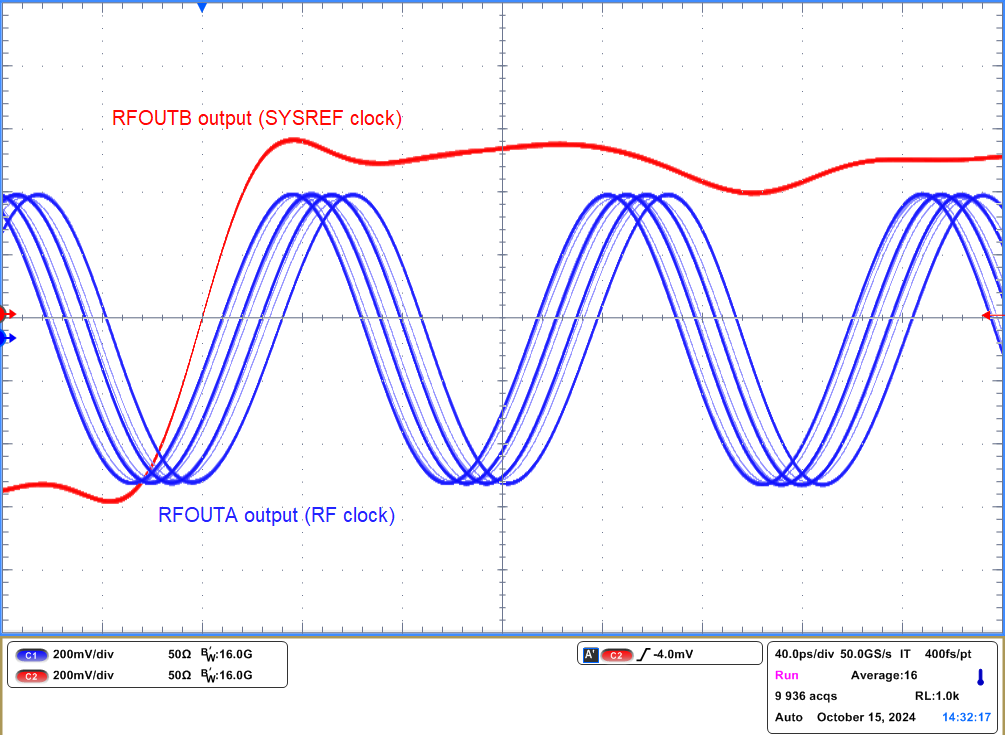

图 4-20 SYSREF 连续时钟生成 图 4-21 连续 SYSREF 时钟生成

图 4-21 连续 SYSREF 时钟生成 图 4-22 SYSREF 延迟

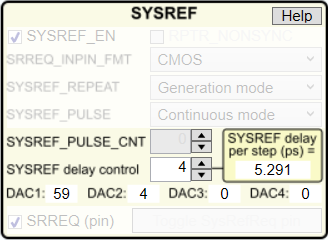

图 4-22 SYSREF 延迟SYSREF 时钟 (RFOUTB) 和射频时钟 (RFOUTA) 之间的相位可以使用寄存器 JESD_DACx 进行调整。

图 4-23 SYSREF 延迟控制

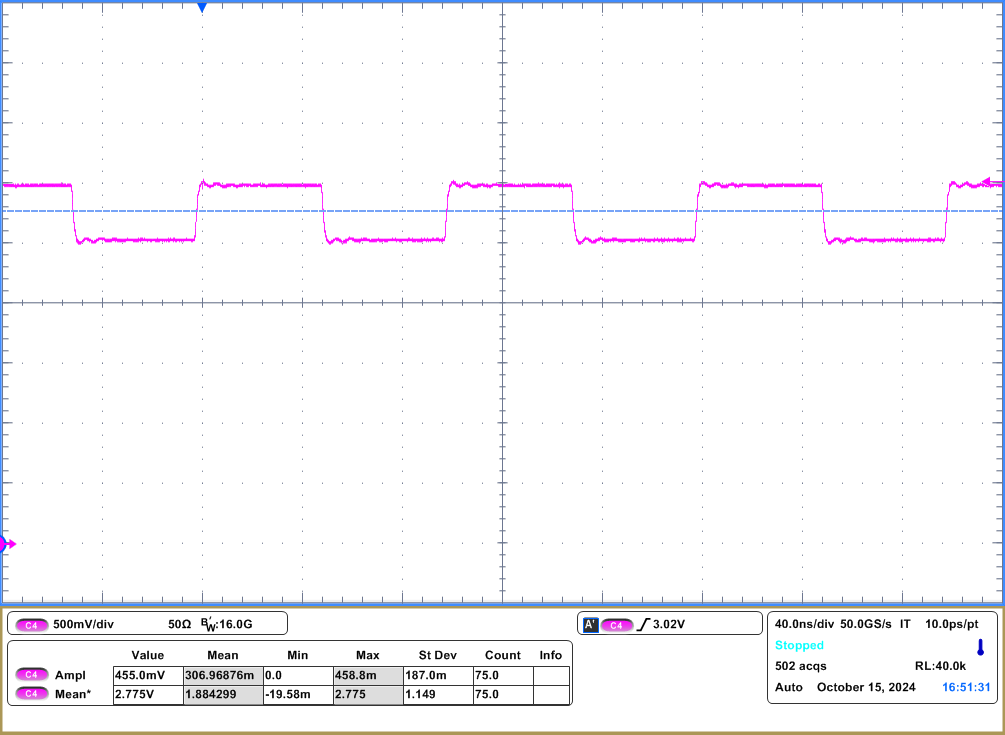

图 4-23 SYSREF 延迟控制如果需要对 SYSREF 时钟进行直流耦合,则必须注意输出共模电压,该电压不是恒定值,而是随输出电压摆幅设置而变化。将 Power 设置为不同的值会更改 SYSREF 时钟输出电压摆幅以及共模电压。

图 4-24 Power = 2 时的 SYSREF 输出

图 4-24 Power = 2 时的 SYSREF 输出 图 4-25 Power = 7 时的 SYSREF 输出

图 4-25 Power = 7 时的 SYSREF 输出