ZHCUCI3 November 2024 LMX2624-SP

4.2.6 引脚模式

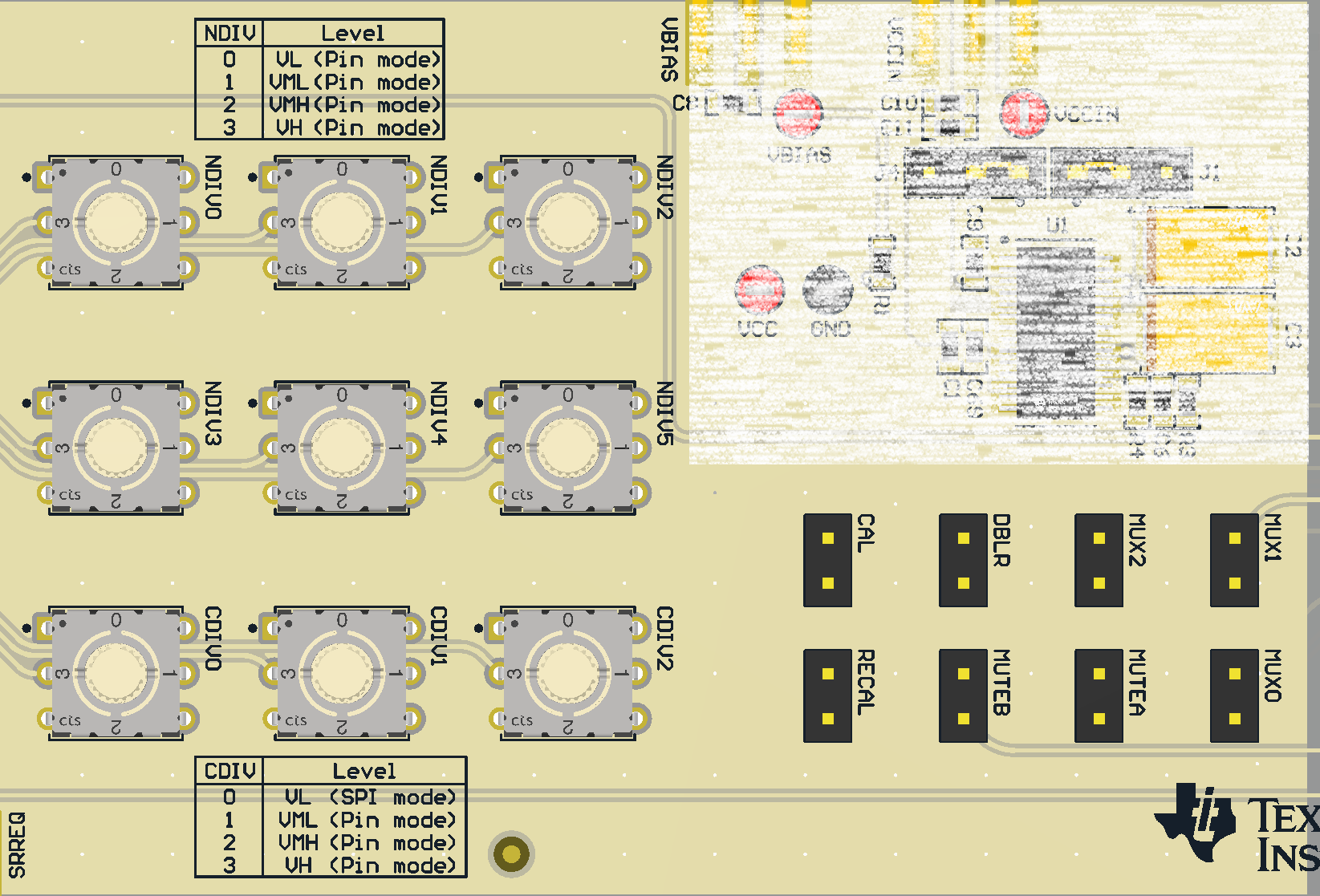

LMX2624-SP 支持引脚配置操作,无需寄存器编程。引脚模式操作的设置与图 2-1 中所示的图相同,只是不需要连接到 PC。在 EVM 中,LMX2624-SP 的配置由旋转 DIP 开关和 2 引脚接头决定。

图 4-40 引脚控制元件

图 4-40 引脚控制元件N 分频器值由 NDIVx 旋转 DIP 开关进行配置,CDIVx 旋转 DIP 开关用于设置通道分频器值。NDIVx 和 CDIVx 引脚是 4 电平输入引脚。旋转 DIP 开关的位置(0、1、2 或 3)将引脚设置为以下电平之一:VL (0V);VML;VMH 和 VH (3.3V)。

表 4-1 CDIVx 通道分频器真值表

| CDIV2 | CDIV1 | CDIV0 | 分频器值 |

|---|---|---|---|

| 0 | 0 | 0 | SPI 模式 |

| 0 | 1 | 0 | 2 |

| 0 | 2 | 0 | 4 |

| 0 | 2 | 3 | 6 |

| 1 | 0 | 0 | 8 |

| 1 | 0 | 3 | 12 |

| 1 | 1 | 0 | 16 |

| 1 | 1 | 3 | 24 |

| 1 | 2 | 0 | 32 |

| 1 | 2 | 3 | 48 |

| 1 | 3 | 0 | 64 |

| 1 | 3 | 3 | 96 |

| 2 | 0 | 0 | 128 |

| 2 | 0 | 3 | 192 |

| 2 | 1 | 0 | 256 |

| 2 | 1 | 3 | 384 |

| 2 | 2 | 0 | 512 |

| 2 | 2 | 3 | 768 |

| 2 | 3 | 0 | 1024 |

| 2 | 3 | 3 | 1536 |

表 4-2 NDIVx N 分频器真值表

| 十进制 | NDIV5 | NDIV4 | NDIV3 | NDIV2 | NDIV1 | NDIV0 |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 0 | 0 | 0 | 2 |

| 3 | 0 | 0 | 0 | 0 | 0 | 3 |

| 4 | 0 | 0 | 0 | 0 | 1 | 0 |

| 5 | 0 | 0 | 0 | 0 | 1 | 1 |

| 6 | 0 | 0 | 0 | 0 | 1 | 2 |

| 7 | 0 | 0 | 0 | 0 | 1 | 3 |

| 8 | 0 | 0 | 0 | 0 | 2 | 0 |

| ... | ... | ... | ... | |||

| 59 | 0 | 0 | 0 | 3 | 2 | 3 |

| 60 | 0 | 0 | 0 | 3 | 3 | 0 |

| 61 | 0 | 0 | 0 | 3 | 3 | 1 |

| 62 | 0 | 0 | 0 | 3 | 3 | 2 |

| ... | ... | ... | ... | |||

| 4092 | 3 | 3 | 3 | 3 | 3 | 0 |

| 4093 | 3 | 3 | 3 | 3 | 3 | 1 |

| 4094 | 3 | 3 | 3 | 3 | 3 | 2 |

| 4095 | 3 | 3 | 3 | 3 | 3 | 3 |

2 引脚接头 MUX0、MUX1 和 MUX2 确定 RFOUTA 和 RFOUTB 输出。

表 4-3 输出多路复用器设置

其他 2 引脚接头的定义如下:| MUX2 | MUX1 | MUX0 | RFOUTA | RFOUTB |

|---|---|---|---|---|

| 0 | 0 | 0 | 通道分频器 | 通道分频器 |

| 0 | 0 | 1 | 通道分频器 | VCO |

| 0 | 1 | 0 | VCO | 通道分频器 |

| 0 | 1 | 1 | VCO | VCO |

| 1 | 0 | 0 | 倍频器 | 通道分频器 |

| 1 | 0 | 1 | VCO | 倍频器 |

| 1 | 1 | 0 | 倍频器 | VCO |

| 1 | 1 | 1 | 倍频器 | 倍频器 |

表 4-4 2 引脚接头定义

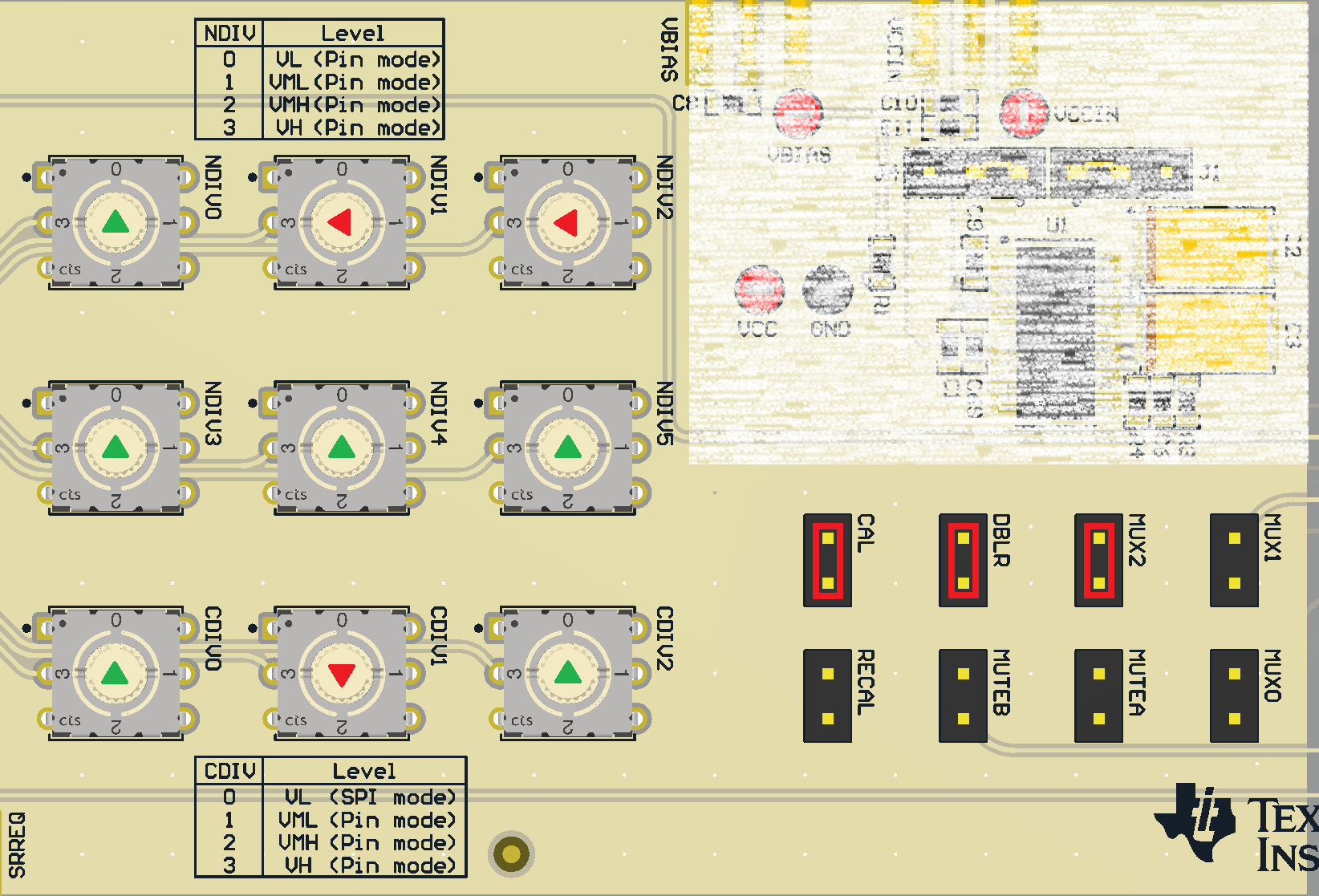

例如,要在引脚模式下针对以下配置来配置 LMX2624-SP:

| 位号 | 功能 |

|---|---|

| MUTEA、MUTEB | 输出静音控制。 |

| RECAL | 如果 RECAL 为高电平,则当器件失去锁定时,器件会自动重新校准以重新增益锁定。EVM 默认将此引脚连接至高电平。 |

| DBLR | 启用 OSCin 倍频器。 |

| CAL | 连接高电平可启用该器件。低电平到高电平转换会触发 VCO 校准。 |

- fOSC = 100MHz;fPD = 200MHz;fVCO = 12GHz

- RFOUTA = 24GHz 输出;RFOUTB = 3GHz

硬件配置为:

- N 分频器 = 12G / 200M = 60 → NDIV[5:0] = (000330)4

- RFOUTA = 24GHz 且 RFOUTB = 3GHz → MUX[2:0] = (100)2

- 通道分频器 = 12G / 3G = 4 → CDIV[2:0] = (020)4

- fPD = 200MHz → DBLR = HIGH

图 4-41 引脚模式硬件配置

图 4-41 引脚模式硬件配置