ISO7821LLS

ZHCSFH5A - MARCH 2016-REVISED SEPTEMBER 2016

# ISO7821LLS 高性能 8000 V<sub>PK</sub> 增强型隔离式双 LVDS 缓冲器

# 1 特性

- 符合 TIA/EIA-644-A LVDS 标准

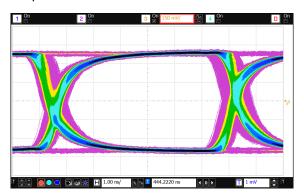

- 信号传输速率: 50Mbps 至 150Mbps

- 针对直流均衡数据进行了优化

- 宽电源电压范围: 3V 至 5.5V

- 宽温度范围: -55℃ 至 125℃

- 低功耗: 电流典型值为 10.3mA/通道(150Mbps 时)

- 低传播延迟: 17ns (典型值)

- 行业领先的 CMTI(最小值): ±100kV/μs

- 优异的电磁兼容性 (EMC)

- 系统级静电放电 (ESD)、瞬态放电 (EFT) 以及抗浪 涌保护

- 低辐射

- 隔离栅寿命: > 40 年

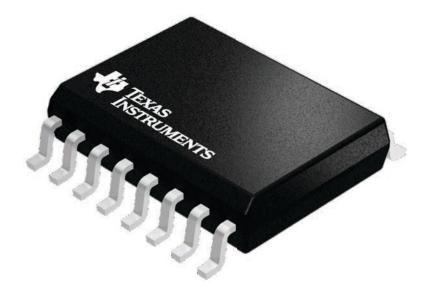

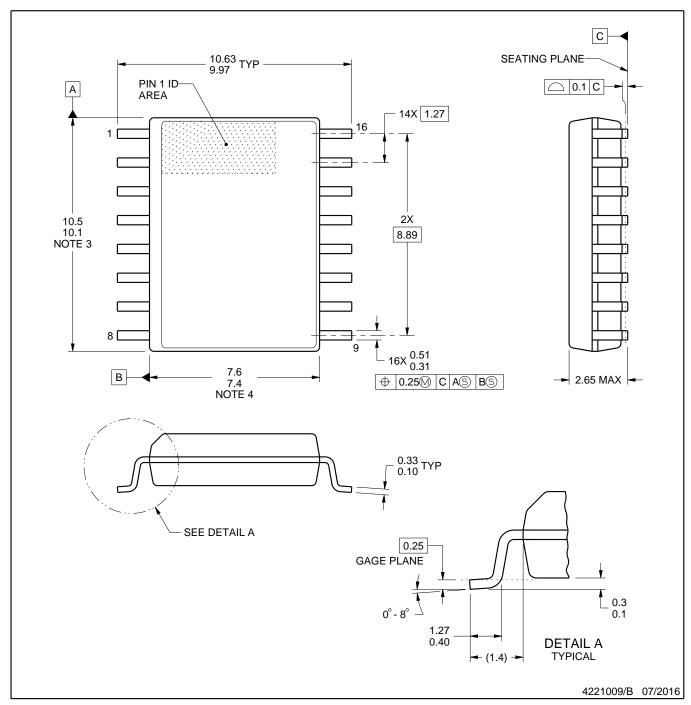

- SOIC-16 宽体 (DW) 和超宽体 (DWW) 封装选项

- 可承受的隔离浪涌电压高达 12800 VPK

- 安全相关认证:

- 符合 DIN V VDE V 0884-10 (VDE V 0884-10):

2006-12 标准的 8000 V<sub>PK</sub> 增强型隔离

- 符合 UL 1577 标准且长达 1 分钟的 5700 V<sub>RMS</sub>

隔离

- CSA 组件验收通知 5A, IEC 60950-1 和 IEC 60601-1 终端设备标准

- 符合 EN 61010-1 和 EN 60950-1 标准的 TUV 认证

- 符合 GB4943.1-2011 标准的 CQC 认证

- 已通过所有认证

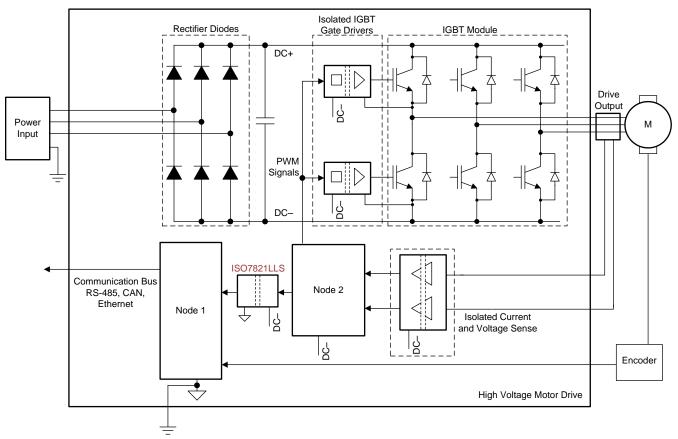

## 2 应用

- 电机控制

- 测试和测量

- 工业自动化

- 医疗设备

- 通信系统

# 3 说明

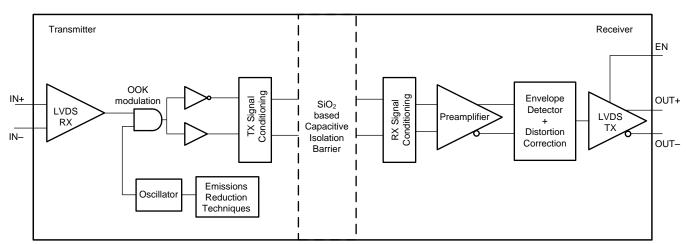

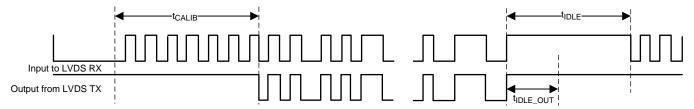

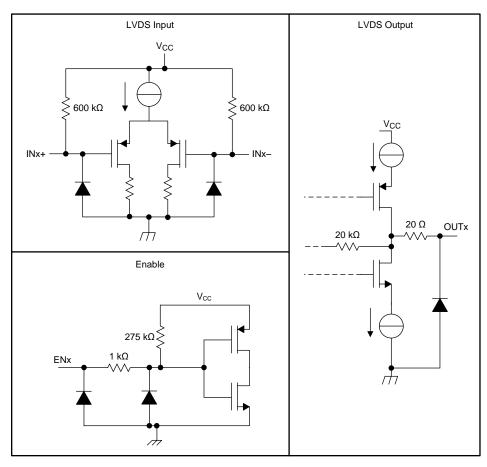

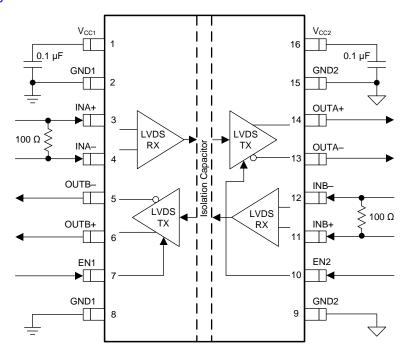

ISO7821LLS 器件是一款高性能、隔离式双 LVDS 缓冲器,隔离电压为 8000 V<sub>PK</sub>。在隔离 LVDS 总线信号时,该器件可提供高电磁抗扰度,辐射较低,并且具有低功耗特性。各隔离通道具有一个 LVDS 接收和传输缓冲器。ISO7821LLS 器件的定时性能针对与通信系统结合使用进行了优化。通信采用通过内部失真校正方案实现的直流均衡数据流。

ISO7821LLS 器件有一条正向通道和一条反向通道。

凭借创新的芯片设计和布线技术,ISO7821LLS 器件的电磁兼容性得到了显著增强,从而可确保提供系统级ESD、EFT 和浪涌保护并符合辐射标准。

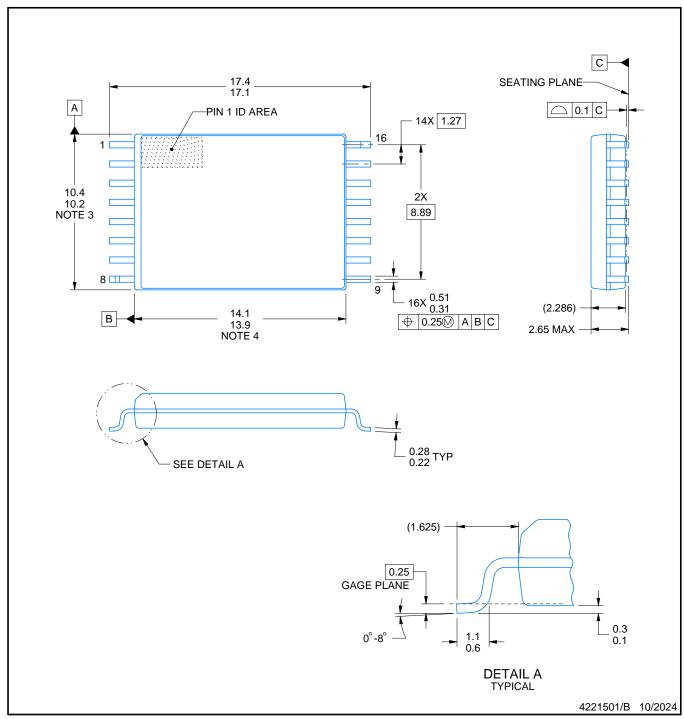

ISO7821LLS 器件采用 16 引脚小外形尺寸集成电路 (SOIC) 宽体 (DW) 和超宽体 (DWW) 封装。

器件信息(1)

| 器件型号        | 封装 封装尺寸(标称值) |                   |

|-------------|--------------|-------------------|

| 100702411.0 | DW (16)      | 10.30mm x 7.50mm  |

| ISO7821LLS  | DWW (16)     | 10.30mm x 14.00mm |

(1) 要了解所有可用封装,请参见数据表末尾的可订购产品附录。

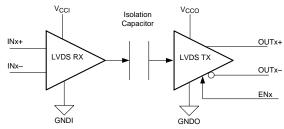

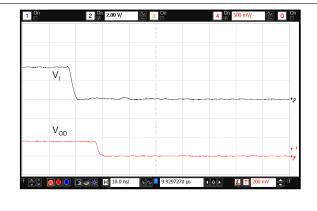

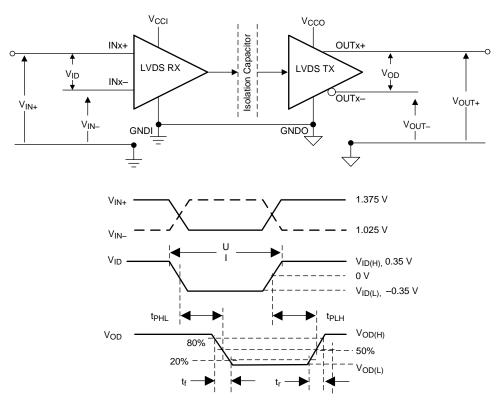

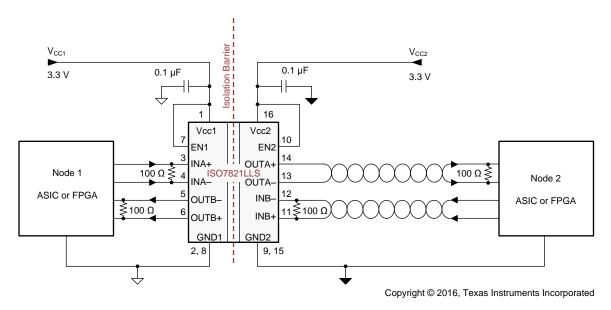

#### 简化电路原理图

Copyright © 2016, Texas Instruments Incorporated

V<sub>CCI</sub> 和 GNDI 分别是输入通道的电源和接地连接。 V<sub>CCO</sub> 和 GNDO 分别是输出通道的电源和接地连接。

| 目 | 录 |

|---|---|

|   |   |

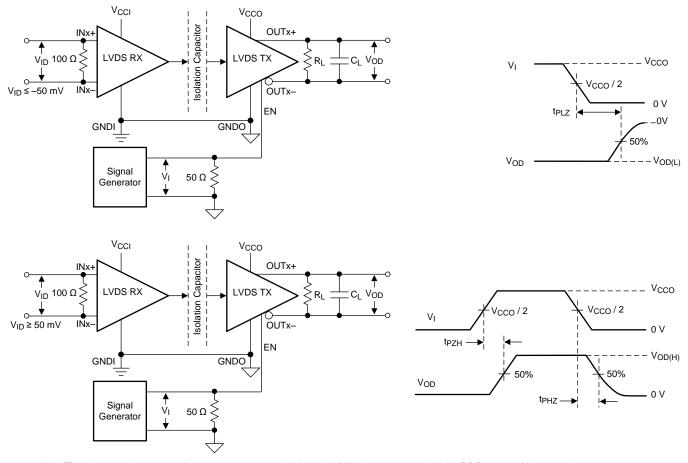

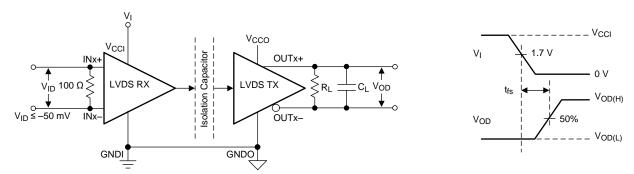

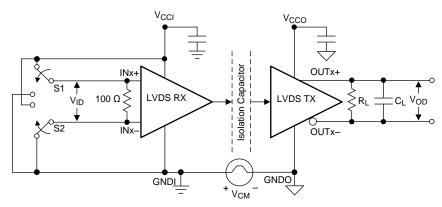

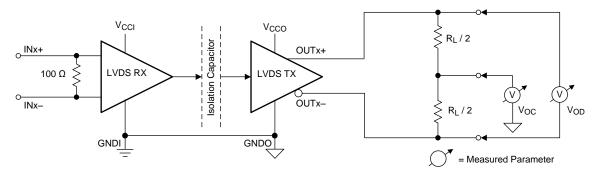

| 1 | 特性1                                                | 7  | Parameter Measurement Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14 |

|---|----------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | 应用 1                                               | 8  | Detailed Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17 |

| 3 | 说明 1                                               |    | 8.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 4 | 修订历史记录 2                                           |    | 8.2 Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 |

| 5 | Pin Configuration and Functions3                   |    | 8.3 Feature Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18 |

| 6 | Specifications4                                    |    | 8.4 Device Functional Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19 |

| • | 6.1 Absolute Maximum Ratings                       | 9  | Application and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20 |

|   | 6.2 ESD Ratings                                    |    | 9.1 Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|   | 6.3 Recommended Operating Conditions               |    | 9.2 Typical Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|   | 6.4 Thermal Information                            | 10 | Power Supply Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|   | 6.5 Power Ratings                                  | 11 | Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|   | 6.6 Insulation Specifications                      |    | 11.1 Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|   | 6.7 Safety-Related Certifications                  |    | 11.2 Layout Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|   | 6.8 Safety Limiting Values7                        | 12 | 器件和文档支持                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|   | 6.9 DC Electrical Characteristics                  |    | 12.1 文档支持                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|   | 6.10 DC Supply Current Characteristics9            |    | 12.2 接收文档更新通知                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|   | 6.11 Timing Requirements for Distortion Correction |    | 12.3 社区资源                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|   | Scheme9                                            |    | 12.4 商标                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|   | 6.12 Switching Characteristics                     |    | 12.5 静电放电警告                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|   | 6.13 Insulation Characteristics Curves             |    | 12.6 Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

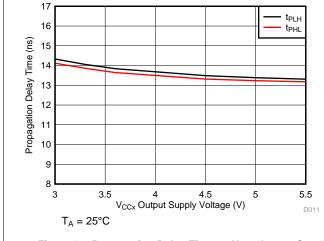

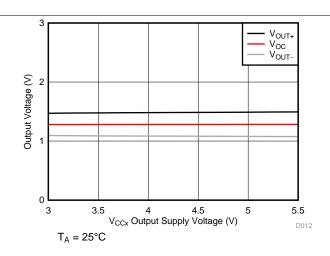

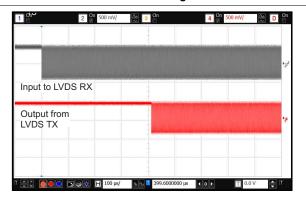

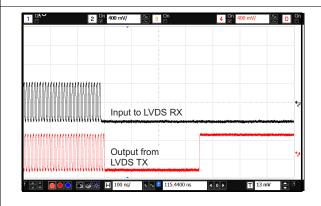

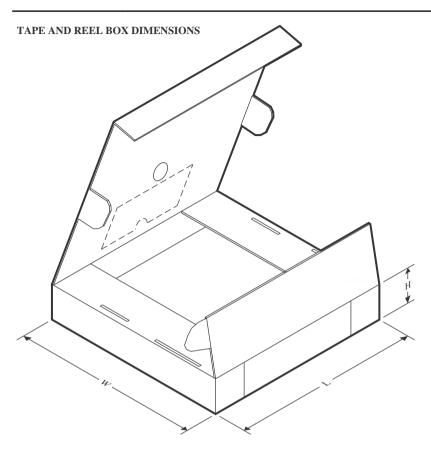

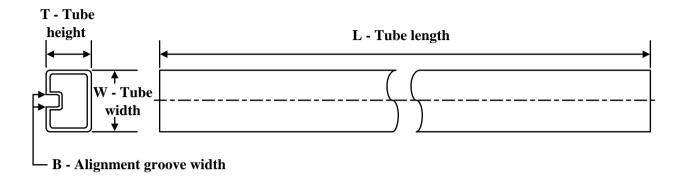

|   | 6.14 Typical Characteristics12                     | 13 | 机械、封装和可订购信息                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|   |                                                    |    | \$ -\$\tau_1 \ - \tau_2 \ \tau_1 \ \ \tau_1 \ \tau_2 \ \tau_1 \ \tau_2 \ \tau_2 \ \tau_3 \ \tau_4 \ \tau_2 \ \tau_2 \ \tau_3 \ \tau_4 \ \tau_2 \ \tau_3 \ \tau_4 \ \tau_2 \ \tau_3 \ \tau_4 \ \tau_3 \ \tau_4 \ \tau_4 \ \tau_5 \ \tau |    |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

# Changes from Original (March 2016) to Revision A

Page

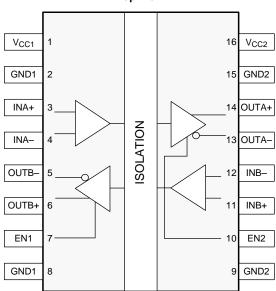

# 5 Pin Configuration and Functions

#### DW and DWW Packages 16-Pin SOIC Top View

## **Pin Functions**

|                  | PIN | 1/0 | DESCRIPTION                                                                                                              |  |  |

|------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME             | NO. | 1/0 | DESCRIPTION                                                                                                              |  |  |

| EN1              | 7   | 1   | Output enable 1. Output pins on side 1 are enabled when EN1 is high or open and in high impedance state when EN1 is low. |  |  |

| EN2              | 10  | I   | Output enable 2. Output pins on side 2 are enabled when EN2 is high or open and in high impedance state when EN2 is low. |  |  |

| CND4             | 2   |     | Crown description for V                                                                                                  |  |  |

| GND1             | 8   |     | Ground connection for V <sub>CC1</sub>                                                                                   |  |  |

| CNIDO            | 9   |     | Crown description for V                                                                                                  |  |  |

| GND2             | 15  |     | Ground connection for V <sub>CC2</sub>                                                                                   |  |  |

| INA+             | 3   | I   | Positive differential input, channel A                                                                                   |  |  |

| INA-             | 4   | I   | Negative differential input, channel A                                                                                   |  |  |

| INB+             | 11  | I   | Positive differential input, channel B                                                                                   |  |  |

| INB-             | 12  | I   | Negative differential input, channel B                                                                                   |  |  |

| OUTA+            | 14  | 0   | Positive differential output, channel A                                                                                  |  |  |

| OUTA-            | 13  | 0   | Negative differential output, channel A                                                                                  |  |  |

| OUTB+            | 6   | 0   | Positive differential output, channel B                                                                                  |  |  |

| OUTB-            | 5   | 0   | Negative differential output, channel B                                                                                  |  |  |

| V <sub>CC1</sub> | 1   | _   | Power supply, side 1, V <sub>CC1</sub>                                                                                   |  |  |

| V <sub>CC2</sub> | 16  | _   | Power supply, side 2, V <sub>CC2</sub>                                                                                   |  |  |

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                           |                                     | MIN  | MAX                   | UNIT |

|------------------|-------------------------------------------|-------------------------------------|------|-----------------------|------|

| V <sub>CCx</sub> | Supply voltage (2)                        | V <sub>CC1</sub> , V <sub>CC2</sub> | -0.5 | 6                     | V    |

| V                | Voltage on input, output, and enable pins | OUTx, INx, ENx                      | -0.5 | $V_{CCx} + 0.5^{(3)}$ | V    |

| Io               | Maximum current through OUTx pins         |                                     | -20  | 20                    | mA   |

| T <sub>J</sub>   | Junction temperature                      |                                     | -55  | 150                   | °C   |

| T <sub>stg</sub> | Storage temperature                       |                                     | -65  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

| ., Electrostatic   | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±4500 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

|                                     |                                            |                                           | MIN                  | NOM | MAX                        | UNIT |

|-------------------------------------|--------------------------------------------|-------------------------------------------|----------------------|-----|----------------------------|------|

| V <sub>CC1</sub> , V <sub>CC2</sub> | Supply voltage                             |                                           | 3                    | 3.3 | 5.5                        | V    |

| V <sub>ID</sub>                     | Magnitude of RX input differential voltage | Driven with voltage sources on RX pins    | 100                  |     | 600                        | mV   |

| V <sub>IC</sub>                     | RX input common-<br>mode voltage           | V <sub>CC1</sub> , V <sub>CC2</sub> ≥ 3 V | 0.5  V <sub>ID</sub> |     | 2.4 – 0.5  V <sub>ID</sub> | V    |

| $R_L$                               | TX far-end differential te                 | ermination                                |                      | 100 |                            | Ω    |

| DR                                  | Signaling rate                             |                                           | 50                   |     | 150                        | Mbps |

| T <sub>A</sub>                      | Ambient temperature                        |                                           | -55                  | 25  | 125                        | °C   |

<sup>(2)</sup> All voltage values except differential I/O bus voltages are with respect to the local ground pin (GND1 or GND2) and are peak voltage values.

<sup>(3)</sup> Maximum voltage must not exceed 6 V.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.4 Thermal Information

|                         |                                              | ISO7821LLS |            |      |  |

|-------------------------|----------------------------------------------|------------|------------|------|--|

|                         | THERMAL METRIC <sup>(1)</sup>                | DW (SOIC)  | DWW (SOIC) | UNIT |  |

|                         |                                              | 16 PINS    | 16 PINS    |      |  |

| $R_{\theta JA}$         | Junction-to-ambient thermal resistance       | 82         | 84.6       | °C/W |  |

| $R_{\theta JC(top)}$    | Junction-to-case(top) thermal resistance     | 44.6       | 46.4       | °C/W |  |

| $R_{\theta JB}$         | Junction-to-board thermal resistance         | 46.6       | 55.3       | °C/W |  |

| ΨЈТ                     | Junction-to-top characterization parameter   | 17.8       | 18.7       | °C/W |  |

| ΨЈВ                     | Junction-to-board characterization parameter | 46.1       | 54.5       | °C/W |  |

| $R_{\theta JC(bottom)}$ | Junction-to-case(bottom) thermal resistance  | _          | _          | °C/W |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Power Ratings

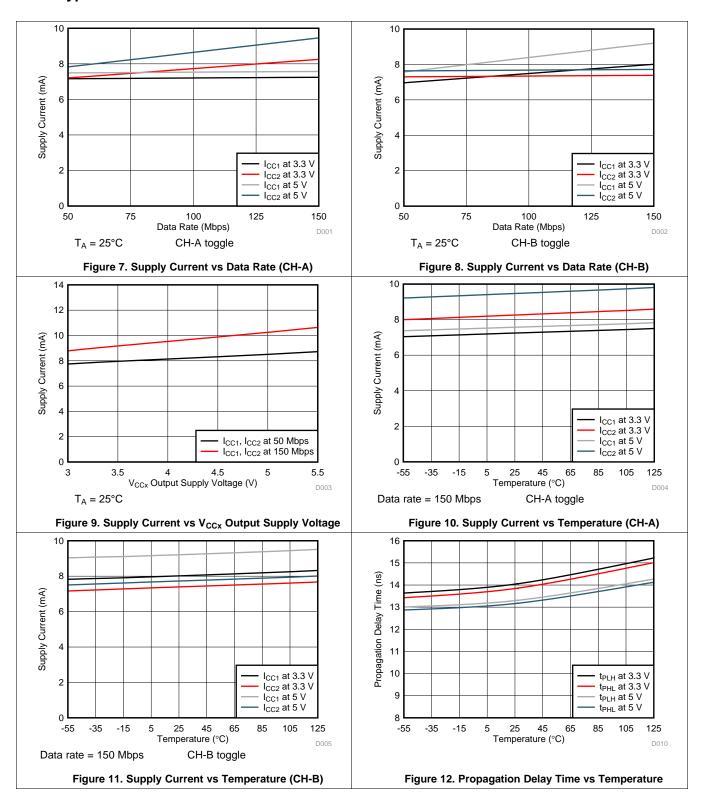

$V_{CC1}$  =  $V_{CC2}$  = 5.5 V,  $T_J$  = 150°C,  $C_L$  = 5 pF,  $R_L$  = 100- $\Omega$  differential, input a 75-MHz 50% duty-cycle square wave, EN1 = EN2 = 5.5 V

|                 | PARAMETER                              | TEST CONDITIONS | MAX | TYP | MAX | UNIT |

|-----------------|----------------------------------------|-----------------|-----|-----|-----|------|

| $P_{D}$         | Maximum power dissipation (both sides) |                 |     |     | 180 | mW   |

| P <sub>D1</sub> | Maximum power dissipation (side 1)     |                 |     |     | 90  | mW   |

| P <sub>D2</sub> | Maximum power dissipation (side 2)     |                 |     |     | 90  | mW   |

# 6.6 Insulation Specifications

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                        | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                    | SPECIF            | ICATION           | UNIT             |

|-------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------|

|                   | FARAINETER                                       | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                    | DW                | DWW               | UNIT             |

| GENEF             | RAL                                              |                                                                                                                                                                                                                                                                                                                                    |                   |                   |                  |

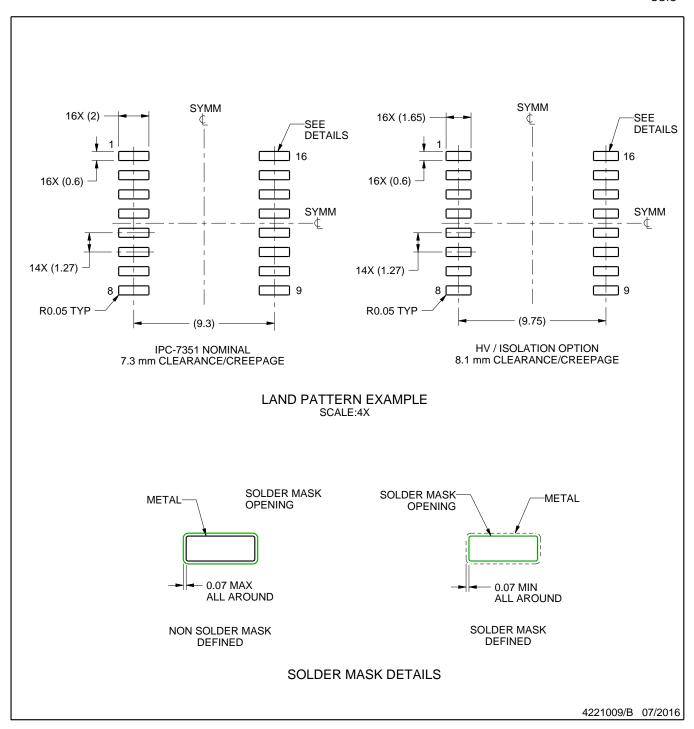

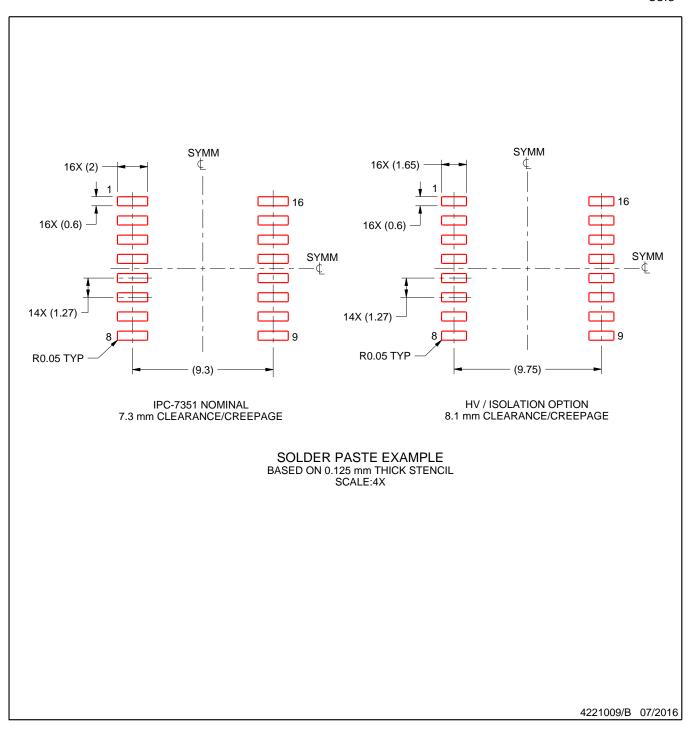

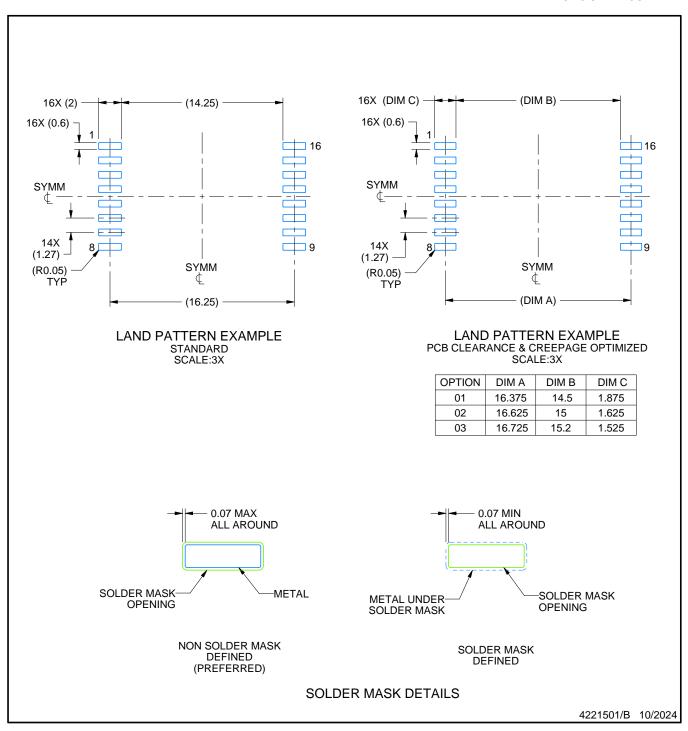

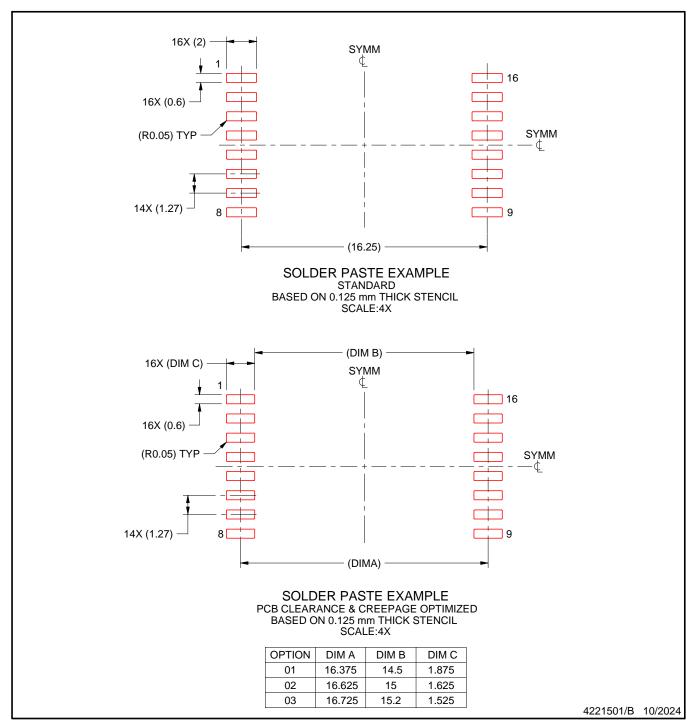

| CLR               | External clearance <sup>(1)</sup>                | Shortest terminal-to-terminal distance through air                                                                                                                                                                                                                                                                                 | >8                | >14.5             | mm               |

| CPG               | External creepage <sup>(1)</sup>                 | Shortest terminal-to-terminal distance across the package surface                                                                                                                                                                                                                                                                  | >8                | >14.5             | mm               |

| DTI               | Distance through the insulation                  | Minimum internal gap (internal clearance)                                                                                                                                                                                                                                                                                          | >21               | >21               | μm               |

| СТІ               | Tracking resistance (comparative tracking index) | DIN EN 60112 (VDE 0303-11); IEC 60112; UL 746A                                                                                                                                                                                                                                                                                     | >600              | >600              | V                |

|                   | Material group                                   | According to IEC 60664-1                                                                                                                                                                                                                                                                                                           | I                 | 1                 |                  |

|                   | Overvelte as estagen, per IEC 60664.1            | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                                                                                                                                                         | I–IV              | I–IV              |                  |

|                   | Overvoltage category per IEC 60664-1             | Rated mains voltage ≤ 1000 V <sub>RMS</sub>                                                                                                                                                                                                                                                                                        | I–III             | I–IV              |                  |

| DIN V             | VDE V 0884-10 (VDE V 0884-10):2006-1             | 12 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                  |                   |                   |                  |

| $V_{IORM}$        | Maximum repetitive peak isolation voltage        | AC voltage (bipolar)                                                                                                                                                                                                                                                                                                               | 2121              | 2828              | V <sub>PK</sub>  |

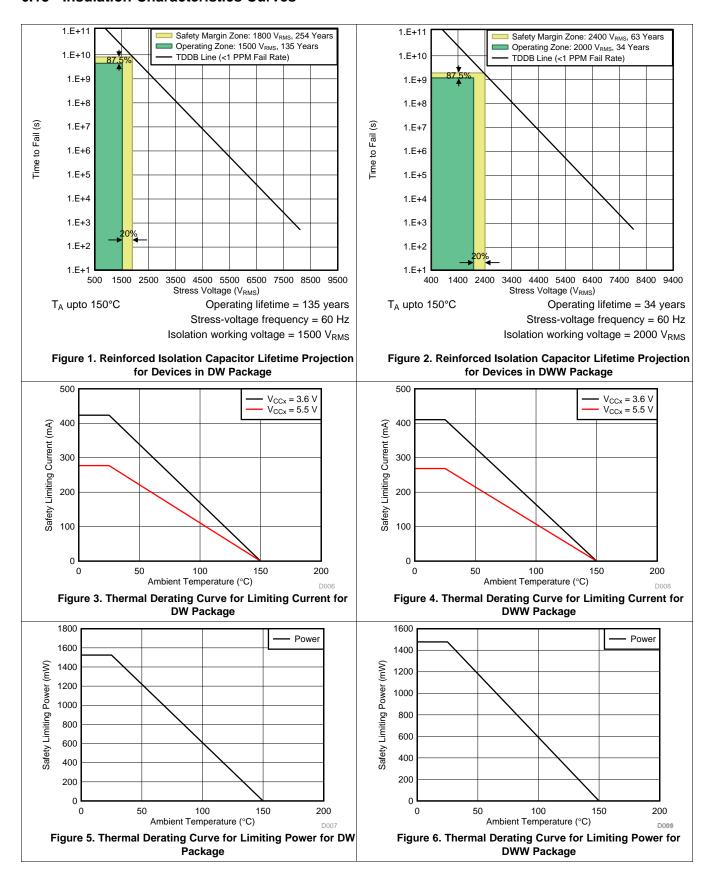

| V <sub>IOWM</sub> | Maximum isolation working voltage                | AC voltage (sine wave); time dependent dielectric breakdown (TDDB) test; see Figure 1 and Figure 2                                                                                                                                                                                                                                 | 1500              | 2000              | V <sub>RMS</sub> |

| IOWINI            | 5 5                                              | DC voltage                                                                                                                                                                                                                                                                                                                         | 2121              | 2828              | $V_{DC}$         |

| V <sub>IOTM</sub> | Maximum transient isolation voltage              | V <sub>TEST</sub> = V <sub>IOTM</sub> , t = 60 s (qualification)<br>t = 1 s (100% production)                                                                                                                                                                                                                                      | 8000              | 8000              | V <sub>PK</sub>  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage (3)              | Test method per IEC 60065, 1.2/50 $\mu$ s waveform, $V_{TEST} = 1.6 \times V_{IOSM} = 12800 V_{PK}$ (qualification)                                                                                                                                                                                                                | 8000              | 8000              | V <sub>PK</sub>  |

|                   |                                                  | Method a: After I/O safety test subgroup 2/3, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60$ s; $V_{pd(m)} = 1.2 \times V_{IORM} = 2545 \ V_{PK}$ (DW) and 3394 $V_{PK}$ (DWW), $t_m = 10$ s                                                                                                                                                | ≤5                | ≤5                |                  |

| q <sub>pd</sub>   | Apparent charge (4)                              | Method a: After environmental tests subgroup 1, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60 \text{ s}$ ; $V_{pd(m)} = 1.6 \times V_{IORM} = 3394 \text{ V}_{PK}$ (DW) and 4525 $V_{PK}$ (DWW), $t_m = 10 \text{ s}$                                                                                                                       | ≤5                | ≤5                | рС               |

|                   |                                                  | Method b1: At routine test (100% production) and preconditioning (type test) $ V_{\text{ini}} = V_{\text{IORM}}, t_{\text{ini}} = 1 \text{ s}; \\ V_{\text{pd(m)}} = 1.875 \times V_{\text{IORM}} = 3977 \text{ V}_{\text{PK}} \text{ (DW)} \text{ and } \\ 5303 \text{ V}_{\text{PK}} \text{ (DWW)}, t_{\text{m}} = 1 \text{ s} $ | ≤5                | ≤5                |                  |

| C <sub>IO</sub>   | Barrier capacitance, input to output (5)         | $V_{IO} = 0.4 \times \sin(2\pi ft), f = 1 \text{ MHz}$                                                                                                                                                                                                                                                                             | ~0.7              | ~0.7              | pF               |

|                   |                                                  | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                     | >10 <sup>12</sup> | >10 <sup>12</sup> |                  |

| R <sub>IO</sub>   | Isolation resistance, input to output (5)        | $V_{IO} = 500 \text{ V}, 100^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$                                                                                                                                                                                                                                                    | >10 <sup>11</sup> | >10 <sup>11</sup> | Ω                |

|                   |                                                  | $V_{IO} = 500 \text{ V at } T_{S} = 150^{\circ}\text{C}$                                                                                                                                                                                                                                                                           | >10 <sup>9</sup>  | >10 <sup>9</sup>  |                  |

|                   | Pollution degree                                 |                                                                                                                                                                                                                                                                                                                                    | 2                 | 2                 |                  |

|                   | Climatic category                                |                                                                                                                                                                                                                                                                                                                                    | 55/125/21         | 55/125/21         |                  |

| UL 157            | 7                                                |                                                                                                                                                                                                                                                                                                                                    |                   |                   |                  |

| V <sub>ISO</sub>  | Withstanding isolation voltage                   | $V_{TEST} = V_{ISO} = 5700 \text{ V}_{RMS}, t = 60 \text{ s (qualification)};$<br>$V_{TEST} = 1.2 \times V_{ISO} = 6840 \text{ V}_{RMS},$<br>t = 1  s (100% production)                                                                                                                                                            | 5700              | 5700              | V <sub>RMS</sub> |

<sup>(1)</sup> Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves and/or ribs on a printed circuit board are used to help increase these specifications.

- (3) Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

- (4) Apparent charge is electrical discharge caused by a partial discharge (pd).

- 5) All pins on each side of the barrier tied together creating a two-terminal device.

<sup>(2)</sup> This coupler is suitable for safe electrical insulation only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

# 6.7 Safety-Related Certifications

| VDE                                                                                                                                                                                                                                       | CSA                                                                                                                                                                                                                                                                                                                                                                          | UL                                                                       | CQC                                                                                                      | TUV                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Plan to certify according to<br>DIN V VDE V 0884-10<br>(VDE V 0884-10):2006-12<br>and DIN EN 60950-1 (VDE<br>0805 Teil 1):2011-01                                                                                                         | Plan to certify under CSA<br>Component Acceptance<br>Notice 5A, IEC 60950-1 and<br>IEC 60601-1                                                                                                                                                                                                                                                                               | Plan to certify according<br>to UL 1577 Component<br>Recognition Program | Plan to certify according to<br>GB 4943.1-2011                                                           | Plan to certify according to<br>EN 61010-1:2010 (3rd Ed) and<br>EN 60950-1:2006/A11:2009/A1:2010/<br>A12:2011/A2:2013                                                                                                                                                                                                                                                             |

| Reinforced insulation Maximum transient isolation voltage, 8000 V <sub>PK</sub> ; Maximum repetitive peak isolation voltage, 2121 V <sub>PK</sub> (DW), 2828 V <sub>PK</sub> (DWW); Maximum surge isolation voltage, 8000 V <sub>PK</sub> | Reinforced insulation per CSA 60950-1-07+A1+A2 and IEC 60950-1 2nd Ed., 800 V <sub>RMS</sub> (DW package) and 1450 V <sub>RMS</sub> (DWW package) max working voltage (pollution degree 2, material group I);  2 MOPP (Means of Patient Protection) per CSA 60601-1:14 and IEC 60601-1 Ed. 3.1, 250 V <sub>RMS</sub> (354 V <sub>PK</sub> ) max working voltage (DW package) | Single protection, 5700 V <sub>RMS</sub>                                 | Reinforced Insulation, Altitude ≤ 5000 m, Tropical Climate, 250 V <sub>RMS</sub> maximum working voltage | 5700 V <sub>RMS</sub> Reinforced insulation per EN 61010-1:2010 (3rd Ed) up to working voltage of 600 V <sub>RMS</sub> (DW package) and 1000 V <sub>RMS</sub> (DWW package)  5700 V <sub>RMS</sub> Reinforced insulation per EN 60950-1:2006/A11:2009/A1:2010/A12:2011/A2:2013 up to working voltage of 800 V <sub>RMS</sub> (DW package) and 1450 V <sub>RMS</sub> (DWW package) |

| Certification planned                                                                                                                                                                                                                     | Certification planned                                                                                                                                                                                                                                                                                                                                                        | Certification planned                                                    | Certification planned                                                                                    | Certification planned                                                                                                                                                                                                                                                                                                                                                             |

#### 6.8 Safety Limiting Values

Safety limiting intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry. A failure of the I/O can allow low resistance to ground or the supply and, without current limiting, dissipate sufficient power to overheat the die and damage the isolation barrier potentially leading to secondary system failures.

|                | PARAMETER                            | TEST CONDITIONS                                                                                                 | MIN | TYP | MAX  | UNIT |  |

|----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|------|------|--|

| DW P           | ACKAGE                               |                                                                                                                 |     |     |      |      |  |

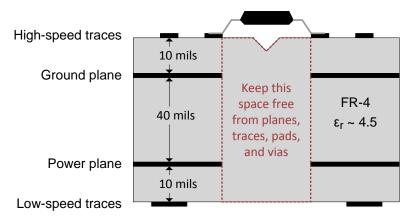

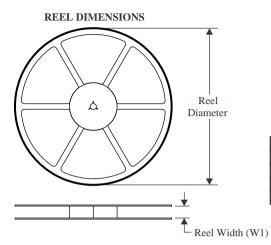

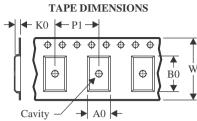

|                | Safety input, output, or supply      | $R_{\theta JA} = 82^{\circ}C/W$ , $V_I = 5.5$ V, $T_J = 150^{\circ}C$ , $T_A = 25^{\circ}C$ , see Figure 3      | 277 |     | Λ    |      |  |