**SN65DSI86**

ZHCSBP5C - SEPTEMBER 2013 - REVISED OCTOBER 2020

# SN65DSI86 MIPI® DSI 至 eDP™ 桥

# 1 特性

- 与嵌入式 DisplayPort™ (eDP™) 1.4 兼容,支持 1.62Gbps (RBR)、2.16Gbps、2.43Gbps、 2.7Gbps (HBR)、3.24Gbps、4.32Gbps 或 5.4Gbps (HBR2) 的 1、2 或 4 信道。

- 实现了 MIPI® D-PHY 版本 1.1 物理层前端和显示串 行接口 (DSI) 版本 1.02.00

- 双通道 DSI 接收器在每个通道上可针对 1 条、2 条、3条或4条 D-PHY 数据信道进行配置,每信道 的运行速率高达 1.5Gbps

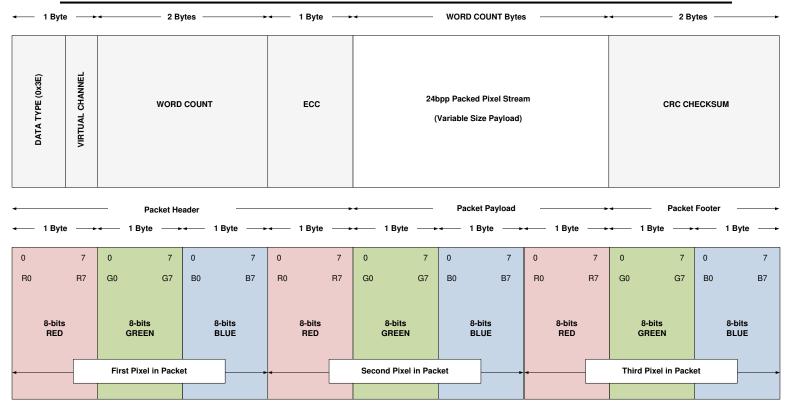

- 支持格式为 RGB666 和 RGB888 的 18bpp 和 24bpp DSI 视频数据包

- 适合 60fps 4K 4096 × 2304 分辨率 (18bpp 彩色) 以及 60fps 的 WUXGA 1920 × 1200 分辨率和 3D 图形显示(相当于 120fps)

- MIPI 前端可配置用于单通道或双通道 DSI 配置

- 支持双通道 DSI 奇/偶以及左/右工作模式

- 1.2V VCC 主电源, 1.8V 电源用于数字 I/O

- 低功耗特性包括面板刷新和 MIPI 超低功耗状态 (ULPS) 支持

- 可配置 DisplayPort 信道极性和分配。

- 通过外部基准时钟 (REFCLK) 支持 12MHz、 19.2MHz、26MHz、27MHz 和 38.4MHz 等频率

- ESD 等级 ±4kV (HBM)

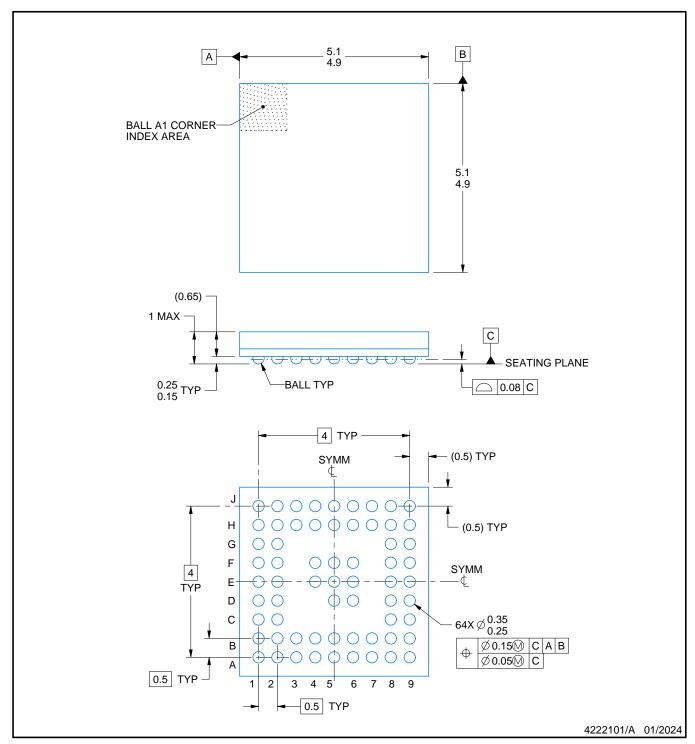

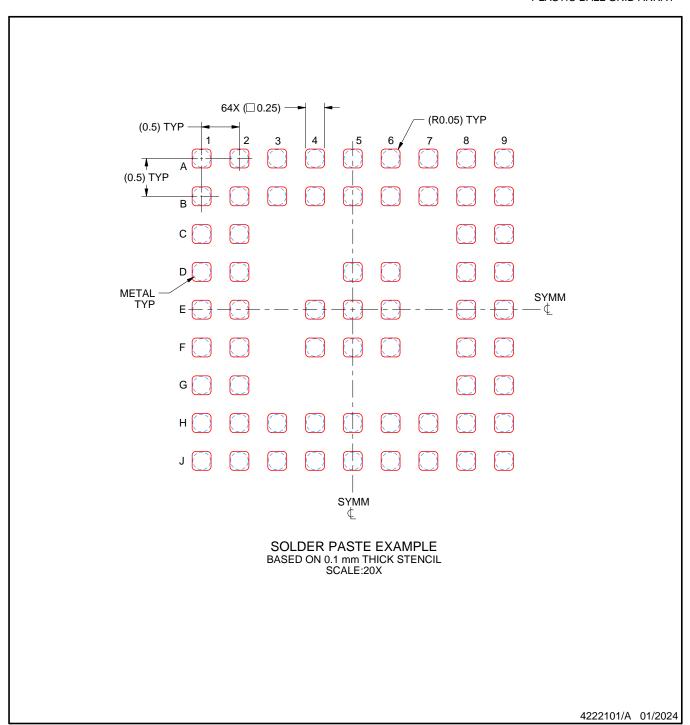

- 采用 64 焊球 5mm x 5mm nFBGA (ZXH) 封装

- I<sup>2</sup>C 可配置

- 温度范围: -40°C至+85°C

### 2 应用

- PC 和笔记本电脑

- 平板电脑

- 零售自动化和支付

- 测试和测量

- 工厂自动化和控制

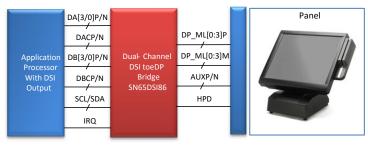

# 3 说明

SN65DSI86 DSI 至嵌入式 DisplayPort (eDP) 桥接器 采用双通道 MIPI D-PHY 接收器前端配置,此配置中在 每个通道上具有 4 个信道,每个信道的运行速率为 1.5Gbps,最大输入带宽为 12Gbps。该桥接器可解码 MIPI DSI 18bpp RGB666 和 24bpp RGB888 视频流, 并将格式化视频数据流转换到具有多达四条信道的 DisplayPort,每条信道的运行速率为 1.62Gbps、2.16 Gbps、2.43 Gbps、2.7Gbps、3.24Gbps、4.32Gbps 或 5.4Gbps。

SN65DSI86 非常适合每秒 60 帧的 WQXGA,以及等 效 120fps (高达 24bpp )的 4K 和真正高清 (1920 × 1080) 分辨率 3D 图形。执行了部分线路缓冲以适应 DSI 与 DisplayPort 接口间的数据流不匹配。

## 器件信息(1)

| 器件型号      | 封装         | 封装尺寸 ( 标称值 )    |

|-----------|------------|-----------------|

| SN65DSI86 | nFBGA (64) | 5.00mm x 5.00mm |

Copyright © 2017, Texas Instruments Incorporated

# 简单方框图

# **Table of Contents**

| 1 特性                                 | 1 | 8.5 Programming                                            | 43                 |

|--------------------------------------|---|------------------------------------------------------------|--------------------|

|                                      |   | 8.6 Register Map                                           |                    |

| - <i>二/1.</i><br>3 说明                |   | 9 Application and Implementation                           |                    |

| 4 Revision History                   |   | 9.1 Application Information                                | <mark>69</mark>    |

| 5 Description (continued)            |   | 9.2 Typical Application                                    | 70                 |

| 6 Pin Configuration and Functions    |   | 10 Power Supply Recommendations                            | 7 <mark>5</mark>   |

| 7 Specifications                     |   | 10.1 V <sub>CC</sub> Power Supply                          | <mark>75</mark>    |

| 7.1 Absolute Maximum Ratings         |   | 10.2 V <sub>CCA</sub> Power supply                         |                    |

| 7.2 ESD Ratings                      |   | 10.3 V <sub>PLL</sub> and V <sub>CCIO</sub> Power Supplies | 7 <mark>5</mark>   |

| 7.3 Recommended Operating Conditions |   | 11 Layout                                                  |                    |

| 7.4 Thermal Information              |   | 11.1 Layout Guidelines                                     |                    |

| 7.5 Electrical Characteristics       |   | 11.2 Layout Example                                        | <mark>77</mark>    |

| 7.6 Timing Requirements              |   | 12 Device and Documentation Support                        | 7 <mark>8</mark>   |

| 7.7 Switching Characteristics        |   | 12.1 Documentation Support                                 | 78                 |

| 8 Detailed Description               |   | 12.2 Receiving Notification of Documentation Updat         | es <mark>78</mark> |

| 8.1 Overview                         |   | 12.3 Community Resources                                   | <mark>78</mark>    |

| 8.2 Functional Block Diagram         |   | 12.4 Trademarks                                            | 78                 |

| 8.3 Feature Description              |   | 13 Mechanical, Packaging, and Orderable                    |                    |

| 8.4 Device Functional Modes          |   | Information                                                | <mark>78</mark>    |

| 5 5                                  |   |                                                            |                    |

# **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision B (March 2017) to Revision C (October 2020)                                                      | Page |

|---|-----------------------------------------------------------------------------------------------------------------------|------|

| • | 注:采用 MicroStar Jr. BGA 封装的器件采用层压 nFBGA 封装进行了重新设计。这种 nFBGA 封装提供于数据表中的电气性能。该封装占用空间也类似于 MicroStar Jr. BGA。将在整个数据表中更新全新封装 |      |

|   |                                                                                                                       |      |

|   | 来代替已停止使用的封装标识符。                                                                                                       |      |

| • | 将 u*jr ZQE 更改为 nFBGA ZXH                                                                                              |      |

| • | Changed u*jr ZQE to nFBGA ZXH                                                                                         |      |

| • | Changed u*jr ZQE to nFBGA ZXH. Updated thermal information                                                            | 8    |

| С | hanges from Revision A (November 2015) to Revision B (March 2017)                                                     | Page |

| • | 删除了数据表中的 SN65DSI96 器件型号                                                                                               | 1    |

| • | 删除了特性"自适应内容管理和背光 PWM 控制"                                                                                              | 1    |

| • | 添加了 <i>特性</i> : I2C 可配置                                                                                               |      |

| • | 更新了 <i>应用</i> 列表                                                                                                      |      |

| • | 更换了简单方框图                                                                                                              |      |

| • | Changed SN65DSIx6 To: SN65DSI86 throughout the data sheet                                                             |      |

| • | Deleted pagraph "For the SN65DSI96, the brightness is controlled" from the <i>Pulse Width Modulation</i>              |      |

|   | section                                                                                                               | . ,  |

| • | Deleted the PWM Backlight Selection Options table                                                                     |      |

| • | Deleted the Assertive Display (SN65DSI96 Only) section.                                                               |      |

| • | Deleted step: "Configure Assertive Display Core. (For SN65DSI96 only)" from the Power-Up Sequence                     |      |

|   |                                                                                                                       | 21   |

|   | Deleted step: "For SN65DSI96, disable Assertive Display core by clearing the ADEN bit." from the Pou                  |      |

|   | Down Sequence section                                                                                                 |      |

|   | Changed 图 8-14                                                                                                        |      |

|   | Deleted SN65DSI96 from address 0x00 through 0x07 of 表 8-19                                                            |      |

|   | Deleted address 0x3F from the 表 8-22                                                                                  |      |

| • | Deleted address 0x01 HUIII the 🕸 0-22                                                                                 | 45   |

### www.ti.com.cn

| • | Deleted "This register is also used for SN65DSI96 when OPTION_SELECT is not equal to zero." from address 0xA3 in 表 8-27 | 45     |

|---|-------------------------------------------------------------------------------------------------------------------------|--------|

|   | Deleted "This register is also used for SN65DSI96 when OPTION_SELECT is not equal to zero." from address 0xA4 in 表 8-27 | 45     |

| • | Changed 0xE6 Bits 7, 6, and 4 to Reserved in 表 8-30                                                                     | 45     |

| • | Changed 0xF5 Bits 7, 6, and 4 to Reserved in 表 8-31                                                                     | 45     |

|   | Deleted options 001 to 110 for 0xFF Bit 2:0 in 表 8-32                                                                   | Page   |

|   | 添加了 <i>引脚配置和功能</i> 部分、 <b>ESD</b> 等级表、特性说明部分、器件功能模式、应用和实施部分、电源相关                                                        |        |

| • | 议部分、布局部分、器件和文档支持部分以及机械、封装和可订购信息部分                                                                                       | 1<br>8 |

| • |                                                                                                                         | 4      |

# 5 Description (continued)

Designed with industry compliant interface technology, the SN65DSI86 is compatible with a wide range of microprocessors, and is designed with a range of power management features, including panel refresh support, and the MIPI defined ultralow power state (ULPS) support.

The SN65DSI86 is implemented in a small outline, 5-mm × 5-mm, MicroStar Junior ball-grid array (BGA) at 0.5-mm pitch package, and operates across a temperature range from - 40°C to +85°C.

In the rest of this document, the SN65DSI86 is referred to as SN65DSI86 . Anytime SN65DSI86 is used, then that particular sentence or feature only refers to that specific part.

Product Folder Links: SN65DSI86

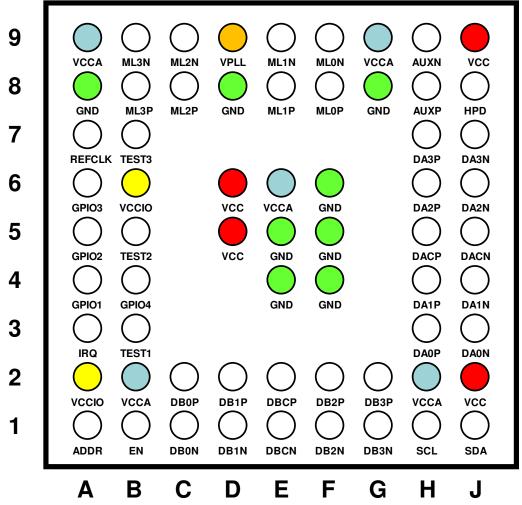

# **6 Pin Configuration and Functions**

See #11.1 for additional information.

图 6-1. ZXH Package 64-Pin nFBGA Top View

表 6-1. Pin Functions

| PI     | IN     | 1/0                                              | DESCRIPTION                                                                                                                                                                                                                                                |

|--------|--------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.    | 1/0                                              | DESCRIPTION                                                                                                                                                                                                                                                |

| ADDR   | A1     | CMOS Input/Output                                | Local I <sup>2</sup> C interface target address select. See 表 8-4. In normal operation, this pin is an input. When the ADDR pin is programmed high, it must be tied to the same 1.8-V power rails where the SN65DSI86 VCCIO 1.8-V power rail is connected. |

| AUXP/N | H8, H9 | LVDS I/O                                         | Auxiliary-channel differential pair                                                                                                                                                                                                                        |

| DA0P/N | H3, J3 | LVDS Input (HS)<br>CMOS Input/Output<br>(LS)     | MIPI D-PHY channel A data lane 0; data rate up to 1.5 Gbps.                                                                                                                                                                                                |

| DA1P/N | H4, J4 | LVDS Input (HS)<br>CMOS Input (LS)<br>(Failsafe) | MIPI D-PHY channel a data lane 1; data rate up to 1.5 Gbps.                                                                                                                                                                                                |

| DA2P/N | H6, J6 | LVDS Input (HS)<br>CMOS Input (LS)<br>(Failsafe) | MIPI D-PHY channel A data lane 2; data rate up to 1.5 Gbps                                                                                                                                                                                                 |

# 表 6-1. Pin Functions (continued)

| Р         | IN                                   |                                                  | DESCRIPTION                                                                                                                                                                                                                                                                               |

|-----------|--------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.                                  | - I/O                                            | DESCRIPTION                                                                                                                                                                                                                                                                               |

| DA3P/N    | H7, J7                               | LVDS Input (HS)<br>CMOS Input (LS)<br>(Failsafe) | MIPI D-PHY channel A data lane 3; data rate up to 1.5 Gbps.                                                                                                                                                                                                                               |

| DACP/N    | H5, J5                               | LVDS Input (HS)<br>CMOS Input (LS)<br>(Failsafe) | MIPI D-PHY channel A clock lane; operates up to 750 MHz. Under proper conditions, this clock can be used instead of REFCLK to feed DisplayPort PLL.                                                                                                                                       |

| DB0P/N    | C2, C1                               | LVDS Input (HS)<br>CMOS Input (LS)<br>(Failsafe) | MIPI D-PHY channel B data lane 0; data rate up to 1.5 Gbps.                                                                                                                                                                                                                               |

| DB1P/N    | D2, D1                               | LVDS Input (HS)<br>CMOS Input (LS)<br>(Failsafe) | MIPI D-PHY channel B data lane 1; data rate up to 1.5 Gbps.                                                                                                                                                                                                                               |

| DB2P/N    | F2, F1                               | LVDS Input (HS)<br>CMOS Input (LS)<br>(Failsafe) | MIPI D-PHY channel B data lane 2; data rate up to 1.5 Gbps.                                                                                                                                                                                                                               |

| DB3P/N    | G2, G1                               | LVDS Input (HS)<br>CMOS Input (LS)<br>(Failsafe) | MIPI D-PHY channel B data lane 3; data rate up to 1.5 Gbps.                                                                                                                                                                                                                               |

| DBCP/N    | E2, E1                               | LVDS Input (HS)<br>CMOS Input (LS)<br>(Failsafe) | MIPI D-PHY channel B clock lane; operates up to 750 MHz.                                                                                                                                                                                                                                  |

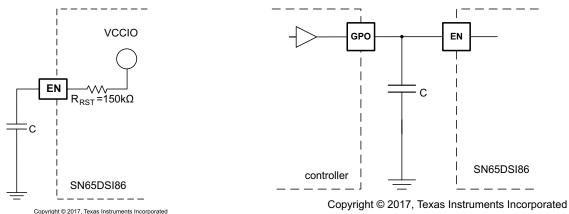

| EN        | B1                                   | CMOS Input<br>(Failsafe)                         | Chip enable and reset. Device is reset (shutdown) when EN is low.  Deassertion (low) of EN will cause all internal CSRs and functions to be reset to default state.                                                                                                                       |

| GND       | A8, D8, E4,<br>E5, F4, F5,<br>F6, G8 | Power Supply                                     | Reference ground for digital and analog circuits.                                                                                                                                                                                                                                         |

| GPIO[4:1] | B4, A6, A5,<br>A4                    | CMOS Input/Output                                | General-purpose I/O. See #8.3.3 section for details on GPIO functionality. When these pins are set high, tie the pins to the same 1.8-V power rail that the SN65DSI86 VCCIO 1.8-V power rail is connected to.                                                                             |

| HPD       | J8                                   | CMOS Input with internal pulldown. (Failsafe)    | HPD input. This input requires a 51-k $\Omega$ 1% series resistor.                                                                                                                                                                                                                        |

| IRQ       | А3                                   | CMOS Output                                      | Interrupt signal                                                                                                                                                                                                                                                                          |

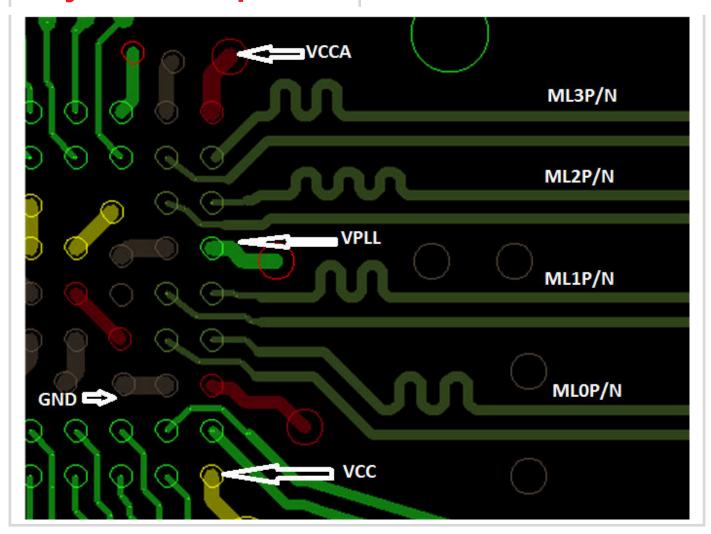

| ML0P/N    | F8, F9                               | LVDS output (DP)                                 | DisplayPort lane 0 transmit differential pair. Supports 1.62 Gbps, 2.16 Gbps, 2.43 Gbps, 2.7 Gbps, 3.24 Gbps, 4.32 Gbps, and 5.4 Gbps. All DisplayPort lanes transmit at the same data rate.                                                                                              |

| ML1P/N    | E8, E9                               | LVDS output (DP)                                 | DisplayPort lane 1 transmit differential pair. Supports 1.62 Gbps, 2.16 Gbps, 2.43 Gbps, 2.7 Gbps, 3.24 Gbps, 4.32 Gbps, and 5.4 Gbps. All DisplayPort lanes transmit at the same data rate.                                                                                              |

| ML2P/N    | C8, C9                               | LVDS output (DP)                                 | DisplayPort lane 2 transmit differential pair. Supports 1.62 Gbps, 2.16 Gbps, 2.43 Gbps, 2.7 Gbps, 3.24 Gbps, 4.32 Gbps, and 5.4 Gbps. All DisplayPort lanes transmit at the same data rate.                                                                                              |

| ML3P/N    | B8, B9                               | LVDS output (DP)                                 | DisplayPort lane 3 transmit differential pair. Supports 1.62 Gbps, 2.16 Gbps, 2.43 Gbps, 2.7 Gbps, 3.24 Gbps, 4.32 Gbps, and 5.4 Gbps. All DisplayPort lanes transmit at the same data rate.                                                                                              |

| REFCLK    | A7                                   | Input                                            | Reference clock. Frequency determined by value programmed in I <sup>2</sup> C register or value of GPIO[3:1] latched at rising edge of EN. Supported frequencies are: 12 MHz, 19.2 MHz, 26 MHz, 27 MHz, and 38.4 MHz.  This pin must be tied to GND when DACP/N feeds the DisplayPort PLL |

| SCL       | H1                                   | OpenDrain Input/Output<br>(Failsafe)             | Local I <sup>2</sup> C interface clock.                                                                                                                                                                                                                                                   |

| SDA       | J1                                   | OpenDrain Input/Output<br>(Failsafe)             | Local I <sup>2</sup> C interface bidirectional data signal.                                                                                                                                                                                                                               |

# 表 6-1. Pin Functions (continued)

| P     | IN                    | I/O                                         | DESCRIPTION                                                                                                                                                                                                                                                 |

|-------|-----------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO.                   | 1/0                                         | DESCRIPTION                                                                                                                                                                                                                                                 |

| TEST1 | В3                    | CMOS Input with internal pulldown.          | Used for Texas Instruments internal use only. This pin must be left unconnected or tied to ground.                                                                                                                                                          |

| TEST2 | B5                    | CMOS Input/Output<br>with internal pulldown | Used for internal test, HBR2 compliance eye, and symbol error rate measurement pattern. For normal operation, pull down this pin to GND or leave unconnected. See 表 8-15 for information on HBR2 compliance eye and symbol error rate measurement patterns. |

| TEST3 | B7                    | NA                                          | Used for Texas Instruments internal use only. This pin must be left unconnected or tied to GND through a $0.1$ - $\mu$ F capacitor.                                                                                                                         |

| VCC   | D6, D5, J2,<br>J9     | Power Supply                                | 1.2-V power supply for digital core                                                                                                                                                                                                                         |

| VCCA  | A9, G9,<br>E6, B2, H2 | Power Supply                                | 1.2-V power supply for analog circuits. AVCC and VCC can be applied simultaneously.                                                                                                                                                                         |

| VCCIO | B6, A2                | Power Supply                                | 1.8-V power supply for Digital I/O                                                                                                                                                                                                                          |

| VPLL  | D9                    | Power Supply                                | 1.8-V power supply for DisplayPort PLL                                                                                                                                                                                                                      |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                        |                                      | MIN   | MAX   | UNIT |

|------------------------|--------------------------------------|-------|-------|------|

| Supply voltage         | V <sub>CCA</sub> , V <sub>CC</sub>   | - 0.3 | 1.3   | V    |

|                        | V <sub>CCIO</sub> , V <sub>PLL</sub> | - 0.3 | 2.175 |      |

| Input voltage          | All input terminals                  | - 0.5 | 2.175 | V    |

| Operating temperature  |                                      | - 40  | 85    | °C   |

| Storage temperature, T | stg                                  | - 65  | 105   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under #7.3. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                   |                                          |                                     |       | VALUE | UNIT |

|-------------------|------------------------------------------|-------------------------------------|-------|-------|------|

| V Electrostatic d | Electrostatic discharge                  | Human body model <sup>(1)</sup>     | ±4000 | V     |      |

|                   | V <sub>ESD</sub> Electrostatic discharge | Charged-device model <sup>(2)</sup> | ±500  | V     |      |

Tested in accordance with JEDEC Standard 22, Test Method A114-B

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                      |                                        | MIN                          | NOM | MAX  | UNIT |

|----------------------|----------------------------------------|------------------------------|-----|------|------|

| V <sub>CCA</sub>     | VCCA Power supply; analog circuits     | 1.14                         | 1.2 | 1.26 | V    |

| V <sub>CC</sub>      | VCC Power supply; digital circuits     | 1.14                         | 1.2 | 1.26 | V    |

| V <sub>CCIO</sub>    | VCCIO Power Supply; digital IOs.       | 1.65                         | 1.8 | 1.98 | V    |

| V <sub>PLL</sub>     | VPLL Power Supply, DisplayPort PLL     | 1.65                         | 1.8 | 1.98 | V    |

| V <sub>PSN</sub>     | Supply noise on any VCC terminal       | f <sub>(noise)</sub> > 1 MHz |     | 0.05 | V    |

| V <sub>DSI_PIN</sub> | DSI input pin voltage range            | - 50                         |     | 1350 | mV   |

| f <sub>(I2C)</sub>   | Local I <sup>2</sup> C input frequency |                              |     | 400  | kHz  |

| f <sub>HS_CLK</sub>  | DSI HS clock input frequency           | 40                           |     | 750  | MHz  |

| Z <sub>L</sub>       | DP output differential load impedance  | 90                           |     | 110  | Ω    |

| T <sub>A</sub>       | Operating free-air temperature         | - 40                         |     | 85   | °C   |

| T <sub>J</sub>       | Operating junction temperature         | - 40                         |     | 105  | °C   |

# 7.4 Thermal Information

Submit Document Feedback

|                        |                                                   |                | SN65DSI86 |      |

|------------------------|---------------------------------------------------|----------------|-----------|------|

|                        | THERMAL METRIC                                    | ZXH<br>(nFBGA) | UNIT      |      |

|                        |                                                   |                | 64 PINS   |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance            |                | 55.0      | °C/W |

| R <sub>θ JC(top)</sub> | JC(top) Junction-to-case (top) thermal resistance |                | 30.6      | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance              |                | 31.0      | °C/W |

| ψJT                    | Junction-to-top thermal resistance metric         | High-K board   | 0.8       | °C/W |

| ψ ЈВ                   | Junction-to-board thermal resistance metric       | High-K board   | 30.8      | °C/W |

Product Folder Links: SN65DSI86

Tested in accordance with JEDEC Standard 22, Test Method C101-A

www.ti.com.cn

| THERMAL METRIC(1)                                                   | SN65DSI86  ZXH (nFBGA) |      |

|---------------------------------------------------------------------|------------------------|------|

|                                                                     | 64 PINS                | -    |

| R <sub>θ JC(bot)</sub> Junction-to-case (bottom) thermal resistance | N/A                    | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

# 7.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                                                           | TEST CONDITIONS                                                                                              | MIN                        | TYP <sup>(1)</sup> | MAX                        | UNIT               |

|----------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------|--------------------|----------------------------|--------------------|

| STANDARD IO (TES     | ST1, TEST2, ADDR, SCL, SDA, IRQ, REFC                                               | LK, EN, GPIO[4:1])                                                                                           |                            |                    |                            |                    |

| V <sub>IL</sub>      | Low-level control signal input voltage                                              |                                                                                                              |                            |                    | 0.3 ×<br>V <sub>CCIO</sub> | V                  |

| V <sub>IH</sub>      | High-level control signal input voltage                                             |                                                                                                              | 0.7 ×<br>V <sub>CCIO</sub> |                    |                            | V                  |

| V <sub>OH</sub>      | High-level output voltage                                                           | I <sub>OH</sub> = -2 mA                                                                                      | 1.3                        |                    |                            | V                  |

| V <sub>OL</sub>      | Low-level output voltage                                                            | I <sub>OL</sub> = 2 mA                                                                                       |                            |                    | 0.4                        | V                  |

| I <sub>IH</sub>      | High-level input current                                                            | A i 4 4 i 1                                                                                                  |                            |                    |                            | •                  |

| I <sub>IL</sub>      | Low-level input current                                                             | Any input terminal                                                                                           |                            |                    | ±5                         | μ <b>A</b>         |

| l <sub>oz</sub>      | High-impedance output current                                                       | Any output terminal                                                                                          |                            |                    | ±10                        | μ <b>А</b>         |

| l <sub>os</sub>      | Short-circuit output current                                                        | Any output driving GND short                                                                                 |                            |                    | ±2                         | mA                 |

| I <sub>CCA</sub>     | V <sub>CCA</sub> device active current                                              | V <sub>CCA</sub> = 1.2 V <sup>(2)</sup>                                                                      |                            | 70                 | 126                        | mA                 |

| I <sub>cc</sub>      | V <sub>CC</sub> device active current                                               | V <sub>CCA</sub> = 1.2 V <sup>(2)</sup>                                                                      |                            | 43                 | 52                         | mA                 |

| I <sub>CCIO</sub>    | $V_{\text{CCIO}}$ and $V_{\text{PLL}}$ device active current                        | V <sub>CCIO</sub> = 1.8 V, V <sub>PLL</sub> = 1.8 V <sup>(2)</sup>                                           |                            | 32                 | 32                         | mA                 |

| SUSPEND_CCA          | V <sub>CCA</sub> device suspend current                                             | All data and clock lanes are in<br>ultra-low power state (ULPS) and<br>SUSPEND = 1                           |                            | 9.8                |                            | mA                 |

| SUSPEND_CC           | V <sub>CC</sub> device suspend current                                              | All data and clock lanes are in ultra-low power state (ULPS) and SUSPEND = 1                                 |                            | 9                  |                            | mA                 |

| SUSPEND_CCIO         | V <sub>CCIO</sub> and V <sub>PLL</sub> device suspend current                       | All data and clock lanes are in ultra-low power state (ULPS) and SUSPEND = 1                                 |                            | 1.16               |                            | mA                 |

| I <sub>EN_CCA</sub>  | V <sub>CCA</sub> shutdown current                                                   | EN = 0                                                                                                       |                            | 0.95               |                            | mA                 |

| I <sub>EN_CC</sub>   | V <sub>CC</sub> shutdown current                                                    | EN = 0                                                                                                       |                            | 2                  |                            | mA                 |

| I <sub>EN_CCIO</sub> | V <sub>CCIO</sub> and V <sub>PLL</sub> shutdown current                             | EN = 0                                                                                                       |                            | 0.038              |                            | mA                 |

| R <sub>EN</sub>      | EN control input resistor                                                           |                                                                                                              |                            | 150                |                            | $\mathbf{k}\Omega$ |

| ADDR, EN, SCL, SD    | A, DBP/N[3:0], DAP/N[3:1], DBCP/N, DAC                                              | P/N                                                                                                          |                            |                    |                            |                    |

| I <sub>LEAK</sub>    | Input failsafe leakage current                                                      | $V_{\rm CC}$ = 0; $V_{\rm CCIO}$ = 0 V. Input pulled up to $V_{\rm CCIO}$ max. DSI inputs pulled up to 1.3 V | - 40                       |                    | 40                         | μΑ                 |

| MIPI DSI INTERFAC    | E                                                                                   |                                                                                                              |                            |                    |                            |                    |

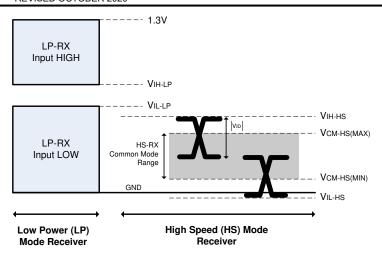

| V <sub>IH-LP</sub>   | LP receiver input high threshold                                                    | 0 10 7 5                                                                                                     | 880                        |                    |                            | mV                 |

| V <sub>IL-LP</sub>   | LP receiver input low threshold                                                     | - See 图 7-5                                                                                                  |                            |                    | 550                        | mV                 |

| V <sub>OH-LP</sub>   | LP transmitter high-level output voltage                                            |                                                                                                              | 1100                       |                    | 1300                       | mV                 |

| V <sub>OL-LP</sub>   | LP transmitter low-level output voltage                                             |                                                                                                              | - 50                       |                    | 50                         | mV                 |

| V <sub>IHCD</sub>    | LP Logic 1 contention threshold                                                     |                                                                                                              | 450                        |                    |                            | mV                 |

| V <sub>ILCD</sub>    | LP Logic 0 contention threshold                                                     |                                                                                                              |                            |                    | 200                        | mV                 |

| V <sub>ID</sub>      | HS differential input voltage                                                       |                                                                                                              | 70                         |                    | 270                        | mV                 |

| V <sub>IDT</sub>     | HS differential input voltage threshold                                             |                                                                                                              |                            |                    | 50                         | mV                 |

| V <sub>IL-ULPS</sub> | LP receiver input low threshold; ultra-low power state (ULPS)                       |                                                                                                              |                            |                    | 300                        | mV                 |

| V <sub>CM-HS</sub>   | HS common mode voltage; steady-state                                                |                                                                                                              | 70                         |                    | 330                        | mV                 |

| Δ V <sub>CM-HS</sub> | HS common mode peak-to-peak<br>variation including symbol delta<br>and interference |                                                                                                              |                            |                    | 100                        | mV                 |

| V <sub>IH-HS</sub>   | HS single-ended input high voltage                                                  | Can [4] 7 F                                                                                                  |                            |                    | 460                        | mV                 |

| V <sub>IL-HS</sub>   | HS single-ended input low voltage                                                   | - See 图 7-5                                                                                                  | - 40                       |                    |                            | mV                 |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLLSEH2

10

Product Folder Links: SN65DS/86

over operating free-air temperature range (unless otherwise noted)

|                                   | PARAMETER                                                                                 | TEST CONDITIONS                                                                 | MIN   | TYP <sup>(1)</sup> | MAX   | UNIT  |

|-----------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|--------------------|-------|-------|

| V <sub>TERM-EN</sub>              | HS termination enable; single-<br>ended input voltage (both Dp AND<br>Dn apply to enable) | Termination is switched simultaneous for Dn and Dp                              |       |                    | 450   | mV    |

| R <sub>DIFF-HS</sub>              | HS mode differential input impedance                                                      |                                                                                 | 80    |                    | 125   | Ω     |

| DisplayPort MAIN LINK             |                                                                                           |                                                                                 |       |                    | 1     |       |

| V <sub>TX_DC_CM</sub>             | Output common mode voltage                                                                |                                                                                 | 0     |                    | 2     | V     |

| V <sub>TX_AC_CM_HBR_RBR</sub>     | TX AC common mode voltage for HBR and RBR.                                                |                                                                                 |       |                    | 20    | mVRMS |

| V <sub>TX_AC_CM_HBR2</sub>        | TX AC common mode voltage for HBR2                                                        |                                                                                 |       |                    | 30    | mVRMS |

| V <sub>TX_DIFFPP_LVL0</sub>       | Differential peak-to-peak output voltage level 0                                          | Based on default state of V0_P0_VOD register                                    | 300   | 400                | 460   | mV    |

| V <sub>TX_DIFFPP_LVL1</sub>       | Differential peak-to-peak output voltage level 1                                          | Based on default state of V1_P0_VOD register                                    | 450   | 600                | 690   | mV    |

| V <sub>TX_DIFFPP_LVL2</sub>       | Differential peak-to-peak output voltage level 2                                          | Based on default state of V2_P0_VOD register                                    | 600   | 800                | 920   | mV    |

| V <sub>TX_DIFFPP_LVL3</sub>       | Differential peak-to-peak output voltage level 3                                          | Based on default state of V3_P0_VOD register. Level 3 is not enabled by default | 600   | 800                | 920   | mV    |

| V <sub>TX_PRE_RATIO_0</sub>       | Pre-emphasis level 0                                                                      |                                                                                 | 0     | 0                  | 0     | dB    |

| V <sub>TX_PRE_RATIO_1</sub>       | Pre-emphasis level 1                                                                      |                                                                                 | 2.8   | 3.5                | 4.2   | dB    |

| V <sub>TX_PRE_RATIO_2</sub>       | Pre-emphasis level 2                                                                      |                                                                                 | 4.8   | 6.0                | 7.2   | dB    |

| V <sub>TX_PRE_RATIO_3</sub>       | Pre-emphasis level 3                                                                      | Level 3 is not enabled by default                                               | 4.8   | 6.0                | 7.2   | dB    |

| V <sub>TX_PRE_POST2_RATIO_0</sub> | Post-cursor2 level 0                                                                      |                                                                                 | 0     | 0                  | 0     | dB    |

| V <sub>TX_PRE_POST2_RATIO_1</sub> | Post-cursor2 level 1                                                                      |                                                                                 | - 1.1 | - 0.9              | - 0.7 | dB    |

| V <sub>TX_PRE_POST2_RATIO_2</sub> | Post-cursor2 level 2                                                                      |                                                                                 | - 2.3 | - 1.9              | - 1.5 | dB    |

| V <sub>TX_PRE_POST2_RATIO_3</sub> | Post-cursor2 level 3                                                                      | Level 3 is not enabled by default                                               | - 3.7 | - 3.1              | - 2.5 | dB    |

| I <sub>TX_SHORT</sub>             | TX short circuit current limit                                                            |                                                                                 |       |                    | 50    | mA    |

| R <sub>TX_DIFF</sub>              | Differential impedance                                                                    |                                                                                 | 80    | 100                | 120   | Ω     |

| C <sub>AC_COUPLING</sub>          | AC coupling capacitor                                                                     |                                                                                 | 75    |                    | 200   | nF    |

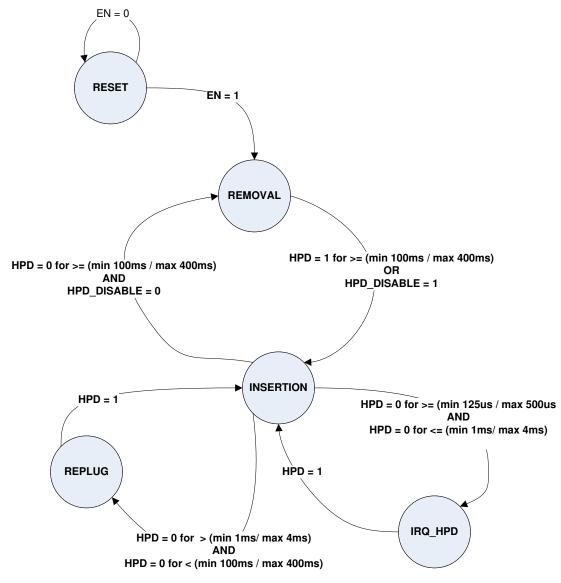

| DisplayPort HPD                   |                                                                                           |                                                                                 |       |                    | '     |       |

| V <sub>HPD_PLUG</sub>             | Hot plug detection threshold                                                              | Measured at 51-k Ω series resistor.                                             | 2.2   |                    |       | V     |

| V <sub>HPD_UNPLUG</sub>           | Hot unplug detection threshold                                                            | Measured at 51-k Ω series resistor.                                             |       |                    | 0.8   | V     |

| RHPDPD                            | HPD internal pulldown resistor                                                            |                                                                                 | 51    | 60                 | 69    | kΩ    |

| DisplayPort AUX INTER             | RFACE                                                                                     |                                                                                 |       |                    |       |       |

| V <sub>AUX_DIFF_PP_TX</sub>       | Peak-to-peak differential voltage at transmit pins                                        | V <sub>AUX_DIFF_PP</sub> = 2 ×  V <sub>AUXP</sub> - V <sub>AUXN</sub>           | 0.18  |                    | 1.38  | V     |

| V <sub>AUX_DIFF_PP_RX</sub>       | Peak-to-peak differential voltage at receive pins                                         | V <sub>AUX_DIFF_PP</sub> = 2 ×  V <sub>AUXP</sub> - V <sub>AUXN</sub>           | 0.18  |                    | 1.36  | V     |

| R <sub>AUX_TERM</sub>             | AUX channel termination DC resistance                                                     |                                                                                 |       | 100                |       | Ω     |

| V <sub>AUX_DC_CM</sub>            | AUX channel DC common mode voltage                                                        |                                                                                 | 0     |                    | 1.2   | V     |

| V <sub>AUX_TURN_CM</sub>          | AUX channel turnaround common-<br>mode voltage                                            |                                                                                 |       |                    | 0.3   | V     |

| I <sub>AUX_SHORT</sub>            | AUX Channel short circuit current limit                                                   |                                                                                 |       |                    | 90    | mA    |

| C <sub>AUX</sub>                  | AUX AC-coupling capacitor                                                                 |                                                                                 | 75    |                    | 200   | nF    |

<sup>(1)</sup> All typical values are at V<sub>CC</sub> = 1.2 V, V<sub>CCA</sub> = 1.2 V, V<sub>CCIO</sub> = 1.8 V, and V<sub>PLL</sub> = 1.8 V, and T<sub>A</sub> = 25°C

(2) Maximum condition: WQXGA 60 fps Dual-Link 2xDP at HBR2, PLL enabled; typical condition: WUXGA 60 fps 1xDP at HBR2, PLL enabled

# 7.6 Timing Requirements

|                         |                                                                                                                                   | MIN                                   | MAX                                   | UNIT |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|------|

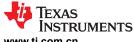

| Power-up For I          | DPPLL_CLK_SRC = REFCLK, See 图 7-1                                                                                                 |                                       |                                       |      |

| td1                     | V <sub>CC/A</sub> stable before V <sub>CCIO</sub> /V <sub>PLL</sub> stable                                                        | 0                                     |                                       | μs   |

| td2                     | V <sub>CC/A</sub> and V <sub>CCIO</sub> /V <sub>PLL</sub> stable before EN assertion                                              | 100                                   |                                       | μs   |

| td3                     | REFCLK active and stable before EN assertion                                                                                      | 0                                     |                                       | μs   |

| td4                     | GPIO[3:1] stable before EN assertion                                                                                              | 0                                     |                                       | ns   |

| td5                     | GPIO[3:1] stable after EN assertion                                                                                               | 5                                     |                                       | μs   |

| td6                     | LP11 state on DSI channels A and B before EN assertion                                                                            | 0                                     |                                       | ns   |

| td7                     | LP11 state on DSI channels A and B after EN assertion <sup>(1)</sup>                                                              | 100                                   |                                       | μs   |

| t <sub>VCC_RAMP</sub>   | V <sub>CC</sub> supply ramp requirements                                                                                          | 0.2                                   | 100                                   | ms   |

| t <sub>VCCA_RAMP</sub>  | V <sub>CCA</sub> supply ramp requirements                                                                                         | 0.2                                   | 100                                   | ms   |

| t <sub>VCCIO_RAMP</sub> | V <sub>CCIO</sub> supply ramp requirements                                                                                        | 0.2                                   | 100                                   | ms   |

| t <sub>VPLL_RAMP</sub>  | V <sub>PLL</sub> supply ramp requirements                                                                                         | 0.2                                   | 100                                   | ms   |

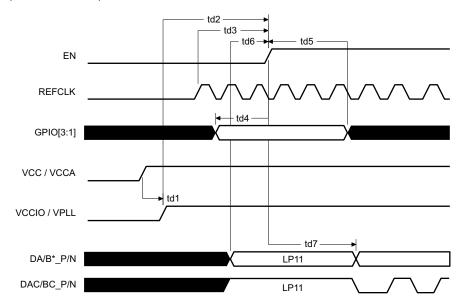

| Power-up For I          | DPPLL_CLK_SRC = DACP/N, See 🛚 7-2                                                                                                 |                                       |                                       |      |

| td1                     | V <sub>CC/A</sub> stable before V <sub>CCIO</sub> /V <sub>PLL</sub> stable                                                        | 0                                     |                                       | μs   |

| td2                     | V <sub>CC/A</sub> and V <sub>CCIO</sub> /V <sub>PLL</sub> stable before EN assertion                                              | 100                                   |                                       | μs   |

| td3                     | REFCLK low before EN assertion                                                                                                    | 10                                    |                                       | μs   |

| td4                     | GPIO[3:1] stable before EN assertion                                                                                              | 0                                     |                                       | ns   |

| td5                     | GPIO[3:1] stable after EN assertion                                                                                               | 5                                     |                                       | μs   |

| td6                     | LP11 state on DSI channels A and B before EN assertion                                                                            | 0                                     |                                       | ns   |

| td7                     | LP11 state on DSI channels A and B after EN assertion <sup>(1)</sup>                                                              | 100                                   |                                       | μs   |

| td8                     | DACP/N active and stable before DP_PLL_EN bit is set.                                                                             | 100                                   |                                       | μs   |

| t <sub>VCC_RAMP</sub>   | V <sub>CC</sub> supply ramp requirements                                                                                          | 0.2                                   | 100                                   | ms   |

| t <sub>VCCA_RAMP</sub>  | V <sub>CCA</sub> supply ramp requirements                                                                                         | 0.2                                   | 100                                   | ms   |

| t <sub>VCCIO_RAMP</sub> | V <sub>CCIO</sub> supply ramp requirements                                                                                        | 0.2                                   | 100                                   | ms   |

| t <sub>VPLL_RAMP</sub>  | V <sub>PLL</sub> supply ramp requirements                                                                                         | 0.2                                   | 100                                   | ms   |

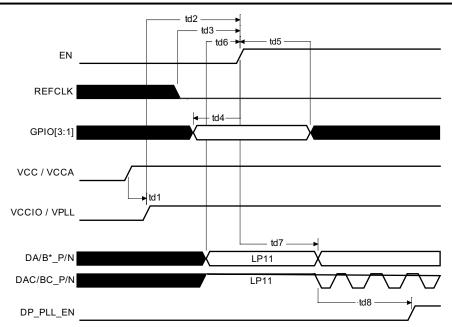

| SUSPEND Tim             | ing Requirements, See 图 7-3                                                                                                       |                                       | 1                                     |      |

| td1                     | LP11 or ULPS on DSI channel A and B before assertion of SUSPEND.                                                                  | 200                                   |                                       | ns   |

| td2                     | Delay from SUSPEND asserted to DisplayPort Main Link powered off.                                                                 | 2 × t <sub>REFCLK</sub>               |                                       |      |

| td3                     | REFCLK active hold time after assertion of SUSPEND                                                                                | 4 × t <sub>REFCLK</sub>               |                                       |      |

| td4                     | REFCLK active setup time before deassertion of SUSPEND.                                                                           | 100                                   |                                       | ns   |

| td5                     | Delay from SUSPEND deasserted to DisplayPort Main Link active and transmitting IDLE pattern. Semi-Auto Link Training is NOT used. |                                       | 20 + (1155<br>× t <sub>REFCLK</sub> ) | μs   |

| td6                     | LP11 state or ULPS on DSI channels A and B after SUSPEND deassertion                                                              | 20 + (1155<br>× t <sub>REFCLK</sub> ) |                                       | μs   |

<sup>(1)</sup> Access to SN65DSI86 CFR from I<sup>2</sup>C or DSI allowed after td7.

# 7.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                                             | PARAMETER                                                                                                               | TEST CONDITIONS                                 | MIN      | TYP <sup>(1)</sup> | MAX      | UNIT               |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------|--------------------|----------|--------------------|

| MIPI DSI INTERFAC                           | DE                                                                                                                      |                                                 |          |                    |          |                    |

| t <sub>GS</sub>                             | DSI LP glitch suppression pulse width                                                                                   |                                                 |          |                    | 300      | ps                 |

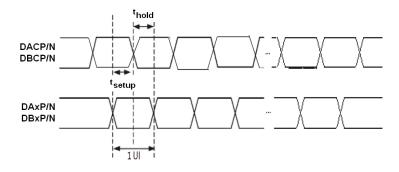

| t <sub>HS-SETUP</sub>                       | DSI HS data to clock setup time                                                                                         |                                                 | 0.2      |                    |          | UI                 |

| t <sub>HS-HOLD</sub>                        | DSI HS clock to data hold time                                                                                          |                                                 | 0.2      |                    |          | UI                 |

| DisplayPort MAIN L                          | LINK                                                                                                                    |                                                 |          |                    |          |                    |

| F <sub>BR7</sub>                            | Bit rate 7                                                                                                              |                                                 | 5.37138  | 5.4                | 5.40162  | Gbps               |

| F <sub>BR6</sub>                            | Bit rate 6                                                                                                              |                                                 | 4.297104 | 4.32               | 4.321296 | Gbps               |

| F <sub>BR5</sub>                            | Bit rate 5                                                                                                              |                                                 | 3.222828 | 3.24               | 3.240972 | Gbps               |

| F <sub>BR4</sub>                            | Bit rate 4                                                                                                              |                                                 | 2.68569  | 2.7                | 2.70081  | Gbps               |

| F <sub>BR3</sub>                            | Bit rate 3                                                                                                              |                                                 | 2.417121 | 2.43               | 2.430729 | Gbps               |

| F <sub>BR2</sub>                            | Bit rate 2                                                                                                              |                                                 | 2.148552 | 2.16               | 2.160648 | Gbps               |

| F <sub>BR1</sub>                            | Bit rate 1                                                                                                              |                                                 | 1.611414 | 1.62               | 1.620486 | Gbps               |

| UI <sub>BR7</sub>                           | Unit interval for BR7                                                                                                   | High limit = +300 ppm.<br>Low limit = -5300 ppm |          | 185                |          | ps                 |

| UI <sub>BR6</sub>                           | Unit interval for BR6                                                                                                   | High limit = +300 ppm.<br>Low limit = -5300 ppm |          | 231.5              |          | ps                 |

| UI <sub>BR5</sub>                           | Unit interval for BR5                                                                                                   | High limit = +300 ppm.<br>Low limit = -5300 ppm |          | 308.6              |          | ps                 |

| UI <sub>BR4</sub>                           | Unit interval for BR4                                                                                                   | High limit = +300 ppm.<br>Low limit = -5300 ppm |          | 370.4              |          | ps                 |

| UI <sub>BR3</sub>                           | Unit interval for BR3                                                                                                   | High limit = +300 ppm.<br>Low limit = -5300 ppm |          | 411.5              |          | ps                 |

| UI <sub>BR2</sub>                           | Unit interval for BR2                                                                                                   | High limit = +300 ppm.<br>Low limit = -5300 ppm |          | 463                |          | ps                 |

| UI <sub>BR1</sub>                           | Unit interval for BR1                                                                                                   | High limit = +300 ppm.<br>Low limit = -5300 ppm |          | 617.3              |          | ps                 |

| t <sub>ERC_L0</sub>                         | Differential output rise or fall time with DP_ERC set to 0                                                              |                                                 | 50       | 61                 | 80       | ps                 |

| t <sub>ERC_L1</sub>                         | Differential output rise or fall time with DP_ERC set to 1                                                              |                                                 | 74       | 95                 | 115      | ps                 |

| t <sub>ERC_L2</sub>                         | Differential output rise or fall time with DP_ERC set to 2                                                              |                                                 | 108      | 123                | 146      | ps                 |

| t <sub>ERC_L3</sub>                         | Differential output rise or fall time with DP_ERC set to 3                                                              |                                                 | 136      | 153                | 168      | ps                 |

| t <sub>TX_RISE_FALL</sub><br>_MISMATCH      | Lane intra-pair output skew at TX pins                                                                                  |                                                 |          |                    | 5%       |                    |

| t <sub>INTRA_SKEW</sub>                     | Intra-pair differential skew                                                                                            |                                                 |          |                    | 20       | ps                 |

| t <sub>INTER_SKEW</sub>                     | Inter-pair differential skew                                                                                            |                                                 |          |                    | 100      | ps                 |

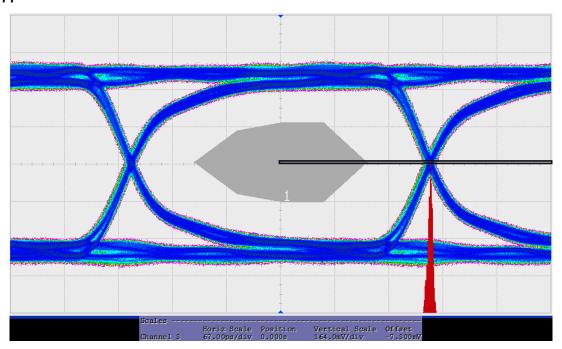

| t <sub>TX_EYE_HBR2</sub>                    | Minimum TX eye width at TX package pins for HBR2 <sup>(2)</sup>                                                         |                                                 | 0.73     |                    |          | UI <sub>HBR2</sub> |

| t <sub>TX_EYE_MED_TO</sub><br>_MAX_JIT_HBR2 | Maximum time between the jitter median and maximum deviation from the median at TX package pins for HBR2 <sup>(2)</sup> |                                                 |          |                    | 0.135    | UI <sub>HBR2</sub> |

| t <sub>TX_EYE_HBR</sub>                     | Minimum TX eye width at TX package pins for HBR <sup>(2)</sup>                                                          |                                                 | 0.72     |                    |          | UI <sub>HBR</sub>  |

| t <sub>TX_EYE_MED_TO</sub><br>_MAX_JIT_HBR  | Maximum time between the jitter median and maximum deviation from the median at TX package pins for HBR <sup>(2)</sup>  |                                                 |          |                    | 0.147    | UI <sub>HBR</sub>  |

| t <sub>TX_EYE_RBR</sub>                     | Minimum TX eye width at TX package pins for RBR <sup>(2)</sup>                                                          |                                                 | 0.82     |                    |          | UI <sub>RBR</sub>  |

over operating free-air temperature range (unless otherwise noted)

|                                         | PARAMETER                                                                                                              | TEST CONDITIONS | MIN     | TYP <sup>(1)</sup> | MAX    | UNIT              |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------|---------|--------------------|--------|-------------------|

| t <sub>TX_EYE_MED_TO</sub> _MAX_JIT_RBR | Maximum time between the jitter median and maximum deviation from the median at TX package pins for RBR <sup>(2)</sup> |                 |         | '                  | 0.09   | UI <sub>RBR</sub> |

| t <sub>XSSC_AMP</sub>                   | Link clock down-spreading                                                                                              |                 | 0%      |                    | 0.5%   |                   |

| t <sub>SSC_FREQ</sub>                   | Link clock down-spreading frequency                                                                                    |                 | 30      |                    | 33     | kHz               |

| DisplayPort AUX IN                      | TERFACE                                                                                                                |                 |         |                    |        |                   |

| UI <sub>MAN</sub>                       | Manchester transaction unit interval                                                                                   |                 | 0.4     |                    | 0.6    | μs                |

| t <sub>auxjitter_tx</sub>               | Cycle-to-cycle jitter time at transmit pins                                                                            |                 |         |                    | 0.08   | UI <sub>MAN</sub> |

| t <sub>auxjitter_rx</sub>               | Cycle-to-cycle jitter time at receive pins                                                                             |                 |         |                    | 0.04   | UI <sub>MAN</sub> |

| REFCLK                                  |                                                                                                                        |                 | •       |                    |        |                   |

| f <sub>REFCLK</sub>                     | REFCLK frequency. supported frequencies: 12 MHz, 19.2 MHz, 26 MHz, 27 MHz, 38.4 MHz                                    |                 | 12      |                    | 38.4   | MHz               |

| t <sub>RISEFALL</sub>                   | REFCLK rise or fall time                                                                                               | 10% to 90%      | 100 ps  |                    | 23     | ns                |

| t <sub>REFCLK</sub>                     | REFCLK period                                                                                                          |                 | 26.0417 |                    | 83.333 | ns                |

| t <sub>pj</sub>                         | REFCLK peak-to-peak phase jitter                                                                                       |                 |         |                    | 50     | ps                |

| Duty                                    | REFCLK duty cycle                                                                                                      |                 | 40%     | 50%                | 60%    |                   |

- (1)

- All typical values are at  $V_{CC}$  = 1.2 V and  $T_A$  = 25 °C BR refers to BR1; HBR refers to BR; HBR2 refers to BR7. (2)

图 7-1. Power-Up Timing Definitions for DPPLL\_CLK\_SRC = REFCLK

图 7-2. Power-Up Timing Definitions for DPPLL\_CLK\_SRC = DACP/N

图 7-3. SUSPEND Timing Definitions

图 7-4. DSI HS Mode Receiver Timing Definitions

图 7-5. DSI Receiver Voltage Definitions

# 8 Detailed Description

### 8.1 Overview

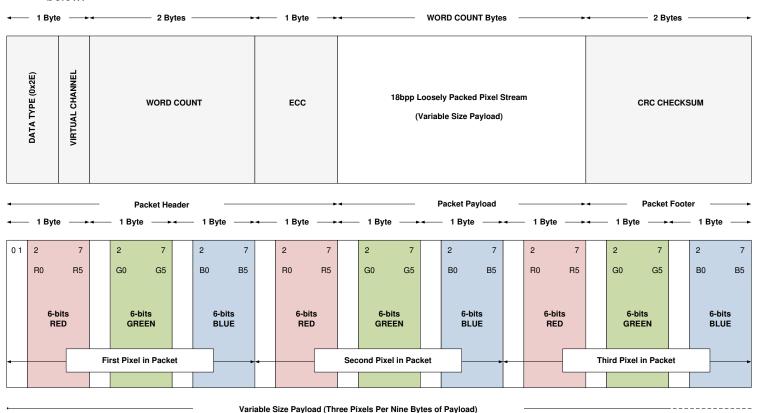

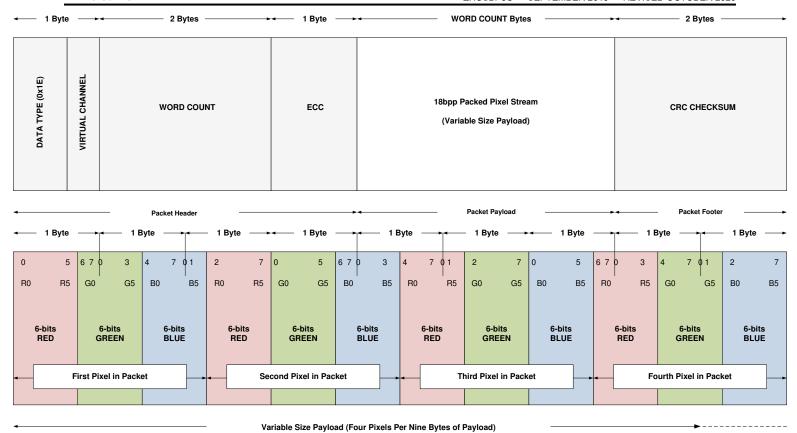

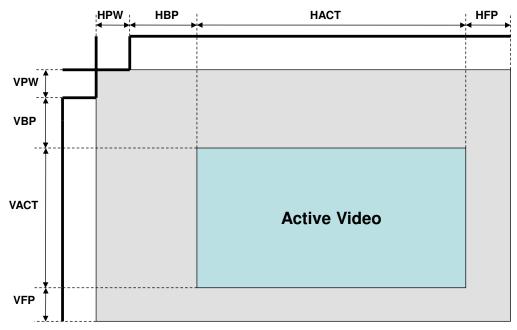

The SN65DSI86 is a MIPI DSI to eDP bridge, and supports MIPI DSI RGB 18 bpp (loosely packed or tightly packed) and 24 bpp formats. The SN65DSI86 packetizes the 18-bpp or 24-bpp RGB data received on the DSI inputs and transmits over the eDP interface in SST format at data rates up to 5.4 Gbps. With support of up to eight DSI lanes at 1.5 Gbps per DSI lane, and four lanes of eDP at speeds up to 5.4 Gbps, the SN65DSI86 is perfectly suited for both standard high definition (HD) displays as well has ultra HD displays like 4K2K.

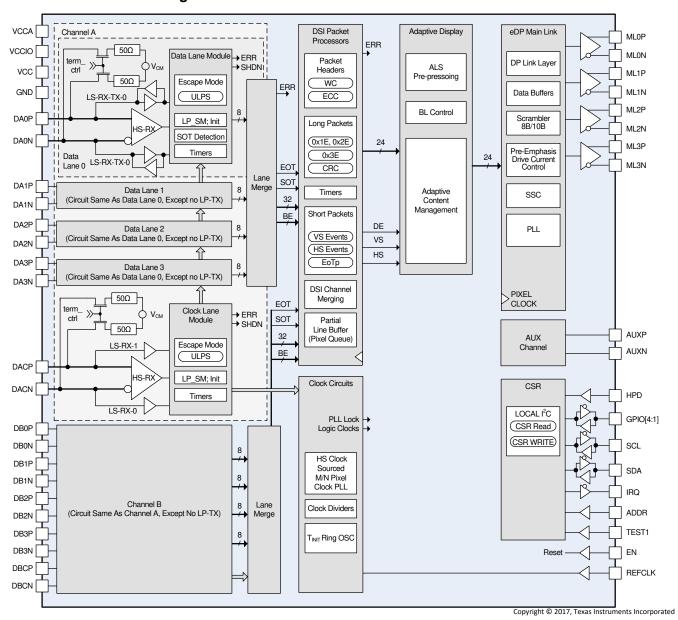

## 8.2 Functional Block Diagram

#### 8.3 Feature Description

### 8.3.1 MIPI Dual DSI Interface

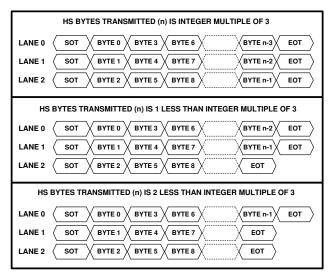

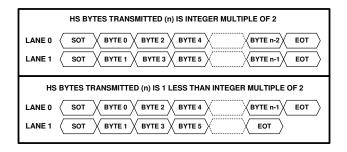

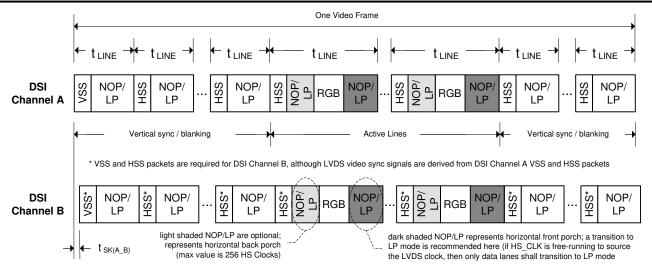

The SN65DSI86 supports two 4-lane MIPI DSI inputs called DSIA and DSIB. Each lane supports a data rate up to 1.5 Gbps and can accept 18 bpp or 24 bpp RGB data. When only using the DSIA channel, the SN65DSI86 can support an maximum video stream rate of 6 Gbps that easily supports HD resolutions. If larger resolutions

Copyright © 2023 Texas Instruments Incorporated

like 4K2K are required, the maximum stream rate can be increased to 12 Gbps by using both DSIA and DSIB channels. When using both DSIA and DSIB channels, the SN65DSI86 requires the pixels on each active line to be broken up into either odd pixels on DSIA and even pixels on DSIB, or left half of line on DSIA and right half of line on DSIB.

The SN65DSI86 also supports DSI generic read and write operation. Using DSI generic reads and writes, the external GPU can configure the SN65DSI86 internal registers and communicate with eDP panels. The DSI generic read and writes is also used for panel self refresh (PSR). In order to use the PSR feature, the eDP panel must support PSR and the GPU must support generating generic reads and writes without stopping the video stream. Generic reads and writes must be performed during video blanking time in order for PSR to work properly.

### 8.3.2 Embedded DisplayPort Interface

The SN65DSI86 supports Single-Stream Transport (SST) mode over one, two, or 4 lanes at data rates of 1.62 Gbps (RBR), 2.16 Gbps, 2.43 Gbps, 2.7 Gbps (HBR), 3.24 Gbps, 4.32 Gbps, and 5.4 Gbps (HBR2). All lanes operate at the same rate (SN65DSI86 does not support each lane being at a different data rate). The SN65DSI86 allows for software control of the eDP interfaces voltage swing level, pre-emphasis level, and SSC. Because the SN65DSI86 is a DSI to eDP bridge, the SN65DSI86 only supports eDP panels which support ASSR (Alternate Scrambler Seed Reset). Software must either through the DSI interface or I<sup>2</sup>C interface enable ASSR in the eDP panel before attempting to link train. See the #9.2.1.2.5 section on how to enable ASSR in the eDP panel.

# 8.3.3 General-Purpose Input and Outputs

The SN65DSI86 provides four GPIO pins that can be configured as an input or output. The GPIOs default to input but can be changed to output by changing the appropriate GPIO register.

#### **GPIO Functions:**

- 1. Input

- 2. Output

- 3. SUSPEND Input (powers down entire chip except for I<sup>2</sup>C interface)

- 4. PWM

- DSIA VSYNC

- DSIA HSYNC

### 8.3.3.1 GPIO REFCLK and DSIA Clock Selection

The clock source for the SN65DSI86 is derived from one of two sources: REFCLK pin or DACP/N pins. On the rising edge of EN, the sampled state of GPIO[3:1] as well as the detection of a clock on REFCLK pin is used to determine the clock source and the frequency of that clock. After the EN, software through the I<sup>2</sup>C interface can change the configuration of REFCLK FREQ, and CHA DSI CLK RANGE registers for the case where GPIO[3:1] sampled state does not represent the intended functionality. Because the clock source is determined at the assertion of EN, software can not change the clock source. See 表 8-1 for GPIO to REFCLK or DACP/N frequency combinations.

表 8-1. GPIO REFCLK or DACP/N Frequency Selection(3)(2)(1)

| GPIO[3:1] | REFCLK FREQUENCY<br>(DPPLL_CLK_SRC = 0) | DACP/N CLOCK FREQUENCY<br>(DPPLL_CLK_SRC = 1) | REFCLK_FREQ |

|-----------|-----------------------------------------|-----------------------------------------------|-------------|

| 3' b000   | 12 MHz                                  | 468 MHz (DSIACLK / 39 = 12 MHz )              | 0x0         |

| 3' b001   | 19.2 MHz                                | 384 MHz (DSIACLK / 20 = 19.2 MHz)             | 0x1         |

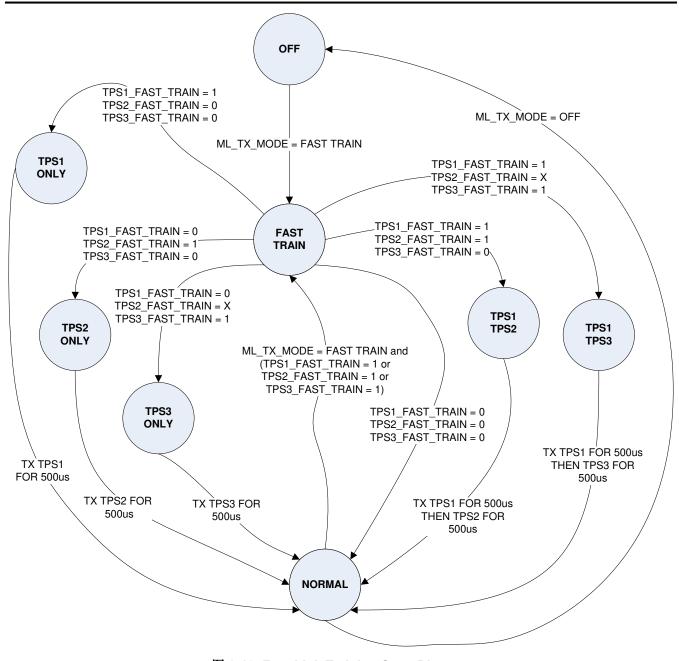

| 3' b010   | 26 MHz                                  | 416 MHz (DSIACLK / 16 = 26 MHz)               | 0x2         |