TPD8S300A

ZHCSIE7 - JUNE 2018

## TPD8S300A USB Type-C™端口保护器: V<sub>BUS</sub> 短路过压和 IEC ESD 保护

#### 1 特性

- 4 通道 V<sub>BUS</sub> 短路过压保护(CC1、CC2、SBU1、SBU2 或 CC1、CC2、DP、DM): 耐受 24V 直流电

- 8 通道 IEC 61000-4-2 ESD 保护(CC1、CC2、SBU1、SBU2、DP\_T、DM\_T、DP\_B、DM\_B)

- CC1 和 CC2 过压保护 FET 可处理最高 600mA 的 电流,因此可支持 V<sub>CONN</sub> 电源电流通过

- 集成 CC 死电池电阻器,可用于处理移动设备中的 死电池用例

- 相较 TPD8S300 所具有的优势

- 更高的死电池性能

- USB Type-C 端口在 IEC 61000-4-2 ESD 冲击 期间保持连接

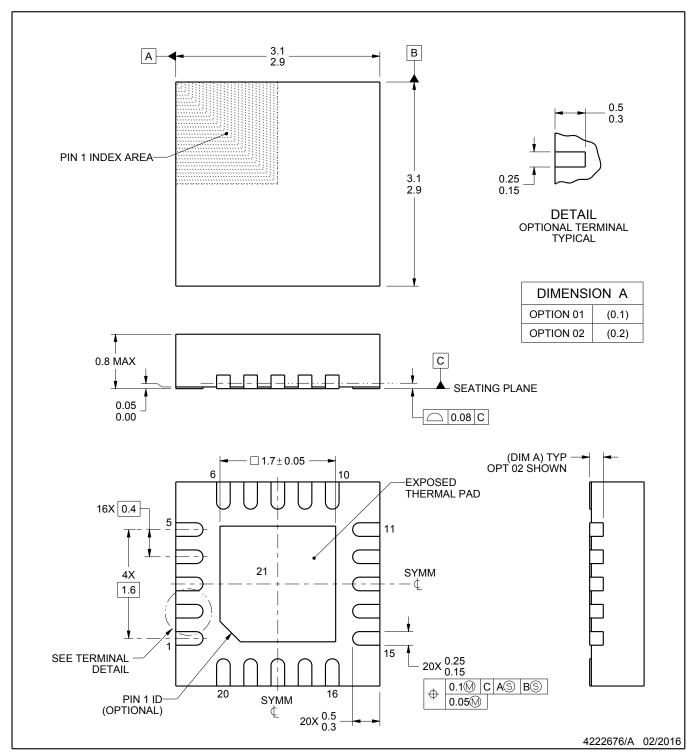

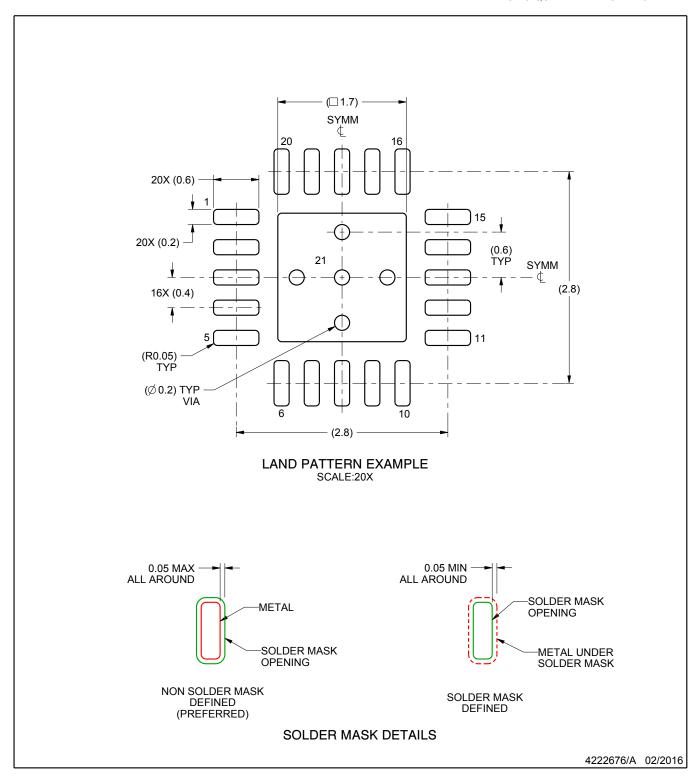

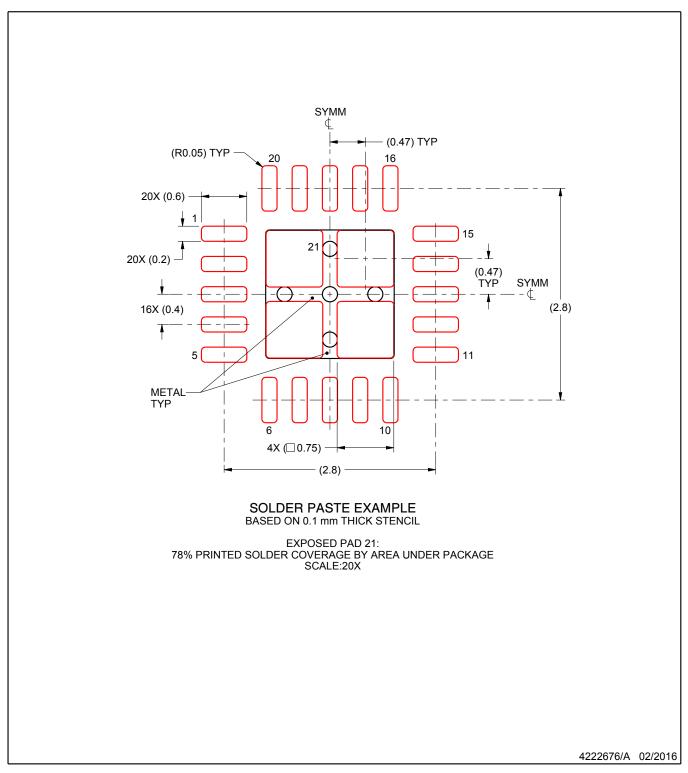

- 3mm × 3mm WQFN 封装

### 2 应用

- 笔记本电脑

- 平板电脑

- 智能手机

- 监视器和电视

- 扩展坞

#### 3 说明

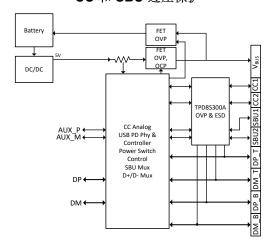

TPD8S300A 是一种单芯片 USB Type-C 端口保护器件,可提供 20V V<sub>BUS</sub> 短路过压保护和 IEC ESD 保护。

自从 USB Type-C 连接器发布以来,市场上已经发布了很多不符合 USB Type-C 规格的 USB Type-C 产品和配件。其中的一个示例就是仅在 V<sub>BUS</sub> 线路上布设20V 电压的 USB Type-C 电力输送适配器。USB Type-C 的另一个问题是,由于此小型连接器中的各引脚极为靠近,因此连接器的机械扭转和滑动可能使引脚短路。这可能导致 20V V<sub>BUS</sub> 与 CC 和 SBU 引脚短路。此外,由于 Type-C 连接器中的各引脚极为靠近,所以存在碎屑和水气导致 20V V<sub>BUS</sub> 引脚与 CC 和SBU 引脚短路的严重问题。

这些非理想的设备和机械事件使得 CC 和 SBU 引脚必须能够承受 20V 的电压,即使这些引脚仅在 5V 或更低电压下工作。通过在 CC 和 SBU 引脚上提供过压保护,TPD8S300A 可以使 CC 和 SBU 引脚耐受 20V 的电压,同时不会干扰正常工作。该器件将高压 FET 串联放置在 SBU 和 CC 线路上。当在这些线路上检测到高于 OVP 阈值的电压时,高压开关被打开,并且将系统的其余部分与连接器上存在的高压状态隔离。

最后,大多数系统都需要为其外部引脚应用 IEC 61000-4-2 系统级 ESD 保护。TPD8S300A 为 CC1、CC2、SBU1、SBU2、DP 和 DM 引脚集成了 IEC 61000-4-2 ESD 保护,无需再在连接器上(外部)放置高电压 TVS 二极管。

#### 器件信息<sup>(1)</sup>

| 器件型号      | 封装        | 封装尺寸 (标称值)      |

|-----------|-----------|-----------------|

| TPD8S300A | WQFN (20) | 3.00mm × 3.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

### CC 和 SBU 过压保护

#### CC 和 DP/DM 过压保护

A

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | 特性           | 9 A<br>9 9<br>10 F<br>11 L<br>1<br>12 # | .3 Feature Description |    |

|---------------------------------|--------------|-----------------------------------------|------------------------|----|

| •                               | 8.1 Overview | 13 柞                                    | 几械、封装和可订购信息            | 28 |

|                                 |              |                                         |                        |    |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| 日期      | 修订版本 | 说明      |  |  |

|---------|------|---------|--|--|

| 2018年6月 | *    | 最初发布版本。 |  |  |

## 5 Device Comparison Table

| Part Number | Over Voltage Protected Channels                    | IEC 61000-4-2 ESD Protected<br>Channels             |

|-------------|----------------------------------------------------|-----------------------------------------------------|

| TPD6S300A   | 4-Ch (CC1, CC2, SBU1, SBU2 or<br>CC1, CC2, DP, DM) | 6-Ch (CC1, CC2, SBU1, SBU2, DP, DM)                 |

| TPD8S300A   | 4-Ch (CC1, CC2, SBU1, SBU2 or CC1, CC2, DP, DM)    | 8-Ch (CC1, CC2, SBU1, SBU2, DP_T, DM_T, DP_B, DM_B) |

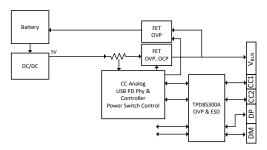

## 6 Pin Configuration and Functions

#### RUK Package 20-Pin WQFN Top View

## **Pin Functions**

| PIN |           |         | DESCRIPTION                                                                                                                                                                                                           |

|-----|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME      | I TPE\" | DESCRIPTION                                                                                                                                                                                                           |

| 1   | C_SBU1    | I/O     | Connector side of the SBU1 OVP FET. Connect to either SBU pin of the USB Type-C connector. Alternatively, connect to either USB2.0 pin of the USB Type-C connector to protect the USB2.0 pins instead of the SBU pins |

| 2   | C_SBU2    | I/O     | Connector side of the SBU2 OVP FET. Connect to either SBU pin of the USB Type-C connector. Alternatively, connect to either USB2.0 pin of the USB Type-C connector to protect the USB2.0 pins instead of the SBU pins |

| 3   | VBIAS     | Power   | Pin for ESD support capacitor. Place a 0.1-µF capacitor on this pin to ground                                                                                                                                         |

| 4   | C_CC1     | I/O     | Connector side of the CC1 OVP FET. Connect to either CC pin of the USB Type-C connector                                                                                                                               |

| 5   | C_CC2     | I/O     | Connector side of the CC2 OVP FET. Connect to either CC pin of the USB Type-C connector                                                                                                                               |

| 6   | RPD_G2    | I/O     | Short to C_CC2 if dead battery resistors are needed. If dead battery resistors are not needed, short pin to GND                                                                                                       |

| 7   | RPD_G1    | I/O     | Short to C_CC1 if dead battery resistors are needed. If dead battery resistors are not needed, short pin to GND                                                                                                       |

| 8   | GND       | GND     | Ground                                                                                                                                                                                                                |

| 9   | FLT       | 0       | Open drain for fault reporting                                                                                                                                                                                        |

| 10  | $V_{PWR}$ | Power   | 2.7-V to 3.6-V power supply                                                                                                                                                                                           |

| 11  | CC2       | I/O     | System side of the CC2 OVP FET. Connect to either CC pin of the CC/PD controller                                                                                                                                      |

<sup>(1)</sup> I = input, O = output, I/O = input and output, GND = ground, P = power

## Pin Functions (continued)

|     | PIN         | TYPE <sup>(1)</sup> | DEGODIDATION                                                                                                                                                                                                |

|-----|-------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        | IYPE                | DESCRIPTION                                                                                                                                                                                                 |

| 12  | CC1         | I/O                 | System side of the CC1 OVP FET. Connect to either CC pin of the CC/PD controller                                                                                                                            |

| 13  | GND         | GND                 | Ground                                                                                                                                                                                                      |

| 14  | SBU2        | I/O                 | System side of the SBU2 OVP FET. Connect to either SBU pin of the SBU MUX. Alternatively, connect to either USB2.0 pin of the USB2.0 Phy when protecting the USB2.0 pins instead of protecting the SBU pins |

| 15  | SBU1        | I/O                 | System side of the SBU1 OVP FET. Connect to either SBU pin of the SBU MUX. Alternatively, connect to either USB2.0 pin of the USB2.0 Phy when protecting the USB2.0 pins instead of protecting the SBU pins |

| 16  | D4          | I/O                 | USB2.0 IEC ESD protection. Connect to any of the USB2.0 pins of the USB Type-C connector                                                                                                                    |

| 17  | D3          | I/O                 | USB2.0 IEC ESD protection. Connect to any of the USB2.0 pins of the USB Type-C connector                                                                                                                    |

| 18  | GND         | GND                 | Ground                                                                                                                                                                                                      |

| 19  | D2          | I/O                 | USB2.0 IEC ESD protection. Connect to any of the USB2.0 pins of the USB Type-C connector                                                                                                                    |

| 20  | D1          | I/O                 | USB2.0 IEC ESD protection. Connect to any of the USB2.0 pins of the USB Type-C connector                                                                                                                    |

| _   | Thermal Pad | GND                 | Internally connected to GND. Used as a heatsink. Connect to the PCB GND plane                                                                                                                               |

ZHCSIE7 - JUNE 2018 www.ti.com.cn

## **Specifications**

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                |                              | MIN  | MAX | UNIT |

|------------------|--------------------------------|------------------------------|------|-----|------|

| V                | Input voltage                  | $V_{PWR}$                    | -0.3 | 4   | V    |

| VI               | Input voltage                  | RPD_G1, RPD_G2               | -0.3 | 24  | V    |

| V                | Output voltage                 | FLT                          | -0.3 | 6   | V    |

| Vo               | Output voltage                 | VBIAS                        | -0.3 | 24  | V    |

|                  |                                | D1, D2                       | -0.3 | 6   | V    |

| $V_{IO}$         | I/O voltage                    | CC1, CC2, SBU1, SBU2         | -0.3 | 6   | V    |

|                  |                                | C_CC1, C_CC2, C_SBU1, C_SBU2 | -0.3 | 24  | V    |

| $T_A$            | Operating free air temperature | ·                            | -40  | 85  | °C   |

| T <sub>stg</sub> | Storage temperature            |                              | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings—JEDEC Specification

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±2000 V may actually have higher performance.

#### 7.3 ESD Ratings—IEC Specification

|                    |                                        |                                     |                   | VALUE  | UNIT |

|--------------------|----------------------------------------|-------------------------------------|-------------------|--------|------|

|                    | Electrostatic discharge <sup>(1)</sup> | IEC 61000-4-2, C CC1, C CC2, D1, D2 | Contact discharge | ±8000  |      |

| V                  |                                        |                                     | Air-gap discharge | ±15000 | .,   |

| V <sub>(ESD)</sub> |                                        |                                     | Contact discharge | ±6000  | V    |

|                    |                                        | IEC 61000-4-2, C_SBU1, C_SBU2       | Air-gap discharge | ±15000 |      |

<sup>(1)</sup> Tested on the TPD6S300 EVM connected to the TPS65982 EVM.

### 7.4 Recommended Operating Conditions

|                    |                           |                                                                               | MIN  | NOM | MAX  | UNIT |

|--------------------|---------------------------|-------------------------------------------------------------------------------|------|-----|------|------|

| .,                 | land vallana              | V <sub>PWR</sub>                                                              | 2.7  | 3.3 | 3.6  | V    |

| VI                 | Input voltage             | RPD_G1, RPD_G2                                                                | 0    |     | 5.5  | V    |

| Vo                 | Output voltage            | FLT pull-up resistor power rail                                               | 2.7  |     | 5.5  | V    |

| V <sub>IO</sub>    |                           | D1, D2                                                                        | -0.3 |     | 5.5  | V    |

|                    | I/O voltage               | CC1, CC2, C_CC1, C_CC2                                                        | 0    |     | 5.5  | V    |

|                    |                           | SBU1, SBU2, C_SBU1, C_SBU2                                                    | 0    |     | 4.3  | V    |

| I <sub>VCONN</sub> | V <sub>CONN</sub> current | Current flowing into CC1/2 and flowing out of C_CC1/2, VCCx − VC_CCx ≤ 250 mV |      |     | 600  | mA   |

| I <sub>VCONN</sub> | V <sub>CONN</sub> current | Current flowing into CC1/2 and flowing out of C_CC1/2, T <sub>J</sub> ≤ 105°C |      |     | 600  | mA   |

| I <sub>VCONN</sub> | V <sub>CONN</sub> current | Current flowing into CC1/2 and flowing out of C_CC1/2, T <sub>J</sub> ≤ 85°C  |      |     | 1.25 | Α    |

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ±500 V may actually have higher performance.

#### TEXAS INSTRUMENTS

## **Recommended Operating Conditions (continued)**

over operating free-air temperature range (unless otherwise noted)

|                                    |                                  | MIN | NOM | MAX | UNIT |

|------------------------------------|----------------------------------|-----|-----|-----|------|

|                                    | FLT pullup resistance            | 1.7 |     | 300 | kΩ   |

| External components <sup>(1)</sup> | VBIAS capacitance <sup>(2)</sup> |     | 0.1 |     | μF   |

|                                    | V <sub>PWR</sub> capacitance     | 0.3 | 1   |     | μF   |

<sup>1)</sup> For recommended values for capacitors and resistors, the typical values assume a component placed on the board near the pin. Minimum and maximum values listed are inclusive of manufacturing tolerances, voltage derating, board capacitance, and temperature variation. The effective value presented must be within the minimum and maximums listed in the table.

#### 7.5 Thermal Information

|                      |                                              | TPD8S300A  |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RUK (WQFN) | UNIT |

|                      |                                              | 20 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 45.2       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 48.8       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 17.1       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.6        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 17.1       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 3.7        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.6 Electrical Characteristics

|                        | PARAMETER                                                                                                                                    | TEST CONDITIONS                                                                                                                                             | MIN  | TYP | MAX | UNIT |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| CC OVP SWI             | TCHES                                                                                                                                        |                                                                                                                                                             |      |     |     |      |

| В                      | On resistance of CC OVP FETs, T <sub>J</sub> ≤ 85°C                                                                                          | CCx = 5.5 V                                                                                                                                                 |      | 278 | 392 | mΩ   |

| R <sub>ON</sub>        | On resistance of CC OVP FETs, $T_J \le 105$ °C                                                                                               | CCx = 5.5 V                                                                                                                                                 |      | 278 | 415 | mΩ   |

| R <sub>ON(FLAT)</sub>  | On resistance flatness                                                                                                                       | Sweep CCx voltage between 0 V and 1.2 V                                                                                                                     |      |     | 5   | mΩ   |

| C <sub>ON_CC</sub>     | Equivalent on capacitance                                                                                                                    | Capacitance from C_CCx or CCx to GND when device is powered. VC_CCx/VCCx = 0 V to 1.2 V, f = 400 kHz                                                        | 60   | 74  | 120 | pF   |

| $R_{D}$                | Dead battery pull-down resistance<br>(only present when device is<br>unpowered). Effective resistance of<br>R <sub>D</sub> and FET in series | V_C_CCx = 2.6 V                                                                                                                                             | 4.1  | 5.1 | 6.1 | kΩ   |

| VTH_DB                 | Threshold voltage of the pulldown<br>FET in series with RD during dead<br>battery                                                            | I_CC = 80 μA                                                                                                                                                | 0.5  | 0.9 | 1.2 | V    |

| V <sub>OVPCC</sub>     | OVP threshold on CC pins                                                                                                                     | Place 5.5 V on C_CCx. Step up C_CCx until the FLT pin is asserted                                                                                           | 5.75 | 6   | 6.2 | V    |

| V <sub>OVPCC_HYS</sub> | Hysteresis on CC OVP                                                                                                                         | Place 6.5 V on C_CCx. Step down the voltage on C_CCx until the FLT pin is deasserted. Measure difference between rising and falling OVP threshold for C_CCx |      | 50  |     | mV   |

| BW <sub>ON</sub>       | On bandwidth single ended (-3 dB)                                                                                                            | Measure the –3-dB bandwidth from                                                                                                                            |      | 100 |     | MHz  |

<sup>(2)</sup> The VBIAS pin requires a minimum 35-V<sub>DC</sub> rated capacitor. A 50-V<sub>DC</sub> rated capacitor is recommended to reduce capacitance derating. See the *VBIAS Capacitor Selection* section for more information on selecting the VBIAS capacitor.

**Electrical Characteristics (continued)**

|                                  | PARAMETER                                                         | TEST CONDITIONS                                                                                                                                                     | MIN  | TYP  | MAX | UNIT |

|----------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| V <sub>STBUS_CC</sub>            | Short-to-VBUS tolerance on the CC pins                            | Hot-Plug C_CCx with a 1 meter USB Type C Cable, place a 30-Ω load on CCx                                                                                            |      |      | 24  | V    |

| V <sub>STBUS_CC_CL</sub>         | Short-to-VBUS system-side clamping voltage on the CC pins (CCx)   | Hot-Plug C_CCx with a 1 meter USB<br>Type C Cable. Hot-Plug voltage<br>C_CCx = 24 V. VPWR = 3.3 V. Place<br>a 30-Ω load on CCx                                      |      | 8    |     | V    |

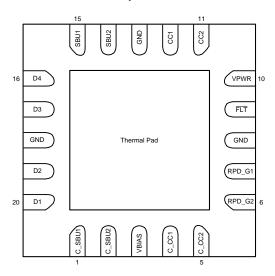

| SBU OVP SW                       | ITCHES                                                            |                                                                                                                                                                     |      |      |     |      |

| R <sub>ON</sub>                  | On resistance of SBU OVP FETs                                     | SBUx = 3.6 V. $-40^{\circ}$ C $\leq T_{J} \leq +85^{\circ}$ C                                                                                                       |      | 4    | 6.5 | Ω    |

| R <sub>ON(FLAT)</sub>            | On resistance flatness                                            | Sweep SBUx voltage between 0 V and 3.6 V. $-40^{\circ}$ C $\leq$ T <sub>J</sub> $\leq$ +85 $^{\circ}$ C                                                             |      | 0.7  | 1.5 | Ω    |

| $C_{ON\_SBU}$                    | Equivalent on capacitance                                         | Capacitance from SBUx or C_SBUx to GND when device is powered.  Measure at VC_SBUx/VSBUx = 0.3 V to 3.6 V                                                           |      | 6    |     | pF   |

| V <sub>OVPSBU</sub>              | OVP threshold on SBU pins                                         | Place 3.6 V on C_SBUx. Step up C_SBUx until the FLT pin is asserted                                                                                                 | 4.35 | 4.5  | 4.7 | V    |

| V <sub>OVPSBU_</sub> HYS         | Hysteresis on SBU OVP                                             | Place 5 V on C_CCx. Step down the voltage on C_CCx until the FLT pin is deasserted. Measure difference between rising and falling OVP threshold for C_SBUx          |      |      |     | mV   |

| BW <sub>ON</sub>                 | On bandwidth single ended (-3 dB)                                 | Measure the –3-dB bandwidth from C_SBUx to SBUx. Single ended measurement, 50-Ω system. Vcm = 0.1 V to 3.6 V                                                        |      | 1000 |     | MHz  |

| X <sub>TALK</sub>                | Crosstalk                                                         | Measure crosstalk at f = 1 MHz from SBU1 to C_SBU2 or SBU2 to C_SBU1. Vcm1 = 3.6 V, Vcm2 = 0.3 V. Be sure to terminate open sides to 50 $\Omega$                    |      | -80  |     | dB   |

| V <sub>STBUS_SBU</sub>           | Short-to-VBUS tolerance on the SBU pins                           | Hot-Plug C_SBUx with a 1 meter USB Type C Cable. Put a 100-nF capacitor in series with a 40-Ω resistor to GND on SBUx                                               |      |      | 24  | V    |

| V <sub>STBUS_SBU_C</sub><br>LAMP | Short-to-VBUS system-side clamping voltage on the SBU pins (SBUx) | Hot-Plug C_SBUx with a 1 meter USB Type C Cable. Hot-Plug voltage C_SBUx = 24 V. VPWR = 3.3 V. Put a 150-nF capacitor in series with a 40-Ω resistor to GND on SBUx |      | 8    |     | V    |

| POWER SUPI                       | PLY and LEAKAGE CURRENTS                                          | ,                                                                                                                                                                   |      |      |     |      |

| V <sub>PWR_UVLO</sub>            | V <sub>PWR</sub> under voltage lockout                            | Place 1 V on VPWR and raise voltage until SBU or CC FETs turnon                                                                                                     | 2.1  | 2.3  | 2.5 | V    |

| V <sub>PWR_UVLO_</sub> H<br>YS   | V <sub>PWR</sub> UVLO hysteresis                                  | Place 3 V on VPWR and lower voltage until SBU or CC FETs turnoff; measure difference between rising and falling UVLO to calculate hysteresis                        | 100  | 150  | 200 | mV   |

| I <sub>VPWR</sub>                | V <sub>PWR</sub> supply current                                   | VPWR = 3.3 V (typical), VPWR = 3.6 V (maximum). $-40^{\circ}$ C $\leq$ T <sub>J</sub> $\leq$ +85 $^{\circ}$ C.                                                      |      | 90   | 120 | μΑ   |

| I <sub>CC_LEAK</sub>             | Leakage current for CC pins when device is powered                | VPWR = 3.3 V, VC_CCx = 3.6 V, CCx pins are floating, measure leakage into C_CCx pins. Result must be same if CCx side is biased and C_CCx is left floating          |      |      | 5   | μA   |

## **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                           | PARAMETER                                                     | TEST CONDITIONS                                                                                                                                                                                                                         | MIN  | TYP | MAX  | UNIT |

|---------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| I <sub>SBU_LEAK</sub>     | Leakage current for SBU pins when device is powered           | VPWR = 3.3 V, VC_SBUx = 3.6 V, SBUx pins are floating, measure leakge into C_SBUx pins. Result must be same if SBUx side is biased and C_SBUx is left floating. $-40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq +85^{\circ}\text{C}$ |      |     | 3    | μΑ   |

| I <sub>C_CC_LEAK_OV</sub> | Leakage current for CC pins when device is in OVP             | VPWR = 0 V or 3.3 V, VC_CCx = 24 V, CCx pins are set to 0 V, measure leakage into C_CCx pins                                                                                                                                            |      |     | 1200 | μΑ   |

| I <sub>C_SBU_LEAK_O</sub> | Leakage current for SBU pins when device is in OVP            | VPWR = 0 V or 3.3 V, VC_SBUx = 24 V, SBUx pins are set to 0 V, measure leakage into C_SBUx pins                                                                                                                                         |      |     | 400  | μΑ   |

| I <sub>CC_LEAK_OVP</sub>  | Leakage current for CC pins when device is in OVP             | VPWR = 0 V or 3.3 V, VC_CCx = 24 V, CCx pins are set to 0 V, measure leakage out of CCx pins                                                                                                                                            |      |     | 30   | μΑ   |

| I <sub>SBU_LEAK_OVP</sub> | Leakage current for SBU pins when device is in OVP            | VPWR = 0 V or 3.3 V, VC_SBUx = 24 V, SBUx pins are set to 0 V, measure leakage out of SBUx pins                                                                                                                                         |      |     | 1    | μΑ   |

| I <sub>Dx_LEAK</sub>      | Leakage current for Dx pins                                   | V_Dx = 3.6 V, measure leakage into Dx pins                                                                                                                                                                                              |      |     | 1    | μΑ   |

| FLT PIN                   |                                                               |                                                                                                                                                                                                                                         |      |     |      |      |

| V <sub>OL</sub>           | Low-level output voltage                                      | $IOL = 3$ mA. Measure the voltage at the $\overline{FLT}$ pin                                                                                                                                                                           |      |     | 0.4  | V    |

| OVER TEMPE                | RATURE PROTECTION                                             | -                                                                                                                                                                                                                                       |      |     |      |      |

| T <sub>SD_RISING</sub>    | The rising over-temperature protection shutdown threshold     |                                                                                                                                                                                                                                         | 150  | 175 |      | °C   |

| T <sub>SD_FALLING</sub>   | The falling over-temperature protection shutdown threshold    |                                                                                                                                                                                                                                         | 130  | 140 |      | °C   |

| T <sub>SD_HYST</sub>      | The over-temperature protection shutdown threshold hysteresis |                                                                                                                                                                                                                                         |      | 35  |      | °C   |

| Dx ESD PRO                | FECTION                                                       |                                                                                                                                                                                                                                         |      |     |      |      |

| V <sub>RWM_POS</sub>      | Reverse stand-off voltage from Dx to GND                      | Dx to GND. I <sub>DX</sub> ≤ 1 μA                                                                                                                                                                                                       |      |     | 5.5  | V    |

| V <sub>RWM_NEG</sub>      | Reverse stand-off voltage from GND to Dx                      | GND to Dx                                                                                                                                                                                                                               |      |     | 0    | V    |

| V <sub>BR_POS</sub>       | Break-down voltage from Dx to GND                             | Dx to GND. I <sub>BR</sub> = 1 mA                                                                                                                                                                                                       | 7    |     |      | V    |

| V <sub>BR_NEG</sub>       | Break-down voltage from GND to Dx                             | GND to Dx. I <sub>BR</sub> = 8 mA                                                                                                                                                                                                       | 0.6  |     |      | V    |

| C <sub>IO</sub>           | Dx to GND or GND to Dx                                        | f = 1 MHz, VIO = 2.5 V                                                                                                                                                                                                                  |      | 1.7 |      | pF   |

| $\Delta C_{IO}$           | Differential capacitance between two Dx pins                  | f = 1 MHz, VIO = 2.5 V                                                                                                                                                                                                                  | 0.02 |     |      | pF   |

| R <sub>DYN</sub>          | Dynamic on-resistance Dx IEC clamps                           | Dx to GND or GND to Dx                                                                                                                                                                                                                  |      | 0.4 |      | Ω    |

## 7.7 Timing Requirements

|                           |                                                                                                                    | MIN  | NOM | MAX | UNIT |

|---------------------------|--------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| POWER-ON and O            | ff TIMINGS                                                                                                         |      |     |     |      |

| t <sub>ON_FET</sub>       | Time from crossing rising VPWR UVLO until CC and SBU OVP FETs are on                                               |      | 1.3 | 3.5 | ms   |

| t <sub>ON_FET_DB</sub>    | Time from crossing rising VPWR UVLO until CC and SBU OVP FETs are on and the dead battery resistors are turned off |      | 5.7 | 9.5 | ms   |

| dV <sub>PWR_OFF</sub> /dt | Minimum Slew rate allowed to guarantee CC and SBU FETs turnoff during a power off                                  | -0.5 |     |     | V/µs |

## **Timing Requirements (continued)**

|                                 |                                                                                                                                                                                                               | MIN | NOM  | MAX      | UNIT |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|----------|------|

| OVER VOLTAGE PROTE              | CTION                                                                                                                                                                                                         |     |      | <u>'</u> |      |

| tovp_response_cc                | OVP response time on the CC pins. Time from OVP asserted until OVP FETs turnoff                                                                                                                               |     | 70   |          | ns   |

| tovp_response_sbu               | OVP response time on the SBU pins. Time from OVP asserted until OVP FETs turnoff                                                                                                                              |     | 80   |          | ns   |

| tovp_recovery_cc_1_fet          | OVP recovery time on the CC pins. Once an OVP has occurred, the minimum time duration until the CC FETs turn back on. OVP must be removed for CC FETs to turn back on                                         |     | 0.93 |          | ms   |

| tovp_recovery_cc_1_db           | OVP recovery time on the CC pins. Once an OVP has occurred, the minimum time duration until the CC FETs turn back on and the dead battery resistors turn off. OVP must be removed for CC FETs to turn back on |     | 5    |          | ms   |

| tovp_recovery_sbu_1             | OVP recovery time on the SBU pins. Once an OVP has occurred, the minimum time duration until the SBU FETs turn back on. OVP must be removed for SBU FETs to turn back on                                      |     | 0.62 |          | ms   |

| tovp_recovery_cc_2_fet          | OVP recovery time on the CC pins. Time from OVP Removal until CC FETs turn back on, if device has been in OVP > 0.6 ms                                                                                        |     | 0.61 |          | ms   |

| tovp_recovery_cc_2_db           | OVP recovery time on the CC pins. Time from OVP Removal until CC FETs turn back on and dead battery resistors turn off, if device has been in OVP > 0.6 ms                                                    |     | 4.75 |          | ms   |

| tovp_recovery_sbu_2             | OVP recovery time on the SBU pins. Time from OVP Removal until SBU FETs turn back on, if device has been in OVP > 0.6 ms                                                                                      |     | 0.3  |          | ms   |

| t <sub>OVP_FLT_</sub> ASSERTION | Time from OVP asserted to FLT assertion                                                                                                                                                                       |     | 20   |          | μs   |

| tovp_flt_deassertion            | Time from CC FET turnon after an OVP to FLT deassertion                                                                                                                                                       |     | 4.1  |          | ms   |

# TEXAS INSTRUMENTS

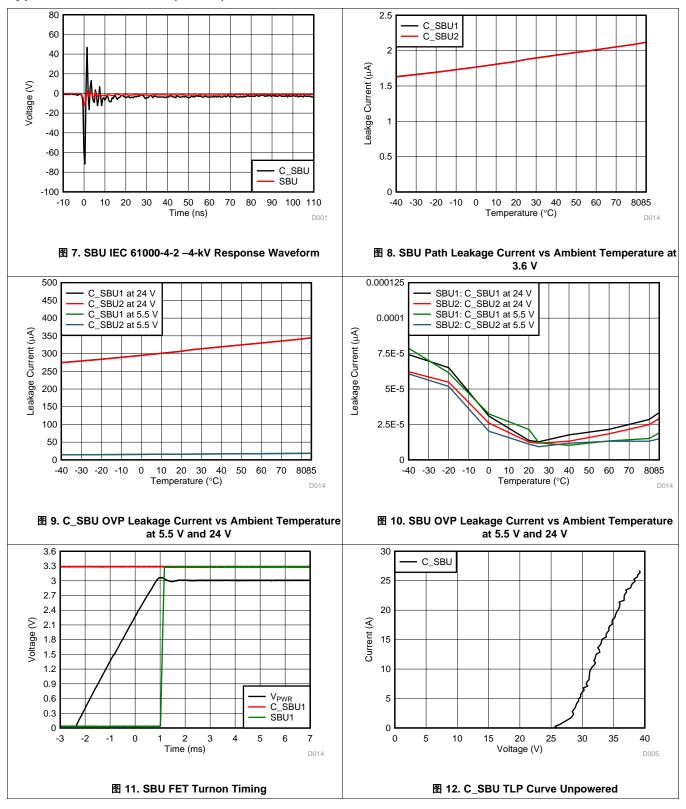

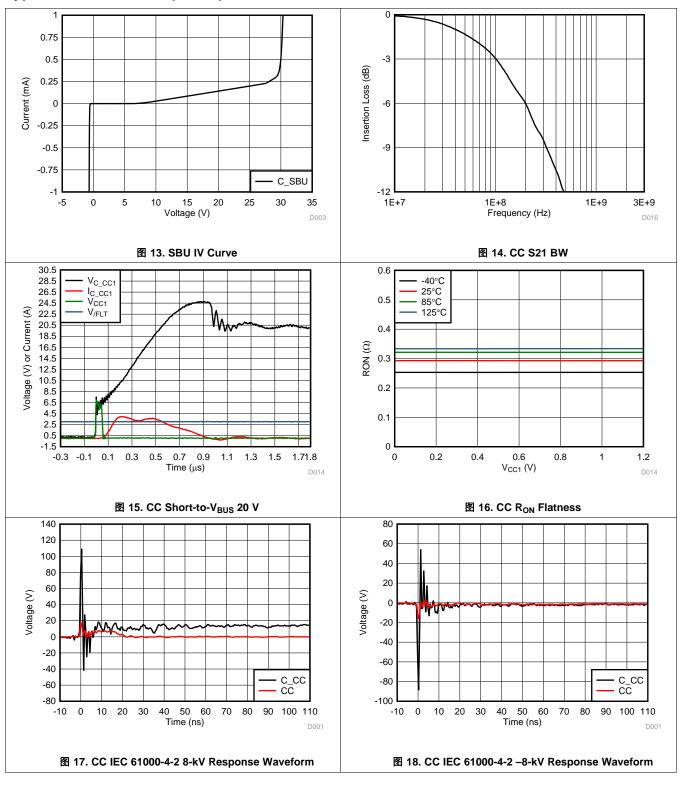

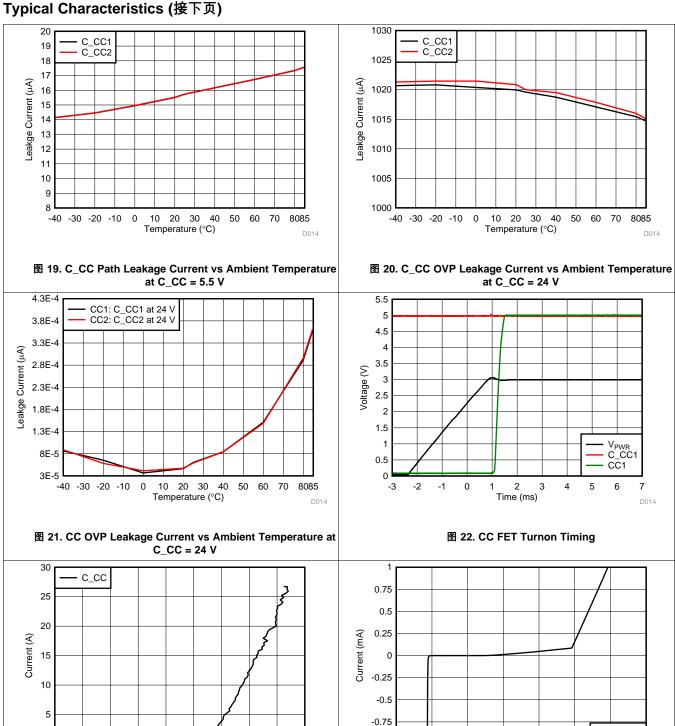

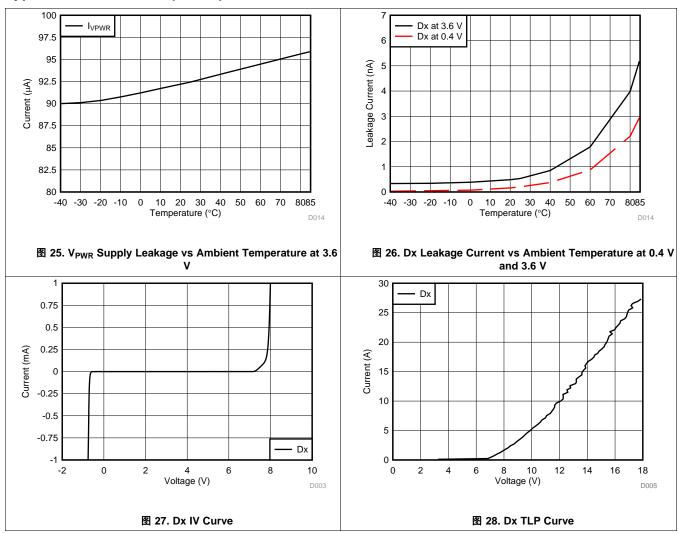

## 7.8 Typical Characteristics

ZHCSIE7-JUNE 2018 www.ti.com.cn

## Typical Characteristics (接下页)

# TEXAS INSTRUMENTS

## Typical Characteristics (接下页)

0 0

5

10

15

25

Voltage (V)

图 23. C\_CC TLP Curve Unpowered

35

45

D003

-5

0

Voltage (V)

图 24. C\_CC IV Curve

C\_CC

D003

# TEXAS INSTRUMENTS

## Typical Characteristics (接下页)

8 Detailed Description

## 8.1 Overview

www.ti.com.cn

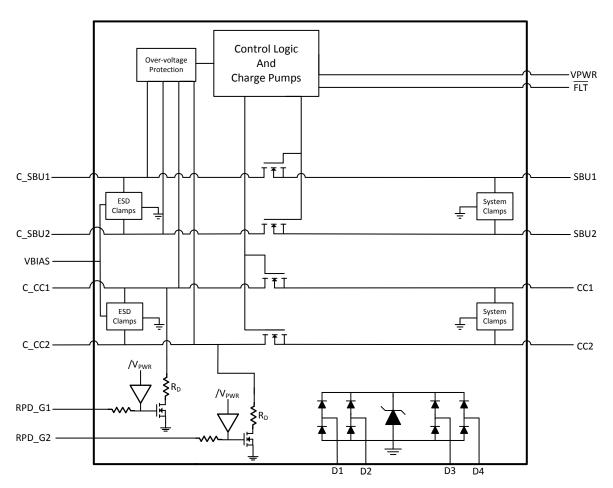

The TPD8S300A is a single chip USB Type-C port protection solution that provides 20-V Short-to- $V_{BUS}$  overvoltage and IEC ESD protection. Due to the small pin pitch of the USB Type-C connector and non-compliant USB Type-C cables and accessories, the  $V_{BUS}$  pins can get shorted to the CC and SBU pins inside the USB Type-C connector. Because of this short-to- $V_{BUS}$  event, the CC and SBU pins need to be 20-V tolerant, to support protection on the full USB PD voltage range. Even if a device does not support 20-V operation on  $V_{BUS}$ , non complaint adaptors can start out with 20-V  $V_{BUS}$  condition, making it necessary for any USB Type-C device to support 20 V protection. The TPD8S300A integrates four channels of 20-V Short-to- $V_{BUS}$  overvoltage

protection for the CC1, CC2, SBU1, and SBU2 pins of the USB Type-C connector.

Additionally, IEC 61000-4-2 system level ESD protection is required in order to protect a USB Type-C port from ESD strikes generated by end product users. The TPD8S300A integrates eight channels of IEC61000-4-2 ESD protection for the CC1, CC2, SBU1, SBU2, DP\_T (Top side D+), DM\_T (Top Side D-), DP\_B (Bottom Side D+), and DM\_B (Bottom Side D-) pins of the USB Type-C connector. This means IEC ESD protection is provided for all of the low-speed pins on the USB Type-C connector in a single chip in the TPD8S300A. Additionally, high-voltage IEC ESD protection that is 22-V DC tolerant is required for the CC and SBU lines in order to simultaneously support IEC ESD and Short-to-V<sub>BUS</sub> protection; there are not many discrete market solutions that can provide this kind of protection. This high-voltage IEC ESD diode is what the TPD8S300A integrates, specifically designed to guarantee it works in conjunction with the overvoltage protection FETs inside the device. This sort of solution is very hard to generate with discrete components.

ZHCSIE7 – JUNE 2018 www.ti.com.cn

# TEXAS INSTRUMENTS

#### 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

### 8.3 Feature Description

# 8.3.1 4-Channels of Short-to-V<sub>BUS</sub> Overvoltage Protection (CC1, CC2, SBU1, SBU2 Pins or CC1, CC2, DP, DM Pins): 24-V<sub>DC</sub> Tolerant

The TPD8S300A provides 4-channels of Short-to- $V_{BUS}$  Overvoltage Protection for the CC1, CC2, SBU1, and SBU2 pins (or the CC1, CC2, DP, and DM pins) of the USB Type-C connector. The TPD8S300A is able to handle 24- $V_{DC}$  on its C\_CC1, C\_CC2, C\_SBU1, and C\_SBU2 pins. This is necessary because according to the USB PD specification, with  $V_{BUS}$  set for 20-V operation, the  $V_{BUS}$  voltage is allowed to legally swing up to 21 V and 21.5 V on voltage transitions from a different USB PD  $V_{BUS}$  voltage. The TPD8S300A builds in tolerance up to 24- $V_{BUS}$  to provide margin above this 21.5-V specification to be able to support USB PD adaptors that may break the USB PD specification.

When a short-to- $V_{BUS}$  event occurs, ringing happens due to the RLC elements in the hot-plug event. With very low resistance in this RLC circuit, ringing up to twice the settling voltage can appear on the connector. More than 2x ringing can be generated if any capacitor on the line derates in capacitance value during the short-to- $V_{BUS}$  event. This means that more than 44 V could be seen on a USB Type-C pin during a Short-to- $V_{BUS}$  event. The TPD8S300A has built in circuit protection to handle this ringing. The diode clamps used for IEC ESD protection also clamp the ringing voltage during the short-to- $V_{BUS}$  event to limit the peak ringing to approximately 30 V. Additionally, the overvoltage protection FETs integrated inside the TPD8S300A are 30-V tolerant, therefore being capable of supporting the high-voltage ringing waveform that is experienced during the short-to- $V_{BUS}$  event. The well designed combination of voltage clamps and 30-V tolerant OVP FETs insures the TPD8S300A can handle Short-to- $V_{BUS}$  hot-plug events with hot-plug voltages as high as 24- $V_{DC}$ .

## Feature Description (接下页)

The TPD8S300A has an extremely fast turnoff time of 70 ns typical. Furthermore, additional voltage clamps are placed after the OVP FET on the system side (CC1, CC2, SBU1, SBU2) pins of the TPD8S300A, to further limit the voltage and current that are exposed to the USB Type-C CC/PD controller during the 70 ns interval while the OVP FET is turning off. The combination of connector side voltage clamps, OVP FETs with extremely fast turnoff time, and system side voltage clamps all work together to insure the level of stress seen on a CC1, CC2, SBU1, or SBU2 pin during a short-to-V<sub>BUS</sub> event is less than or equal to an HBM event. This is done by design, as any USB Type-C CC/PD controller will have built in HBM ESD protection.

The SBU OVP FETs where designed with a 1-GHz bandwidth to be able to be used to protect the DP, DM (USB2.0) pins in addition to the SBU pins. Some systems designers also prefer to protect the DP, DM pins from Short-to- $V_{BUS}$  events due to the potential for moisture/water in the connector to short the  $V_{BUS}$  pins to DP, DM pins. This can be especially applicable in cases where the end equipment with a USB Type-C connector is trying to be made water-proof. If desiring to protect the DP, DM pins on the USB Type-C connector from a Short-to- $V_{BUS}$  event, connect the C\_SBUx pins to the DP, DM pins on the USB Type-C connector, and the SBUx pins to the USB2.0 pins of the system device being protected from the Short-to- $V_{BUS}$  event.

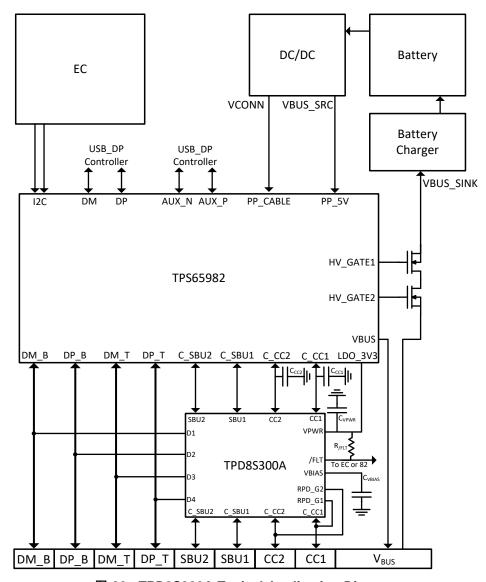

图 29. TPD8S300A Protecting the TPS65982 During a Short-to-V<sub>BUS</sub> Event

# 8.3.2 8-Channels of IEC 61000-4-2 ESD Protection (CC1, CC2, SBU1, SBU2, DP\_T, DM\_T, DP\_B, DM\_B Pins)

The TPD8S300A integrates 8-Channels of IEC 61000-4-2 system level ESD protection for the CC1, CC2, SBU1, SBU2, DP\_T (Top side D+), DM\_T (Top Side D-), DP\_B (Bottom Side D+), and DM\_B (Bottom Side D-) pins. USB Type-C ports on end-products need system level IEC ESD protection in order to provide adequate protection for the ESD events that the connector can be exposed to from end users. The TPD8S300A integrates IEC ESD protection for all of the low-speed pins on the USB Type-C connector in a single chip. Also note, that while the RPD\_Gx pins are not individually rated for IEC ESD, when they are shorted to the C\_CCx pins, the C\_CCx pins provide protection for both the C\_CCx pins and the RPD\_Gx pins. Additionally, high-voltage IEC ESD protection that is 24-V DC tolerant is required for the CC and SBU lines in order to simultaneously support IEC ESD and Short-to-V<sub>BUS</sub> protection; there are not many discrete market solutions that can provide this kind of protection. The TPD8S300A integrates this type of high-voltage ESD protection so a system designer can meet both IEC ESD and Short-to-V<sub>BUS</sub> protection requirements in a single device.

## TEXAS INSTRUMENTS

#### Feature Description (接下页)

#### 8.3.3 CC1, CC2 Overvoltage Protection FETs 600 mA Capable for Passing VCONN Power

The CC pins on the USB Type-C connector serve many functions; one of the functions is to be a provider of power to active cables. Active cables are required when desiring to pass greater than 3 A of current on the V<sub>BUS</sub> line or when the USB Type-C port uses the super-speed lines (TX1+, TX2-, RX1+, RX1-, TX2+, TX2-, RX2+, RX2-). When CC is configured to provide power, it is called VCONN. VCONN is a DC voltage source in the range of 3 V to 5.5 V. If supporting VCONN, a VCONN provider must be able to provide 1 W of power to a cable; this translates into a current range of 200 mA to 333 mA (depending on your VCONN voltage level). Additionally, if operating in a USB PD alternate mode, greater power levels are allowed on the VCONN line.

When a USB Type-C port is configured for VCONN and using the TPD8S300A, this VCONN current flows through the OVP FETs of the TPD8S300A. Therefore, the TPD8S300A has been designed to handle these currents and have an RON low enough to provide a specification compliant VCONN voltage to the active cable. The TPD8S300A is designed to handle up to 600 mA of DC current to allow for alternate mode support in addition to the standard 1 W required by the USB Type-C specification.

#### 8.3.4 CC Dead Battery Resistors Integrated for Handling the Dead Battery Use Case in Mobile Devices

An important feature of USB Type-C and USB PD is the ability for this connector to serve as the sole power source to mobile devices. With support up to 100 W, the USB Type-C connector supporting USB PD can be used to power a whole new range of mobile devices not previously possible with legacy USB connectors.

When the USB Type-C connector is the sole power supply for a battery powered device, the device must be able to charge from the USB Type-C connector even when its battery is dead. In order for a USB Type-C power adapter to supply power on  $V_{BUS}$ , RD pulldown resistors must be exposed on the CC pins. These RD resistors are typically included inside a USB Type-C CC/PD controller. However, when the TPD8S300A is used to protect the USB Type-C port, the OVP FETs inside the device isolate these RD resistors in the CC/PD controller when the mobile device has no power. This is because when the TPD8S300A has no power, the OVP FETs are turned off to guarantee overvoltage protection in a dead battery condition. Therefore, the TPD8S300A integrates high-voltage, dead battery RD pull-down resistors to allow dead battery charging simultaneously with high-voltage OVP protection.

If dead battery support is required, short the RPD\_G1 pin to the C\_CC1 pin, and short the RPD\_G2 pin to the C\_CC2 pin. This connects the dead battery resistors to the connector CC pins. When the TPD8S300A is unpowered, and the RP pull-up resistor is connected from a power adaptor, this RP pull-up resistor activates the RD resistor inside the TPD8S300A. This enables V<sub>BUS</sub> to be applied from the power adaptor even in a dead battery condition. Once power is restored back to the system and back to the TPD8S300A on its VPWR pin, the TPD8S300A turns ON its OVP FETs in 3.5 ms and then turns OFF its dead battery RD. The TPD8S300A first turns ON its CC OVP FETs fully, and then removes its dead battery RDs. This is to make sure the PD controller RD is fully exposed before removing the RD of the TPD8S300A. This is to help ensure the USB Type-C source remains attached because a USB Type-C sink must have an RD present on CC at all times to guarantee according to the USB Type-C spec that the USB Type-C source remains attached.

If desiring to power the CC/PD controller during dead battery mode and if the CC/PD Controller is configured as a DRP, it is critical that the TPD8S300A be powered before or at the same time that the CC/PD controller is powered. It is also critical that when unpowered, the CC/PD controller also expose its dead battery resistors. When the TPD8S300A gets powered, it exposes the CC pins of the CC/PD controller within 3.5 ms, and then removes its own RD dead battery resistors. Once the TPD8S300A turns on, the RD pull-down resistors of the CC/PD controller must be present immediately, in order to guarantee the power adaptor connected to power the dead battery device keeps its  $V_{BUS}$  turned on. If the power adaptor does not see RD present, it can disconnect  $V_{BUS}$ . This removes power from the device with its battery still not sufficiently charged, which consequently removes power from the CC/PD controller and the TPD8S300A. Then the RD resistors of the TPD8S300A are exposed again, and connects the power adaptor's  $V_{BUS}$  to start the cycle over. This creates an infinite loop, never or very slowly charging the mobile device.

#### Feature Description (接下页)

If the CC/PD Controller is configured for DRP and has started its DRP toggle before the TPD8S300A turns on, this DRP toggle is unable to guarantee that the power adaptor does not disconnect from the port. Therefore, it is recommended if the CC/PD controller is configured for DRP, that its dead battery resistors be exposed as well, and that they remain exposed until the TPD8S300A turns on. This is typically accomplished by powering the TPD8S300A at the same time as the CC/PD controller when powering the CC/PD controller in dead battery operation. When protecting the TPS6598x family of PD controllers with TPD8S300A, this is accomplished by powering TPD8S300A from TPS6598x's LDO\_3V3 pin (connect TPS6598x's LDO\_3V3 pin to TPD8S300A's  $V_{\rm PWR}$  pin).

If dead battery charging is not required in your application, connect the RPD G1 and RPD G2 pins to ground.

#### 8.3.5 Advantages over TPD8S300

### 8.3.5.1 Improved Dead Battery Performance

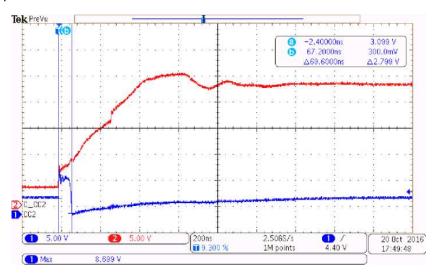

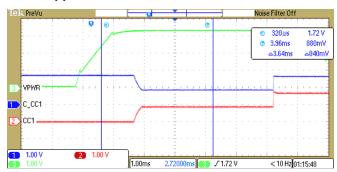

The TPD8S300A has improved dead battery performance over TPD8S300. In the TPD8S300 when the device is first powered (VPWR pin goes from 0V to 3.3V), the CC RD dead battery resistors are disabled at the same time the CC OVP FETs are enabled. This leads to a small ~400us time window where the CC pin can float up above the SRC.RD voltage threshold because the CC OVP FETs are still too resistive for the source to detect RD from the USB-PD controller. If the tSRCDisconnect debounce time of the USB Type-C source is less than ~400us, this could cause a USB Type-C disconnect for the source port during the dead battery boot-up event. Many USB Type-C Sources do not have a tSRCDisconnect debounce time less than ~400us; however, the USB Type-C spec allows the tSRCDisconnect time to be as low as 0ms, so some USB Type-C sources may have a tSRCDisconnect debounce time that is less than ~400us. TPD8S300A solves this problem. When the TPD8S300A is first powered (VPWR pin goes from 0V to 3.3V), TPD8S300A waits for its CC OVP FETs to be completely ON before it removes its RD dead battery resistors. This guarantees that an RD resistor will always be present on the CC line during the dead battery boot-up, and that the USB Type-C source's CC voltage will always stay in the SRC.RD range; therefore, even if a source had a tSRCDisconnect debounce time of 0ms, it will remain connected. See 32 for an oscilloscope capture of TPD8S300A's proper dead battery boot-up behavior.

### 8.3.5.2 USB Type-C Port Stays Connected during an IEC 61000-4-2 ESD Strike

The TPD8S300A will also make sure the USB Type-C ports stay connected, even during an IEC 61000-4-2 ESD strike, whereas the TPD8S300 has the potential to cause a USB Type-C port disconnect during an IEC 61000-4-2 ESD strike. In TPD8S300, in some PCB layouts an IEC 61000-4-2 ESD strike would cause TPD8S300 to go into the OVP state. In TPD8S300, the CC OVP recovery time was 21ms minimum. This means that if an OVP happened in TPD8S300, a USB-C disconnect was guaranteed to happen, because the maximum USB Type-C port disconnect time for sources and sinks is 20ms max in the USB Type-C specification. However, in TPD8S300A, the CC OVP recovery time is 0.93ms typical. For TPD8S300A, the OVP FET will turn back ON much faster than a sinks minimum disconnect time, which is 10ms. So even if an IEC 61000-4-2 ESD strike causes an OVP in TPD8S300A, the new CC OVP FET recovery time of 0.93ms will not cause a disconnect on the USB Type-C port for a sink.

For a source port connected to a sink with a TPD8S300A, if an IEC 61000-4-2 ESD strike occurs that causes an OVP event, even an OVP recovery time of 0.93ms could cause a disconnect, because for source USB Type-C ports, they have a minimum disconnect time of 0ms in the USB Type-C specification. So the CC OVP FET in TPD8S300A would open up and hide the PD controllers RD for 0.93ms, causing a potential for a disconnect on the source USB Type-C port. To solve this problem, TPD8S300A turns on its dead battery RD resistor in an OVP event caused by an IEC 61000-4-2 ESD strike while the CC OVP FET is OFF. This makes it so even during this OVP event caused by IEC ESD, the source port connected to the sink port with TPD8S300A will always see an RD resistor. Therefore, even if the source port has an extremely low tSrcDisconnect time close to 0ms, it will remain connected because an RD resistor is always present on its CC pin.

#### 8.3.6 3-mm × 3-mm WQFN Package

The TPD8S300A comes in a small, 3-mm × 3-mm WQFN package, greatly reducing the size of implementing a similar protection solution discretely. The WQFN package allows support for a wider range of PCB designs.

# TEXAS INSTRUMENTS

#### 8.4 Device Functional Modes

表 1 describes all of the functional modes for the TPD8S300A. The "X" in the below table are "do not care" conditions, meaning any value can be present within the absolute maximum ratings of the datasheet and maintain that functional mode. Also note the D1, D2, D3, and D4 pins are not listed, because these pins have IEC ESD protection diodes that are always present, regardless of whether the device is powered and regardless of the conditions on any of the other pins.

表 1. Device Mode Table

| Device Mode Table       |                                                       |                                                                                                                     |                                                                                                                                            | Input                                                                                                          | s                                                        |                                                                              | Outputs                 |         |          |  |

|-------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------|-------------------------|---------|----------|--|

| MC                      | ODE                                                   | VPWR                                                                                                                | C_CCx                                                                                                                                      | C_SBUx                                                                                                         | RPD_Gx                                                   | TJ                                                                           | FLT                     | CC FETs | SBU FETs |  |

| Normal                  | Unpowered,<br>no dead<br>battery<br>support           | <uvlo< td=""><td>X</td><td>X</td><td>Grounded</td><td>Х</td><td>High-Z</td><td>OFF</td><td>OFF</td></uvlo<>         | X                                                                                                                                          | X                                                                                                              | Grounded                                                 | Х                                                                            | High-Z                  | OFF     | OFF      |  |

| Operating<br>Conditions | Unpowered,<br>dead battery<br>support                 | <uvlo< td=""><td>X</td><td>Х</td><td>Shorted to C_CCx</td><td>Х</td><td>High-Z</td><td>OFF</td><td>OFF</td></uvlo<> | X                                                                                                                                          | Х                                                                                                              | Shorted to C_CCx                                         | Х                                                                            | High-Z                  | OFF     | OFF      |  |

|                         | Powered on                                            | >UVLO                                                                                                               | <ovp< td=""><td><ovp< td=""><td>X, forced<br/>OFF</td><td><tsd< td=""><td>High-Z</td><td>ON</td><td>ON</td></tsd<></td></ovp<></td></ovp<> | <ovp< td=""><td>X, forced<br/>OFF</td><td><tsd< td=""><td>High-Z</td><td>ON</td><td>ON</td></tsd<></td></ovp<> | X, forced<br>OFF                                         | <tsd< td=""><td>High-Z</td><td>ON</td><td>ON</td></tsd<>                     | High-Z                  | ON      | ON       |  |

|                         | Thermal shutdown                                      | >UVLO                                                                                                               | X                                                                                                                                          | X                                                                                                              | X, forced<br>OFF                                         | >TSD                                                                         | Low (Fault<br>Asserted) | OFF     | OFF      |  |

|                         | CC over voltage condition                             | >UVLO                                                                                                               | >OVP                                                                                                                                       | Х                                                                                                              | X, forced<br>OFF                                         | <tsd< td=""><td>Low (Fault<br/>Asserted)</td><td>OFF</td><td>OFF</td></tsd<> | Low (Fault<br>Asserted) | OFF     | OFF      |  |

| Fault<br>Conditions     | SBU over voltage condition                            | >UVLO                                                                                                               | X                                                                                                                                          | >OVP                                                                                                           | X, forced<br>OFF                                         | <tsd< td=""><td>Low (Fault<br/>Asserted)</td><td>OFF</td><td>OFF</td></tsd<> | Low (Fault<br>Asserted) | OFF     | OFF      |  |

|                         | IEC ESD<br>generated<br>over voltage<br>condition (1) | >UVLO                                                                                                               | Х                                                                                                                                          | Х                                                                                                              | R <sub>D</sub> ON if<br>RPD_Gx is<br>shorted to<br>C_CCx | <tsd< td=""><td>Low (Fault<br/>Asserted)</td><td>OFF</td><td>OFF</td></tsd<> | Low (Fault<br>Asserted) | OFF     | OFF      |  |

<sup>(1)</sup> This row describes the state of the device while still in OVP after the IEC ESD strike which put the device into OVP is over, and the voltages on the C\_CCx and C\_SBUx pins have returned to their normal voltage levels.

9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

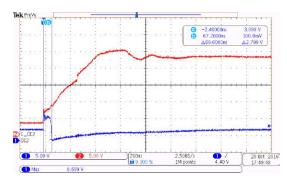

#### 9.1 Application Information

The TPD8S300A provides 4-channels of Short-to-V<sub>BUS</sub> overvoltage protection for the CC1, CC2, SBU1, and SBU2 pins of the USB Type-C connector, and 8-channels of IEC ESD protection for the CC1, CC2, SBU1, SBU2, DP\_T, DM\_T, DP\_B, DM\_B pins of the USB Type-C connector. Care must be taken to insure that the TPD8S300A provides adequate system protection as well as insuring that proper system operation is maintained. The following application example explains how to properly design the TPD8S300A into a USB Type-C system.

## 9.2 Typical Application

图 30. TPD8S300A Typical Application Diagram

ZHCSIE7 – JUNE 2018 www.ti.com.cn

# TEXAS INSTRUMENTS

## Typical Application (接下页)

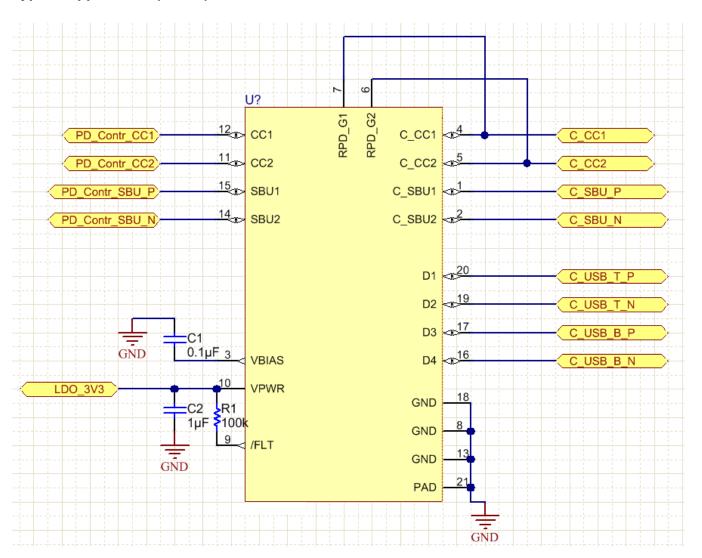

图 31. TPD8S300A Reference Schematic

#### 9.2.1 Design Requirements

In this application example we study the protection requirements for a full-featured USB Type-C DRP Port, fully equipped with USB-PD, USB2.0, USB3.0, Display Port, and 100 W charging. The TPS65982 is used to easily enable a full-featured port with a single chip solution. In this application, all the pins of the USB Type-C connector are utilized. Both the CC and SBU pins are susceptible to shorting to the  $V_{BUS}$  pin. With 100 W charging,  $V_{BUS}$  operates at 20 V, requiring the CC and SBU pins to tolerate 20- $V_{DC}$ . Additionally, the CC, SBU, and USB2.0 pins require IEC system level ESD protection. With these protection requirements present for the USB Type-C connector, the TPD8S300A is utilized. The TPD8S300A is a single chip solution that provides all the required protection for the low speed and USB2.0 pins in the USB Type-C connector.

表 2 lists the TPD8S300A design parameters.

表 2. Design Parameters

| DESIGN PARAMETER                                            | EXAMPLE VALUE |

|-------------------------------------------------------------|---------------|

| V <sub>BUS</sub> nominal operating voltage                  | 20 V          |

| Short-to-V <sub>BUS</sub> tolerance for the CC and SBU pins | 24 V          |

| VBIAS nominal capacitance                                   | 0.1 μF        |

ZHCSIE7-JUNE 2018 www.ti.com.cn

#### 表 2. Design Parameters (接下页)

| DESIGN PARAMETER                        | EXAMPLE VALUE |

|-----------------------------------------|---------------|

| Dead battery charging                   | 100 W         |

| Maximum ambient temperature requirement | 85°C          |

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 VBIAS Capacitor Selection

As noted in the Recommended Operating Conditions table, a minimum of 35-V<sub>BUS</sub> rated capacitor is required for the VBIAS pin, and a 50-V<sub>BUS</sub> capacitor is recommended. The VBIAS capacitor is in parallel with the central IEC diode clamp integrated inside the TPD8S300A. A forward biased hiding diode connects the VBIAS pin to the C\_CCx and C\_SBUx pins. Therefore, when a Short-to-V<sub>BUS</sub> event occurs at 20 V, 20-V<sub>BUS</sub> minus a forward biased diode drop is exposed to the VBIAS pin. Additionally, during the short-to-V<sub>BUS</sub> event, ringing can occur almost double the settling voltage of 20 V, allowing a potential 40 V to be exposed to the C\_CCx and C\_SBUx pins. However, the internal IEC clamps limit the voltage exposed to the C\_CCx and C\_SBUx pins to around 30 V. Therefore, at least 35-V<sub>BUS</sub> capacitor is required to insure the VBIAS capacitor does not get destroyed during Short-to-V<sub>BUS</sub> events.

A 50-V, X7R capacitor is recommended, however. This is to further improve the derating performance of the capacitors. When the voltage across a real capacitor is increased, its capacitance value derates. The more the capacitor derates, the greater than 2x ringing can occur in the short-to-V<sub>BUS</sub> RLC circuit. 50-V X7R capacitors have great derating performance, allowing for the best short-to-V<sub>BUS</sub> performance of the TPD8S300A.

Additionally, the VBIAS capacitor helps pass IEC 61000-4-2 ESD strikes. The more capacitance present, the better the IEC performance. So the less the VBIAS capacitor derates, the better the IEC performance. 表 3 shows real capacitors recommended to achieve the best performance with the TPD8S300A.

表 3. Design Parameters

| CAPACITOR SIZE | PART NUMBER        |

|----------------|--------------------|

| 0402           | CC0402KRX7R9BB104  |

| 0603           | GRM188R71H104KA93D |

#### 9.2.2.2 Dead Battery Operation

For this application, we want to support 100-W dead battery operation; when the laptop is out of battery, we still want to charge the laptop at 20 V and 5 A. This means that the USB PD Controller must receive power in dead battery mode. The TPS65982 has its own built in LDO in order to supply the TPS65982 power from V<sub>BUS</sub> in a dead battery condition. The TPS65982 can also provide power to its flash during this condition through its LDO 3V3 pin.

The OVP FETs of the TPD8S300A remain OFF when it is unpowered in order to insure in a dead battery situation proper protection is still provided to the PD controller in the system, in this case the TPS65982. However, when the OVP FETs are OFF, this isolates the TPS65982s dead battery resistors from the USB Type-C ports CC pins. A USB Type-C power adaptor must see the RD pull-down dead battery resistors on the CC pins or it does not provide power on V<sub>BUS</sub>. Since the TPS65982s dead battery resistors are isolated from the USB Type-C connector's CC pins, the built-in, dead battery resistors of the TPD8S300A must be connected. Short the RPD\_G1 pin to the C\_CC1 pin, and short the RPD\_G2 pin to the C\_CC2 pin.

Once the power adaptor sees the dead battery resistors of the TPD8S300A, it applies 5 V on the V<sub>BUS</sub> pin. This provides power to the TPS65982, turning the PD controller on, and allowing the battery to begin to charge. However, this application requires 100 W charging in dead battery mode, so V<sub>BUS</sub> at 20 V and 5 A is required. USB PD negotiation is required to accomplish this, so the TPS65982 needs to be able to communicate on the CC pins. This means the TPD8S300A needs to be turned on in dead battery mode as well so the TPS65982s PD controller can be exposed to the CC lines. To accomplish this, it is critical that the TPD8S300A is powered by the TPS65982s internal LDO, the LDO\_3V3 pin. This way, when the TPS65982 receives power on V<sub>BUS</sub>, the TPD8S300A is turned on simultaneously.

ZHCSIE7 – JUNE 2018 www.ti.com.cn

It is critical that the TPS65982's dead battery resistors are also connected to its CC pins for dead battery operation. Short the TPS65982s RPD\_G1 pin to its C\_CC1 pin, and its RPD\_G2 pin to its C\_CC2 pin. It is critical that the TPS65982s dead battery resistors are present; once the TPD8S300A receives power, turns on its OVP FETs and then removes its dead battery RD resistor, TPS65982's RD pull-down resistors must be present on the CC line in order to guarantee the power adaptor stays connected. If RD is not present the power adaptor will eventually interpret this as a disconnect and remove  $V_{\rm RUS}$ .

Also, it is important that the TPS65982's dead battery resistors are present so it properly boots up in dead battery operation with the correct voltages on its CC pins.

Once this process has occurred, the TPS65982 can start negotiating with the power adaptor through USB PD for higher power levels, allowing 100-W operation in dead battery mode.

For more information on the TPD8S300A dead battery operation, see the *CC Dead Battery Resistors Integrated for Handling the Dead Battery Use Case in Mobile Devices* section of the datasheet.

#### 9.2.2.3 CC Line Capacitance

USB PD has a specification for the total amount of capacitance that is required for proper USB PD BMC operation on the CC lines. The specification from section 5.8.6 of the *USB PD Specification* is given below in 表 4.

# 表 4. USB PD cReceiver Specification MIN MAX UNIT

| NAME      | DESCRIPTION             | MIN | MAX | UNIT | COMMENT                                                                                          |

|-----------|-------------------------|-----|-----|------|--------------------------------------------------------------------------------------------------|

| cReceiver | CC receiver capacitance | 200 | 600 | pF   | The DFP or UFP system shall have capacitance within this range when not transmitting on the line |

Therefore, the capacitance on the CC lines must stay in between 200 pF and 600 pF when USB PD is being used. Therefore, the combination of capacitances added to the system by the TPS65982, the TPD8S300A, and any external capacitor must fall within these limits. 表 5 shows the analysis involved in choosing the correct external CC capacitor for this system, and shows that an external CC capacitor is required.

#### 表 5. CC Line Capacitor Calculation

|                                           | -   |     |      |                                                                                                                                                            |

|-------------------------------------------|-----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CC Capacitance                            | MIN | MAX | UNIT | COMMENT                                                                                                                                                    |

| CC line target capacitance                | 200 | 600 | pF   | From the USB PD Specification section                                                                                                                      |

| TPS65982 capacitance                      | 70  | 120 | pF   | From the TPS65982 Datasheet                                                                                                                                |

| TPD8S300A capacitance                     | 60  | 120 | pF   | From the Electrical Characteristics table.                                                                                                                 |

| Proposed capacitor GRM033R71E221KA01D     | 110 | 330 | pF   | CAP, CERM, 220 pF, 25 V, ±10%, X7R, 0201 (For min and max, assume ±50% capacitance change with temperature and voltage derating to be overly conservative) |

| TPS65982 + TPD8S300A + GRM033R71E221KA01D | 240 | 570 | pF   | Meets USB PD cReceiver specification                                                                                                                       |

#### 9.2.2.4 Additional ESD Protection on CC and SBU Lines

If additional IEC ESD protection is desired to be placed on either the CC or SBU lines, it is important that high-voltage ESD protection diodes be used. The maximum DC voltage that can be seen in USB PD is  $21\text{-V}_{BUS}$ , with 21.5 V allowed during voltage transitions. Therefore, an ESD protection diode must have a reverse stand off voltage higher than 21.5 V in order to guarantee the diode does not breakdown during a short-to-V<sub>BUS</sub> event and have large amounts of current flowing through it indefinitely, destroying the diode. A reverse stand off voltage of 24 V is recommended to give margin above 21.5 V in case USB Type-C power adaptors are released in the market which break the USB Type-C specification.

Furthermore, due to the fact that the Short-to- $V_{BUS}$  event applies a DC voltage to the CC and SBU pins, a deep-snap-back diode cannot be used unless its minimum trigger voltage is above 42 V. During a Short-to- $V_{BUS}$  event, RLC ringing of up to 2x the settling voltage can be exposed to CC and SBU, allowing for up to 42 V to be exposed. Furthermore, if any capacitor derates on the CC or SBU line, greater than 2x ringing can occur. Since this ringing is hard to bound, it is recommended to not use deep-snap-back diodes. If the deep-snap-back diode triggers during the short-to- $V_{BUS}$  hot-plug event, it begins to operate in its conduction region. With a  $20-V_{BUS}$  source present on the CC or SBU line, this allows the diode to conduct indefinitely, destroying the diode.

#### 9.2.2.5 FLT Pin Operation

Once a Short-to- $V_{BUS}$  occurs on the C\_CCx or C\_SBUx pins, the  $\overline{FLT}$  pin is asserted in 20 µs (typical) so the PD controller can be notified quickly. If  $V_{BUS}$  is being shorted to CC or SBU, it is recommended to respond to the event by forcing a detach in the USB PD controller to remove  $V_{BUS}$  from the port. Although the USB Type-C port using the TPD8S300A is not damaged, as the TPD8S300A provides protection from these events, the other device connected through the USB Type-C Cable or any active circuitry in the cable can be damaged. Although shutting the  $V_{BUS}$  off through a detach does not guarantee it stops the other device or cable from being damaged, it can mitigate any high current paths from causing further damage after the initial damage takes place. Additionally, even if the active cable or other device does have proper protection, the short-to- $V_{BUS}$  event may corrupt a configuration in an active cable or in the other PD controller, so it is best to detach and reconfigure the port.

#### 9.2.2.6 How to Connect Unused Pins

If either the RPD\_Gx pins or any of the Dx pins are unused in a design, they must be connected to GND.

#### 9.2.3 Application Curves

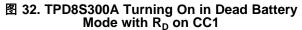

图 33. TPD8S300A Protecting the TPS65982 During a Short-to-V<sub>BUS</sub> Event

ZHCSIE7 – JUNE 2018 www.ti.com.cn

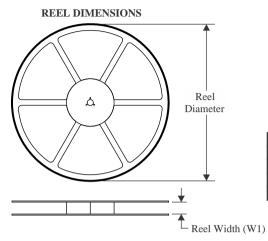

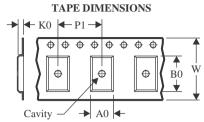

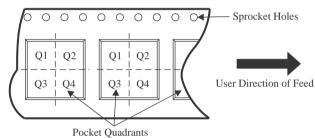

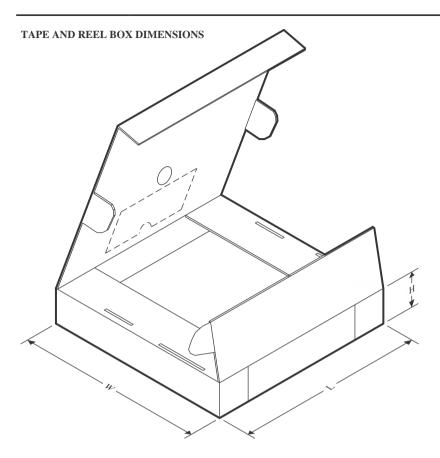

# TEXAS INSTRUMENTS