TPS1210-Q1

ZHCSQN1 - OCTOBER 2023

# TPS1210-Q1 具有短路保护和诊断功能的 45V、汽车类低 IQ、背靠背 MOSFET 智能高侧驱动器

# 1 特性

- 符合面向汽车应用的 AEC-Q100 汽车标准

- 器件温度等级 1: 40°C 至 +125°C 环境工作 温度范围

- 功能安全型

- 可提供用于功能安全系统设计的文档

- 3.5V至40V输入范围(绝对最大值45V)

- 反向输入保护低至 -40 V

- 集成 11V 电荷泵

- 低静态电流,运行时为 35μA

- 1.5µA 低关断电流(EN/UVLO = 低电平)

- 两个强大的栅极驱动器(2A 拉电流/灌电流),用 于通过单独的控制输入(INP1、INP2)进行背靠背 MOSFET 驱动

- 具有高电平有效 (TPS12100-Q1) 和低电平有效 (TPS12101-Q1) 输入的型号

- 使用外部 Rsense 或 MOSFET VDS 检测且具有可 调延迟 (TMR) 的可调节短路保护 (ISCP)

- 高侧或低侧电流检测配置 (CS SEL)

- 短路故障、电荷泵欠压、输入欠压和短路比较器诊 断 (SCP\_TEST) 期间的故障指示 (FLT)

- 可调节输入欠压锁定 (UVLO)

#### 2 应用

- 汽车类 12V BMS

- 直流/直流转换器

具有高侧电流检测功能的 BMS 断路器

#### 3 说明

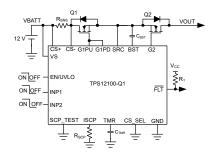

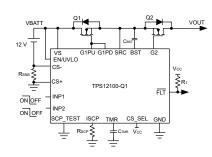

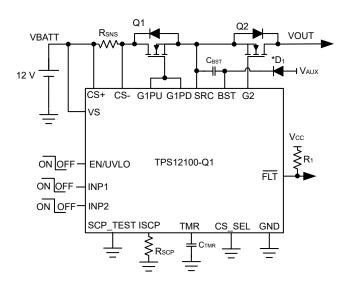

TPS1210x-Q1 系列是具有保护和诊断功能的 45V、低 IQ、智能高侧驱动器。该器件具有 3.5V 至 40V 的宽工 作电压范围,适用于 12V 系统设计。该器件可耐受低 至 -40 V 的负电源电压,并提供负载保护。

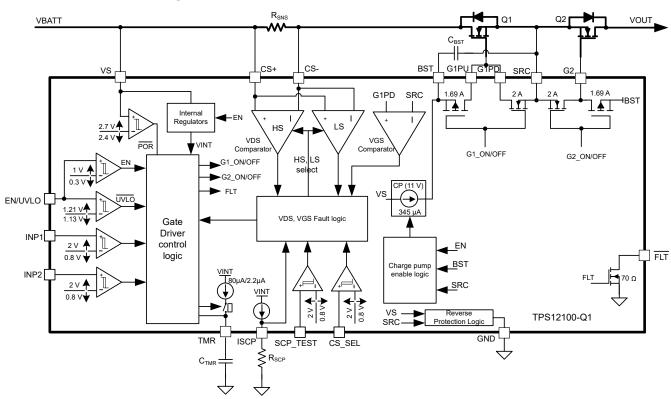

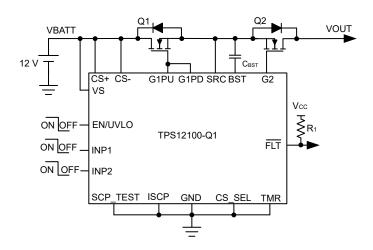

该器件包含两个具有单独控制输入(INP1、INP2)的 强大 (2A) 栅极驱动器,用于驱动采用共源极配置的背 靠背 MOSFET。TPS12100-Q1 具有高电平有效控制 输入, TPS12101-Q1 具有低电平有效控制输入。

该器件提供可调节的短路保护功能。可以配置自动重试 和锁存故障行为。可通过外部检测电阻或 MOSFET VDS 检测完成电流检测。可通过使用 CS\_SEL 引脚输 入实现高侧或低侧电流检测电阻配置。该器件还通过对 SCP\_TEST 输入的外部控制来诊断内部短路比较器。

运行期间的低静态电流 35uA (典型值)可实现常开型 系统设计。在 EN/UVLO 处于低电平时,静态电流降至 1.5 µ A (典型值)。

TPS1210x-Q1 采用 19 引脚 VSSOP 封装。

#### 器件信息

| 器件型号                         | 封装 <sup>(1)</sup> | 封装尺寸 <sup>(2)</sup> |

|------------------------------|-------------------|---------------------|

| TPS12100-Q1 ,<br>TPS12101-Q1 | DGX ( VSSOP、      | 5.1mm × 3.0mm       |

- 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

- 封装尺寸(长×宽)为标称值,并包括引脚(如适用)。

具有低侧电流检测功能的 BMS 断路器

# **Table of Contents**

| 1 特性1                                 | 9.4 Device Functional Modes                          | 17 |

|---------------------------------------|------------------------------------------------------|----|

| 2 应用                                  | 10 Application and Implementation                    | 18 |

| - <u>一</u> , <del>1</del><br>3 说明     | 10.1 Application Information                         | 18 |

| 4 Revision History2                   | 10.2 Typical Application: Circuit Breaker in Battery |    |

| 5 Device Comparison3                  | Management System (BMS) using Low Side               |    |

| 6 Pin Configuration and Functions3    | Current Sense                                        | 19 |

| 7 Specifications5                     | 10.3 Power Supply Recommendations                    | 25 |

| 7.1 Absolute Maximum Ratings5         | 10.4 Layout                                          | 26 |

| 7.2 ESD Ratings                       | 11 Device and Documentation Support                  | 28 |

| 7.3 Recommended Operating Conditions5 | 11.1 接收文档更新通知                                        | 28 |

| 7.4 Thermal Information6              | 11.2 支持资源                                            | 28 |

| 7.5 Electrical Characteristics6       | 11.3 Trademarks                                      | 28 |

| 7.6 Switching Characteristics7        | 11.4 静电放电警告                                          | 28 |

| 8 Parameter Measurement Information8  | 11.5 术语表                                             |    |

| 9 Detailed Description9               | 12 Mechanical, Packaging, and Orderable              |    |

| 9.1 Overview9                         | Information                                          | 28 |

| 9.2 Functional Block Diagram9         | 12.1 Tape and Reel Information                       |    |

| 9.3 Feature Description10             | •                                                    |    |

|                                       |                                                      |    |

# **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| DATE         | REVISION | NOTES           |

|--------------|----------|-----------------|

| October 2023 | *        | Initial Release |

# **5 Device Comparison**

|                             | TPS12100-Q1       | TPS12101-Q1      |

|-----------------------------|-------------------|------------------|

| Input controls (INP1, INP2) | Active High logic | Active Low logic |

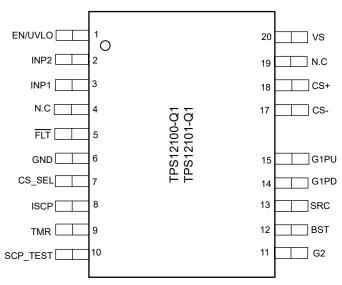

# **6 Pin Configuration and Functions**

图 6-1. VSSOP 19-Pin DGX Top View

表 6-1 Pin Functions

|          | DIN                                             | 10                  | ₹ 6-1. Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|----------|-------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|          | PIN                                             |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| NAME     | TPS1210x-Q1                                     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 10 11112 | DGX-19 (VSSOP)                                  |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| EN/UVLO  | 1                                               | I                   | EN/UVLO Input. A voltage on this pin above 1.21 V enables normal operation. Forcing this pin below 0.3 V shuts down the device reducing quiescent current to approximately 1.6 μA (typical). Optionally connect to the input supply through a resistive divider to set the undervoltage lockout.  When EN/UVLO is left floating an internal pull down of 100 nA pulls EN/UVLO low and keeps the device in shutdown state.             |  |  |  |  |

| INP2     | drive G2 INP2 has 2 I SRC who In TPS1: INP2 has |                     | Input Signal for external charge FET control. In TPS12100-Q1 drive INP2 high to drive G2 high. Drive INP2 low to pull G2 low.  INP2 has an internal weak 100-nA pulldown to GND to keep G2 pulled low to SRC when INP2 is left floating.  In TPS12101-Q1 drive INP2 low to drive G2 high. Drive INP2 high to pull G2 low. INP2 has an internal weak pulldown of 100 nA to GND to keep G2 high when INP2 is left floating.             |  |  |  |  |

| INP1     | 3                                               | I                   | Input Signal for external charge FET control. In TPS12100-Q1 drive INP1 high to drive G1PU high. Drive INP1 low to pull G1PD low. INP1 has an internal weak pulldown of 100 nA to GND to keep G1PD pulled to SRC when INP1 is left floating.  In TPS12101-Q1, drive INP1 low to drive G1PU high. Drive INP1 high to pull G1PD low. INP1 has an internal weak pull down of 100 nA to GND to keep G1PU high when INP1 is left floating. |  |  |  |  |

| N.C      | 4                                               |                     | No connect                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

Product Folder Links: TPS1210-Q1

Copyright © 2023 Texas Instruments Incorporated

提交文档反馈

3

# 表 6-1. Pin Functions (续)

|          | PIN            |                     | I. FIII T UIICUOIIS (英)                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|----------|----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | TPS1210x-Q1    | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| NAME     | DGX-19 (VSSOP) | -                   |                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| FLT      | 5              | 0                   | Open Drain Fault Output. This pin asserts low during short-circuit fault, charge pump UVLO, input UVLO and during SCP comparator diagnosis. If FLT feature is not desired then connect it to GND.                                                                                                                                                                       |  |  |  |

| GND      | 6              | G                   | Connect GND to system ground                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CS_SEL   | 7              | I                   | Current sense select input. Connect this pin to ground to activate high side current sense. Drive this pin to > 2 V to activate low side current sensing. CS_SEL has an internal weak pull down of 100 nA to GND.                                                                                                                                                       |  |  |  |

| ISCP     | 8              | ı                   | Short-circuit detection setting. A resistor across ISCP to GND sets the short circuit current comparator threshold.  If short-circuit protection feature is not desired then connect CS+, CS - , VS pins together and connect ISCP, TMR pins to GND.                                                                                                                    |  |  |  |

| TMR      | 9              | ı                   | Fault Timer Input. A capacitor across TMR pin to GND sets the delay time for short-circuit fault turn-off.  Leave this pin open for fastest response setting. If short-circuit protection feature is not desired then connect CS+, CS -, VS pins together and connect ISCP, TMR pins to GND.                                                                            |  |  |  |

| SCP_TEST | 10             | I                   | Internal short-circuit comparator (SCP) diagnosis input.  When SCP_TEST is driven low to high with INP1 pulled high, the internal SCP comparator operation is checked. FLT goes low and G1PD gets pulled to SRC if SCP comparator is functional.  Connect SCP_TEST pin to GND if this feature is not desired.  SCP_TEST has an internal weak pulldown of 100 nA to GND. |  |  |  |

| G2       | 11             | 0                   | Charging FET gate drive output. This pin has 1.69-A peak source and 2-A sink capacity. Leave the G2 pin floating if the G2 drive functionality is unused.                                                                                                                                                                                                               |  |  |  |

| BST      | 12             | 0                   | $\begin{array}{c} \mbox{High Side Bootstrapped Supply. An external capacitor with a minimum value of > \\ \mbox{$Q_{g(tot)}$ of the external FET must be connected between this pin and SRC.} \end{array}$                                                                                                                                                              |  |  |  |

| SRC      | 13             | 0                   | Source connection of the external FET                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| G1PD     | 14             | 0                   | High Current Gate Driver Pull-Down. This pin pulls down to SRC. For the fastest turn-off, tie this pin directly to the gate of the external high side MOSFET.                                                                                                                                                                                                           |  |  |  |

| G1PU     | 15             | 0                   | High Current Gate Driver Pull-Up. This pin pulls up to BST. Connect this pin to G1PD for maximum gate drive transition speed. A resistor can be connected between this pin and the gate of the external MOSFET to control the in-rush current during turn-on.                                                                                                           |  |  |  |

| CS-      | 17             | ı                   | Current sense negative input                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CS+      | 18             | I                   | Current sense positive input                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| N.C      | 19             | _                   | No connect                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| VS       | 20             | Power               | Supply pin of the controller                                                                                                                                                                                                                                                                                                                                            |  |  |  |

(1) I = input, O = output, I/O = input and output, P = power, G = Ground

提交文档反馈

Copyright © 2023 Texas Instruments Incorporated

4

# 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                       |                                                                | MIN               | MAX                       | UNIT |  |

|---------------------------------------|----------------------------------------------------------------|-------------------|---------------------------|------|--|

|                                       | VS, CS+, CS - to GND                                           | - 40              | 45                        |      |  |

|                                       | SRC to GND                                                     | - 40              | 45                        |      |  |

|                                       | G1PU, G1PD, G2, BST to SRC                                     | - 0.3             | 19                        |      |  |

| Input ping                            | ISCP, TMR, SCP_TEST to GND                                     | - 0.3             | 5.5                       | V    |  |

| Input pins                            | EN/UVLO, INP1, INP2, CS_SEL to GND, V <sub>(VS)</sub> > 0 V    | - 1               | 45                        | V    |  |

|                                       | EN/UVLO, INP1, INP2, CS_SEL to GND, $V_{(VS)} \le 0 \text{ V}$ | V <sub>(VS)</sub> | (40 + V <sub>(VS)</sub> ) |      |  |

|                                       | CS+ to CS -                                                    | - 1               | 45                        |      |  |

|                                       | FLT to GND                                                     | - 1               | 20                        |      |  |

| Sink current                          | I <sub>(FLT)</sub>                                             |                   | 10                        | mA   |  |

| Sink current                          | I <sub>(CS+)</sub> to I <sub>(CS-)</sub> , 1 ms                | - 100             | 100                       | mA   |  |

| Output pins                           | G1PU, G1PD, G2, BST to GND                                     | - 40              | 60                        | V    |  |

| Operating junction temperatu          | Operating junction temperature, T <sub>j</sub> <sup>(2)</sup>  |                   | 150                       | °C   |  |

| Storage temperature, T <sub>stg</sub> |                                                                | - 40              | 150                       | C    |  |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 7.2 ESD Ratings

|                                            |                                              |                                                         |            | VALUE | UNIT |

|--------------------------------------------|----------------------------------------------|---------------------------------------------------------|------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge |                                              | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> |            | ±2000 |      |

|                                            | Charged device model (CDM), per AEC Q100-011 | Corner pins (EN/UVLO, VS, SCP_TEST, G2)                 | ±750       | V     |      |

|                                            |                                              | ALC Q100-011                                            | Other pins | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|             |                                               | MIN  | NOM MAX | UNIT |

|-------------|-----------------------------------------------|------|---------|------|

| Innut nine  | VS to GND                                     | 3.5  | 40      |      |

| Input pins  | EN/UVLO, INP1, INP2, CS_SEL to GND            | 0    | 40      | V    |

| Output pins | FLT to GND                                    | 0    | 15      |      |

| External    | VS, SRC to GND                                | 22   |         | nF   |

| capacitor   | BST to SRC                                    | 0.1  |         | μF   |

| Tj          | Operating Junction temperature <sup>(2)</sup> | - 40 | 150     | °C   |

<sup>(1)</sup> Recommended Operating Conditions are conditions under which the device is intended to be functional. For specifications and test conditions, see Electrical Characteristics.

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

#### 7.4 Thermal Information

|                        |                                              | TPS1210-Q1 |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC(1)                            | DGX        | UNIT |

|                        |                                              | 19 PINS    |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 92.3       | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 28.6       | °C/W |

| R <sub>θ JB</sub>      | Junction-to-board thermal resistance         | 47.5       | °C/W |

| $\Psi$ JT              | Junction-to-top characterization parameter   | 0.6        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 47.2       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Electrical Characteristics

$T_J$  = -40 °C to +125 °C.  $V_{(VS)}$  = 12 V,  $V_{(BST - SRC)}$  = 11 V,  $V_{(SRC)}$  = 0 V

|                                             | PARAMETER                                                | TEST CONDITIONS                                        | MIN       | TYP  | MAX  | UNIT |

|---------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|-----------|------|------|------|

| SUPPLY VOLTAG                               | GE                                                       |                                                        |           |      |      |      |

| VS                                          | Operating input voltage                                  |                                                        | 3.5       |      | 40   | V    |

| I <sub>(Q)</sub>                            | Total system quiescent current, I <sub>(GND)</sub>       | V <sub>(EN/UVLO)</sub> = 2 V                           |           | 35   |      | μA   |

| I <sub>(SHDN)</sub>                         | SHDN current, I <sub>(GND)</sub>                         | V <sub>(EN/UVLO)</sub> = 0 V, V <sub>(SRC)</sub> = 0 V |           | 1.5  |      | μA   |

| ENABLE, UNDE                                | RVOLTAGE LOCKOUT (EN/UVLO), SHO                          | ORT CIRCUIT COMPARATOR TEST (SCP                       | _TEST) IN | PUT  | '    |      |

| V <sub>(UVLOR)</sub>                        | UVLO threshold voltage, rising                           |                                                        |           | 1.24 |      | V    |

| V <sub>(UVLOF)</sub>                        | UVLO threshold voltage, falling                          |                                                        |           | 1.14 |      | V    |

| V <sub>(ENR)</sub>                          | Enable threshold voltage for low Iq shutdown, rising     |                                                        |           |      | 1.02 | V    |

| V <sub>(ENF)</sub>                          | Enable threshold voltage for low Iq shutdown, falling    |                                                        | 0.3       |      |      | ٧    |

| V <sub>(SCP_TEST)</sub>                     | SCP test mode rising threshold                           |                                                        |           |      | 1.02 | V    |

| V <sub>(SCP_TEST)</sub>                     | SCP test mode rising threshold                           |                                                        | 0.3       |      |      | V    |

| I <sub>(EN/UVLO)</sub>                      | Enable input leakage current                             | V <sub>(EN/UVLO)</sub> = 12 V                          |           | 180  |      | nA   |

| CHARGE PUMP                                 | (BST - SRC)                                              |                                                        |           |      |      |      |

| V <sub>(BST - SRC_ON)</sub>                 | Charge Pump turn on voltage                              | V <sub>(EN/UVLO)</sub> = 2 V                           | 10        |      |      | V    |

| V <sub>(BST - SRC_OFF)</sub>                | Charge Pump turn off voltage                             | V <sub>(EN/UVLO)</sub> = 2 V                           |           |      | 11.8 | V    |

| V <sub>(BST_UVLOR)</sub>                    | V <sub>(BST - SRC)</sub> UVLO voltage threshold, rising  | V <sub>(EN/UVLO)</sub> = 2 V                           |           |      | 9.5  | V    |

| V <sub>(BST_UVLOF)</sub>                    | V <sub>(BST - SRC)</sub> UVLO voltage threshold, falling | V <sub>(EN/UVLO)</sub> = 2 V                           | 7.2       |      |      | ٧    |

| I <sub>(SRC)</sub>                          | SRC pin leakage current                                  | $V_{(EN/UVLO)} = 2 V, V_{(INP1)} = V_{(INP2)} = 0 V$   |           | 1    |      | μA   |

| GATE DRIVER O                               | UTPUTS (G1PU, G1PD, G2)                                  |                                                        |           |      |      |      |

| I <sub>(G1PU),</sub> I <sub>(G2_src)</sub>  | Peak Source Current                                      |                                                        |           | 1.69 |      | Α    |

| I <sub>(G1PD)</sub> , I <sub>(G2_snk)</sub> | Peak Sink Current                                        |                                                        |           | 2    |      | Α    |

| V <sub>(G1_GOOD)</sub>                      | VGS Good Threshold for G1 Gate Drive                     |                                                        |           | 7.5  |      | V    |

| SHORT CIRCUIT                               | PROTECTION (ISCP)                                        |                                                        |           |      |      |      |

|                                             |                                                          | $R_{(ISCP)} = 145 \text{ k}\Omega$                     | 240       | 300  | 360  | mV   |

|                                             | SCP threshold                                            | $R_{(ISCP)} = 32.5 \text{ k}\Omega$                    |           | 75   |      | mV   |

| $V_{(SCP)}$                                 |                                                          |                                                        |           |      |      |      |

Product Folder Links: TPS1210-Q1

提交文档反馈

Copyright © 2023 Texas Instruments Incorporated

提交

English Data Sheet: SLUSEZ2

# 7.5 Electrical Characteristics (续)

$T_J$  = -40 °C to +125 °C.  $V_{(VS)}$  = 12 V,  $V_{(BST - SRC)}$  = 11 V,  $V_{(SRC)}$  = 0 V

|                                               | PARAMETER                              | TEST CONDITIONS                  | MIN | TYP | MAX | UNIT |

|-----------------------------------------------|----------------------------------------|----------------------------------|-----|-----|-----|------|

| I <sub>(TMR_SRC_CB)</sub>                     | TMR source current                     |                                  |     | 80  |     | μA   |

| I <sub>(TMR_SRC_FLT)</sub>                    | TMR source current                     |                                  |     | 2.2 |     | μA   |

| I <sub>(TMR_SNK)</sub>                        | TMR sink current                       |                                  |     | 2.5 |     | μA   |

| V <sub>(TMR_SC)</sub>                         |                                        |                                  |     | 1.1 |     | V    |

| V <sub>(TMR_LOW)</sub>                        |                                        |                                  |     | 0.2 |     | V    |

| N <sub>(A-R Count)</sub>                      |                                        |                                  |     | 32  |     |      |

| INPUT CONTROLS                                | 6 (INP1, INP2), CURRENT SENSE SE       | LECT (CS_SEL) AND FAULT FLAG (FL | T)  |     |     |      |

| R <sub>(FLT)</sub>                            | FLT Pull-down resistance               |                                  |     | 70  |     | Ω    |

| V <sub>(INP1_H)</sub> , V <sub>(INP2_H)</sub> |                                        | TPS12100-Q1 Only                 |     |     | 2   | V    |

| V <sub>(INP1_L)</sub> , V <sub>(INP2_L)</sub> |                                        | TPS12100-Q1 Only                 | 0.8 |     |     | V    |

| V <sub>(CS_SEL_H)</sub>                       | CS_SEL threshold for low side sensing  |                                  |     |     | 2   | V    |

| V <sub>(CS_SEL_L)</sub>                       | CS_SEL threshold for high side sensing |                                  | 0.8 |     |     | V    |

# 7.6 Switching Characteristics

$T_J$  = -40 °C to +125 °C.  $V_{(VS)}$  = 12 V,  $V_{(BST - SRC)}$  = 11 V,  $V_{(SRC)}$  = 0 V

|                             | PARAMETER                                                                            | TEST CONDITIONS                                                                            | MIN | TYP | MAX | UNIT |

|-----------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

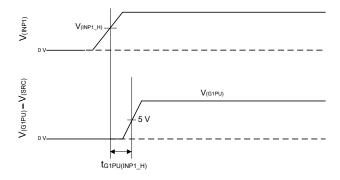

| t <sub>G1PU(INP1_H)</sub>   | INP1 turn on propogation Delay                                                       | INP1 $\uparrow$ to G1PU $\uparrow$ , C <sub>L</sub> = 47 nF                                |     | 1   |     | μs   |

| t <sub>G2(INP2_H)</sub>     | INP2 turn on propogation Delay                                                       | INP2 $\uparrow$ to G2 $\uparrow$ , C <sub>L</sub> = 47 nF                                  |     | 5   |     | μs   |

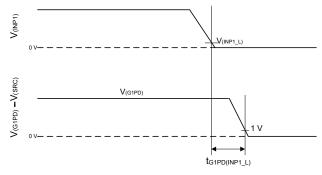

| t <sub>G1PD(INP1_L)</sub>   | INP1 turn off propogation Delay                                                      | INP1 ↓ to G1PD ↓ , C <sub>L</sub> = 47 nF                                                  |     | 1   |     | μs   |

| t <sub>G2(INP2_L)</sub>     | INP2 Turn off propogation Delay                                                      | INP2 ↓ to G2 ↓ , C <sub>L</sub> = 47 nF                                                    |     | 5   |     | μs   |

| t <sub>G1PD(UVLO_OFF)</sub> | UVLO turn off Propogation Delay                                                      | UVLO ↓ to G1PD ↓, C <sub>L</sub> = 47 nF                                                   |     | 7.5 |     | μs   |

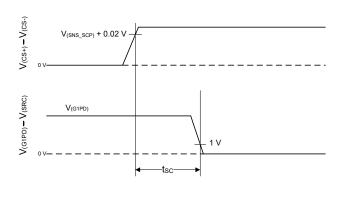

| t <sub>SC</sub>             | Hard short-circuit Protection propogation Delay                                      | $V_{(CS+-CS-)}\uparrow V_{(SCP)}$ to G1PD $\downarrow$ , $C_L$ = 47 nF, $C_{(TMR)}$ = Open |     | 4   |     | μs   |

| t <sub>SC_PUS</sub>         | Short circuit protection propogation delay during power up with output short circuit | C <sub>(TMR)</sub> = Open                                                                  |     |     | 10  | μs   |

# **8 Parameter Measurement Information**

图 8-1. Timing Waveforms

提交文档反馈

Copyright © 2023 Texas Instruments Incorporated

8

# 9 Detailed Description

#### 9.1 Overview

The TPS1210x-Q1 family is a 45-V, low IQ, smart high side driver with protection and diagnostics. With wide operating voltage range of 3.5 V - 40 V, the device is designed for 12-V, system designs. The device can withstand and protect the loads from negative supply voltages down to - 40 V.

The device has two strong (2-A) GATE drivers with separate control inputs (INP1, INP2) to drive back-to-back MOSFETs in common source configuration. Strong GATE driving enables power switching using parallel FETs in high current system designs. TPS12100-Q1 has active high control inputs and TPS12101-Q1 has active low control inputs.

The device provides configurable short-circuit protection using ISCP and TMR pins for adjusting the threshold and response time respectively. Auto-retry and latch-off fault behavior can be configured. With TPS1210x-Q1, current sensing an be done either by an external sense resistor or by MOSFET VDS sensing. High side or low side current sense resistor configuration is possible by using CS SEL pin input. Diagnosis of the integrated short circuit comparator is possible using external control on SCP TEST input.

The device indicates fault (FLT) on open drain output during short circuit, charge pump undervoltage, and input undervoltage conditions.

Low Quiescent Current of 35 µA in operation enables always ON system designs. Quiescent current reduces to 1.5 μ A (typical) with EN/UVLO low.

#### 9.2 Functional Block Diagram

Product Folder Links: TPS1210-Q1

9

#### 9.3 Feature Description

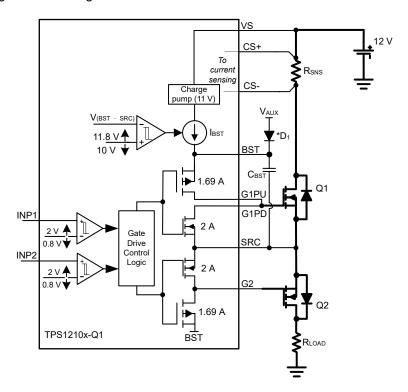

#### 9.3.1 Charge Pump and Gate Driver Output (VS, G1PU, G1PD, G2, BST, SRC)

89-1 shows a simplified diagram of the charge pump and gate driver circuit implementation. The device houses two strong 1.69-A/2-A peak source/sink gate drivers enabling paralleling of FETs in high power system designs ensuring minimum transition time in saturation region. A 11-V, 345- $\mu$ A charge pump is derived from VS terminal and charges the external boot-strap capacitor,  $C_{BST}$  that is placed across the gate driver (BST and SRC).

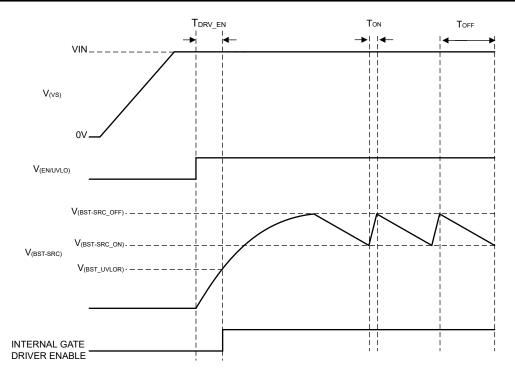

VS is the supply pin to the controller. With VS applied and EN/UVLO pulled high, the charge pump turns ON and charges the  $C_{BST}$  capacitor. After the voltage across  $C_{BST}$  crosses  $V_{(BST\_UVLOR)}$ , the GATE driver section is activated. The device has a 1-V (typical) UVLO hysteresis to ensure chattering less performance during initial GATE turn ON. Choose  $C_{BST}$  based on the external FET  $Q_G$  and allowed dip during FET turn-ON. The charge pump remains enabled until the BST to SRC voltage reaches 11.8 V, typically, at which point the charge pump is disabled decreasing the current draw on the VS pin. The charge pump remains disabled until the BST to SRC voltage discharges to 10 V typically at which point the charge pump is enabled. The voltage between BST and SRC continue to charge and discharge between 11.8 V and 10 V as shown in the  $\frac{1}{2}$  9-2.

图 9-1. Gate Drivers

Copyright © 2023 Texas Instruments Incorporated

图 9-2. Charge Pump Operation

Use the following equation to calculate the initial gate driver enable delay:

$$T_{DRV\_EN} = \frac{C_{BST} \times V_{(BST\_UVLOR)}}{345 \,\mu A} \tag{1}$$

Where,

C<sub>BST</sub> is the charge pump capacitance connected across BST and SRC pins.

$V_{(BST\ UVLOR)} = 9.5\ V\ (maximum).$

If  $T_{DRV\_EN}$  must be reduced then pre-bias BST terminal externally using an external  $V_{AUX}$  supply through a low leakage diode  $D_1$  as shown in . With this connection,  $T_{DRV\_EN}$  reduces to 400  $\mu$ s. TPS12100-Q1 application circuit with external supply to BST is shown in \( \begin{align\*} \text{9-3}. \end{align\*} \)

English Data Sheet: SLUSEZ2

图 9-3. TPS12100-Q1 Application Circuit With External Supply to BST

备注

V<sub>AUX</sub> can be supplied by external regulated supply ranging between 8 V and 18 V.

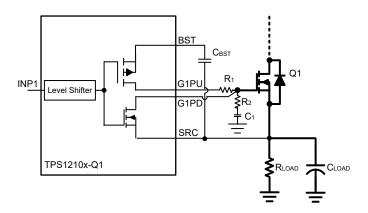

#### 9.3.2 Capacitive Load Driving Using FET Gate (G1PU, G1PD) Slew Rate Control

For limiting inrush current during turn-ON of the external FET (Q1) with capacitive loads, use  $R_1$ ,  $R_2$ ,  $C_1$  as shown in  $\mathbb{Z}$  9-4. The  $R_1$  and  $C_1$  components slow down the voltage ramp rate at the gate of Q1 FET. The FET source follows the gate voltage resulting in a controlled voltage ramp across the output capacitors.

图 9-4. Inrush Current Limiting Using G1 Gate Drive

Use the 方程式 2 to calculate the inrush current during turn-ON of the FET.

$$I_{INRUSH} = C_{LOAD} \times \frac{V_{BATT}}{T_{charge}}$$

(2)

Copyright © 2023 Texas Instruments Incorporated

$$C_{1} = \frac{0.63 \times V_{(BST - SRC)} \times C_{LOAD}}{R_{1} \times I_{INRIISH}}$$

(3)

Where,

C<sub>LOAD</sub> is the load capacitance.

VBATT is the input voltage and T<sub>charge</sub> is the charge time.

$V_{(BST-SRC)}$  is the charge pump voltage (11 V),

Use a damping resistor  $R_2$  (approximately 10  $\Omega$ ) in series with  $C_1$ . 方程式 3 can be used to compute required  $C_1$  value for a target inrush current. A 100-k $\Omega$  resistor for  $R_1$  can be a good starting point for calculations.

Connecting G1PD pin of TPS1210x-Q1 directly to the gate of the Q1 FET ensures fast turn-OFF without any impact of  $R_1$  and  $C_1$  components.

$C_1$  results in an additional loading on  $C_{BST}$  to charge during turn-ON. Use below equation to calculate the required  $C_{BST}$  value:

$$C_{BST} = \frac{Q_{g(total)}}{\Delta V_{BST}} + 10 \times C_1$$

(4)

Where,

Q<sub>a(total)</sub> is the total gate charge of the FET,

$\triangle$  V<sub>BST</sub> (1 V typical) is the ripple voltage across BST to SRC pins.

#### 9.3.3 Short-Circuit Protection

The TPS1210x-Q1 feature adjustable short-circuit protection. The threshold and response time can be adjusted using  $R_{SCP}$  resistor and  $C_{TMR}$  capacitor respectively. The device senses the voltage across CS+ and CS - pins.

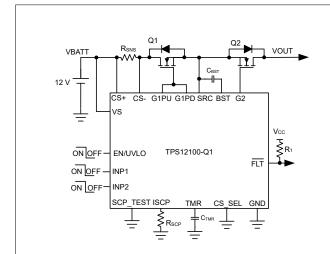

图 9-5. TPS12100-Q1 Application Circuit With External Sense Resistor RSNS based High Side Current Sensing

图 9-6. TPS12100-Q1 Application Circuit With MOSFET RDSON based Current Sensing

图 9-7. TPS12100-Q1 Application Circuit with External Sense Resistor RSNS based Low Side Current Sensing

Set the short-circuit detection threshold using an external R<sub>SCP</sub> resistor across ISCP and GND pins. Use 方程式 5 to calculate the required R<sub>SCP</sub> value:

$$R_{SCP}\left(\Omega\right) = \frac{(I_{SC} \times R_{SNS} - 10 \text{ mV})}{2 \mu A}$$

(5)

Refer to 方程式 9 in Application Limitations section for update in equation in final revision of IC.

Where

**ADVANCE INFORMATION**

R<sub>SNS</sub> is the current sense resistor value or the FET R<sub>DSON</sub> value.

I<sub>SC</sub> is the desired short-circuit current level.

The short-circuit protection response is fastest with no C<sub>TMR</sub> cap connected across TMR and GND pins.

With the device powered ON and EN/UVLO, INP1 pulled high, During Q1 turn-ON, first VGS of external FET Q1 (G1 gate drive) is sensed by monitoring the voltage across G1PD to SRC. Once G1PD to SRC voltage raises above  $V_{(G1\ GOOD)}$  threshold which ensures that the external FET is enhanced, then the SCP comparator output is monitored. If the sensed voltage across CS+ and CS - exceeds the short-circuit set point (V<sub>(SCP)</sub>), G1PD pulls low to SRC and FLT asserts low. Subsequent events can be set either to be auto-retry or latch off as described in following sections.

#### 9.3.3.1 Short-Circuit Protection With Auto-Retry

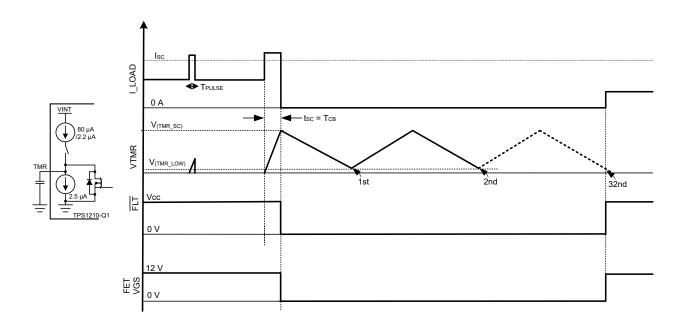

The C<sub>TMR</sub> programs the short-circuit protection delay (t<sub>SC</sub>) and auto-retry time (t<sub>RETRY</sub>). After the voltage across CS+ and CS - exceeds the set point, the C<sub>TMR</sub> starts charging with 80- μ A pullup current.

After  $C_{TMR}$  charges to  $V_{(TMR\_SC)}$ , G1PD pulls low to SRC and  $\overline{FLT}$  asserts low providing warning on impending FET turn-OFF. Post this event, the auto-retry behavior starts. The C<sub>TMR</sub> capacitor starts discharging with 2.5-uA pulldown current. After the voltage reaches V<sub>(TMR LOW)</sub> level, the capacitor starts charging with 2.2-uA pullup. After 32 charging-discharging cycles of C<sub>TMR</sub> the FET turns ON back and FLT de-asserts.

The device retry time ( $t_{RETRY}$ ) is based on  $C_{TMR}$  for the first time as per 方程式 7.

Use 方程式 6 to calculate the C<sub>TMR</sub> capacitor to be connected across TMR and GND.

$$C_{\text{TMR}} = \frac{I_{\text{TMR}} \times t_{\text{SC}}}{1.1} \tag{6}$$

Product Folder Links: TPS1210-Q1

Where,

Copyright © 2023 Texas Instruments Incorporated

I<sub>TMR</sub> is internal pullup current of 80 μA.

t<sub>SC</sub> is the desired short-circuit response time.

Leave TMR floating for fastest short-circuit response time.

$$t_{RETRY} = 22.7 \times 10^6 \times C_{TMR} \tag{7}$$

If the short-circuit pulse duration is below  $t_{SC}$  then the FET remains ON and  $C_{TMR}$  gets discharged using internal pulldown switch.

图 9-8. Short-Circuit Protection With Auto-Retry

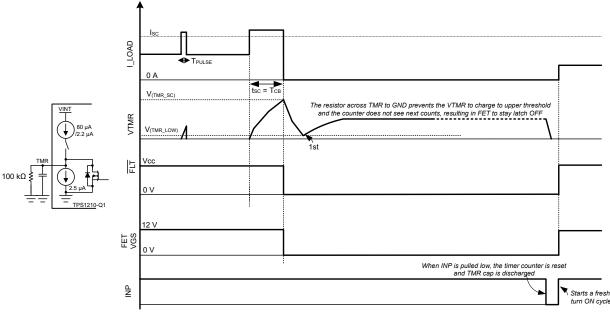

#### 9.3.3.2 Short-Circuit Protection With Latch-Off

Connect an approximately 100-k  $\Omega$  resistor across  $C_{TMR}$  as shown in  $\[ \]$  9-9. With this resistor, during the charging cycle, the voltage across  $C_{TMR}$  gets clamped to a level below  $V_{(TMR\_SC)}$  resulting in a latch-off behavior and  $\overline{FLT}$  asserts low at same time.

Use 方程式 8 to calculate  $C_{TMR}$  capacitor to be connected between TMR and GND for  $R_{TMR}$  = 100 k  $\Omega$  .

$$C_{\text{TMR}} = \frac{t_{\text{SC}}}{R_{\text{TMR}} \times \ln\left(\frac{1}{1 - \frac{1.1}{R_{\text{TMR}} \times 80 \,\mu\text{A}}}\right)}$$

(8)

Where,

$I_{TMR}$  is internal pullup current of 80  $\mu$  A.

t<sub>SC</sub> is the desired short-circuit response time.

Toggle INP or EN/UVLO (below  $V_{(ENF)}$ ) or power cycle VS below  $V_{(VS\_PORF)}$  to reset the latch. At low edge, the timer counter is reset and  $C_{TMR}$  is discharged. G1PU pulls up to BST when INP is pulled high.

English Data Sheet: SLUSEZ2

**ADVANCE INFORMATION**

图 9-9. Short-Circuit Protection With Latch-Off

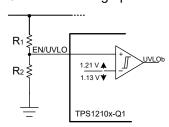

#### 9.3.4 Undervoltage Protection (UVLO)

TPS1210x-Q1 has an accurate undervoltage protection (< ±2%) using EN/UVLO pin providing robust protection. Connect a resistor ladder as shown in

9-10 for undervoltage protection threshold programming.

图 9-10. Programming Undervoltage Protection

#### 9.3.5 Reverse Polarity Protection

The TPS1210x-Q1 devices features integrated reverse polarity protection to protect the device from failing during input and output reverse polarity faults. Reverse polarity faults occur during installation and maintenance of the end equipments. The device is tolerant to reverse polarity voltages down to - 45 V both on input and on the output.

On the output side, the device can see transient negative voltages during regular operation due to output cable harness inductance kickbacks when the switches are turned OFF. In such systems the output negative voltage level is limited by the output side TVS or a diode.

#### 9.3.6 Short-Circuit Protection Diagnosis (SCP\_TEST)

In the safety critical designs, the short-circuit protection (SCP) feature and the diagnosis are important.

The TPS1210x-Q1 features the diagnosis of the internal short-circuit protection. When SCP TEST is driven low to high, then a voltage is applied internally across the SCP comparator inputs to simulate a short-circuit event.

Copyright © 2023 Texas Instruments Incorporated

The comparator output controls the gate drive (G1PU/G1PD) and also the  $\overline{FLT}$ . If the gate drive goes low (with initially being high) and  $\overline{FLT}$  also goes low, then this action indicates that the SCP is good otherwise is to be treated as the SCP feature is not functional.

If the SCP\_TEST feature is not used, then connect SCP\_TEST pin to GND.

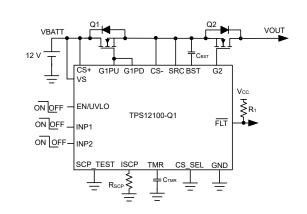

### 9.3.7 TPS1210x-Q1 as a Simple Gate Driver

§ 9-11 shows application schematics of TPS1210x-Q1 as a simple gate driver in load connect-disconnect switch driving back-to-back FETs topology. The short-ciruit protection feature is disabled.

图 9-11. TPS12100-Q1 Application Circuit for Simple Gate Driver

#### 9.4 Device Functional Modes

The TPS1210x-Q1 has two modes of operation. Active mode and low IQ shutdown mode.

If the EN/UVLO pin voltage is greater than  $V_{(ENR)}$  rising threshold, then the device is in active mode. In active state the internal charge pump is enabled, gate drivers, all the protection and diagnostic features are enabled.

If the EN/UVLO voltage is pulled below  $V_{(ENF)}$  falling threshold, the device enters into low IQ shutdown mode. In this mode, the charge pump, gate drivers and all the protection features are disabled. The gate drive and external FETs turn OFF. The TPS1210x-Q1 consumes low IQ of 1.5  $\mu$  A (typical) in this mode.

# 10 Application and Implementation

#### 备注

以下应用部分中的信息不属于 TI 器件规格的范围, TI 不担保其准确性和完整性。TI 的客户应负责确定器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

#### 10.1 Application Information

The TPS1210x-Q1 family is a 45-V, low IQ, smart high side driver with protection and diagnostics. The TPS1210x-Q1 device architecture is design to drive and control back-to-back N-Channel MOSFETs independently in common source configuration with separate control inputs (INP1, INP2), which makes TPS1210x-Q1 an excellent choice to realize circuit breaker in battery management system (BMS). The strong (2-A) GATE drivers enable switching parallel MOSFETs in high current applications such as circuit breaker in powertrain (DC/DC converter), driving loads in power distribution unit, circuit breaker in 12-V BMS, and so forth.

The TPS1210x-Q1 device provides configurable short-circuit protection using ISCP and TMR pins for adjusting the threshold and response time respectively. Auto-retry and latch-off fault behavior can be configured. By using CS+ and CS - pins, current sensing can be done either by an external sense resistor or by MOSFET VDS sensing. High side or low side current sense resistor configuration is possible by using CS\_SEL pin input. The device also features diagnosis of the internal short circuit comparator using external control on SCP\_TEST input.

The following design procedure can be used to select the supporting component values based on the application requirement.

#### 10.1.1 Application Limitations

This section highlights some limitations in the application which were identified during bench evaluation of the existing TPS1210-Q1 silicon on the evaluation module (EVM).

#### 10.1.1.1 Short-Circuit Protection Delay

In application designs with high side current sense configurations as shown in  $\boxtimes$  9-5 and  $\boxtimes$  9-6 with C<sub>TMR</sub> = Open, the short-circuit protection delay during power up with output short circuited does not match the specified maximum value of 10  $\mu$ s.

Testing has shown that the actual short-circuit protection delay during power up by EN/UVLO signal is approximately 70 µs. This increase in protection delay still allows for the TPS1210-Q1 to operate as designed, but results in larger power dissipation in the external MOSFET during output short-circuit scenario.

A design fix must be included in the final version of the IC.

#### 10.1.1.2 Short-Circuit Protection Threshold

The minimum short-circuit protection threshold is limited to 30 mV.

A design update is planned in the final revision of the IC to extend the minimum threshold down to 20 mV. Due to the design update there will be a change of  $R_{SCP}$  resistor formula and the revised formula will be as per the  $\overline{\jmath}$   $\overline{\jmath}$  9:

$$R_{SCP}\left(\Omega\right) = \frac{\left(I_{SC} \times R_{SNS} - 19 \text{ mV}\right)}{2 \mu A} \tag{9}$$

Lowest SCP threshold setting will be limited to 20 mV.

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLUSEZ2

# 10.2 Typical Application: Circuit Breaker in Battery Management System (BMS) using Low Side Current Sense

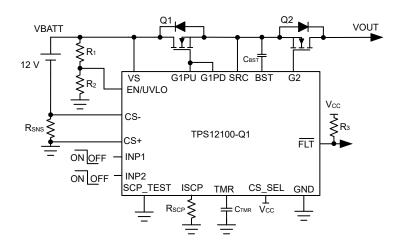

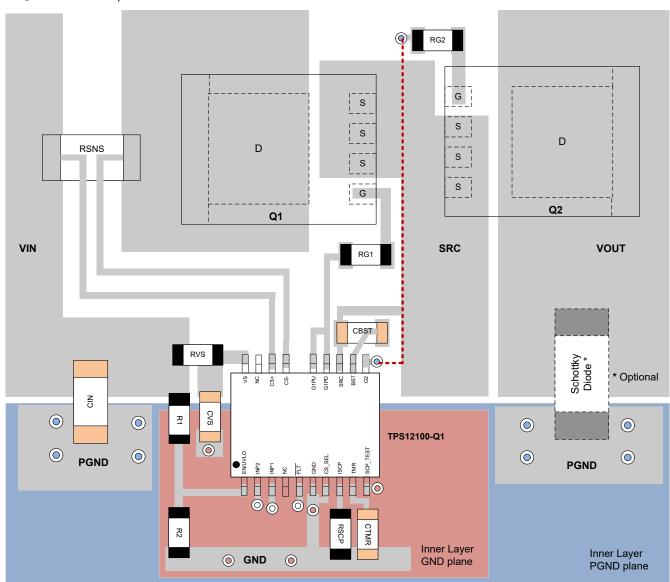

图 10-1. Typical Application Schematic: BMS Circuit Breaker With Low Side Current Sense

#### 10.2.1 Design Requirements

The following table shows the design parameters for this application example.

表 10-1. Design Parameters

| PARAMETER                                           | VALUE      |  |  |  |  |

|-----------------------------------------------------|------------|--|--|--|--|

| Typical input voltage, V <sub>IN</sub>              | 12 V       |  |  |  |  |

| Undervoltage lockout set point, VIN <sub>UVLO</sub> | 6.5 V      |  |  |  |  |

| Maximum load current, I <sub>OUT</sub>              | 25 A       |  |  |  |  |

| Short-circuit protection threshold, I <sub>SC</sub> | 40 A       |  |  |  |  |

| Short-circuit protection delay (t <sub>SC</sub> )   | 1 ms       |  |  |  |  |

| Fault response                                      | Auto-retry |  |  |  |  |

| Current sensing                                     | Low-side   |  |  |  |  |

#### 10.2.2 Detailed Design Procedure

#### Selection of Current Sense Resistor, R<sub>SNS</sub>

The recommended range of the overcurrent protection threshold voltage, V<sub>(SCP)</sub>, extends from 30 mV to 300 mV. Values near the low threshold of 30 mV can be affected by the system noise. Values near the upper threshold of 300 mV can cause high power dissipation in the current sense resistor. To minimize both the concerns, 40 mV is selected as the short-circuit protection threshold voltage. Use the following equation to calculate the current sense resistor, R<sub>SNS</sub>.

$$R_{SNS} = \frac{V_{(SCP)}}{I_{SC}}$$

(10)

The next smaller available sense resistor 1 m $\Omega$ , 1% is chosen.

To improve signal to noise ratio or for better short-circuit protection accuracy, higher short-circuit protection threshold voltage,  $V_{(SCP)}$  can be selected.

#### Programming the Short-Circuit Protection Threshold - R<sub>SCP</sub> Selection

The R<sub>SCP</sub> sets the short-circuit protection threshold. Use the following equation to calculate the value.

$$R_{SCP}\left(\Omega\right) = \frac{(I_{SC} \times R_{SNS} - 10 \text{ mV})}{2 \mu A} \tag{11}$$

To set 30-A as short-circuit protection threshold,  $R_{SCP}$  value is calculated to be 15 k $\Omega$ .

Choose the closest available standard value: 15 k $\Omega$ , 1%.

Refer to 方程式 9 in Application Limitations section for update in equation in final revision of IC.

In case where large di/dt is involved, the system and layout parasitic inductances can generate large differential signal voltages between CS+ and CS- pins. This action can trigger false short-circuit protection and nuisance trips in the system. To overcome such scenario, TI suggests to add placeholder for RC filter components across sense resistor (R<sub>SNS</sub>) and tweak the values during test in the real system. The RC filter components should not be used in current sense designs by MOSFET VDS sensing to avoid impact on the short-circuit protection response.

Product Folder Links: TPS1210-Q1

Copyright © 2023 Texas Instruments Incorporated

#### Programming the Short-Circuit Protection Delay - C<sub>TMR</sub> Selection

For the design example under discussion, overcurrent transients are allowed for 1-ms duration. This short-circuit protection delay,  $t_{SC}$  can be set by selecting appropriate capacitor  $C_{TMR}$  from TMR pin to ground. Use the following equation to calculate the value of  $C_{TMR}$  to set 1 ms for  $t_{SC}$ .

$$C_{\text{TMR}} = \frac{80 \,\mu \times t_{\text{SC}}}{1.1} = 72.72 \,\text{nF} \tag{12}$$

Choose closest available standard value: 82 nF, 10%.

### Selection of MOSFETs, Q1 and Q2

For selecting the MOSFET  $Q_1$  and  $Q_2$  important electrical parameters are the maximum continuous drain current  $I_D$ , the maximum drain-to-source voltage  $V_{DS(MAX)}$ , the maximum drain-to-source voltage  $V_{GS(MAX)}$ , and the drain-to-source ON-resistance  $R_{DSON}$ .

The maximum continuous drain current, I<sub>D</sub>, rating must exceed the maximum continuous load current.

The maximum drain-to-source voltage,  $V_{DS(MAX)}$ , must be high enough to withstand the highest voltage seen in the application. Considering 35 V as the maximum application voltage, MOSFETs with  $V_{DS}$  voltage rating of 40 V is designed for this application.

The maximum  $V_{GS}$  TPS1210-Q1 can drive is 13 V, so a MOSFET with 15-V minimum  $V_{GS}$  rating must be selected.

To reduce the MOSFET conduction losses, lowest possible R<sub>DS(ON)</sub> is preferred.

Based on the design requirements, BUK7S1R0-40H is selected and the ratings are:

- 40-V V<sub>DS(MAX)</sub> and 20-V V<sub>GS(MAX)</sub>

- $R_{DS(ON)}$  is 0.88-m  $\Omega$  typical at 10-V  $V_{GS}$

- Maximum MOSFET Q<sub>g(total)</sub> is 137 nC

#### Selection of Bootstrap Capacitor, C<sub>BST</sub>

The internal charge pump charges the external bootstrap capacitor (connected between BST and SRC pins) with approximately 345  $\,\mu$  A. Use the following equation to calculate the minimum required value of the bootstrap capacitor for driving two BUK7S1R0-40H MOSFETs.

$$C_{BST} = \frac{Q_{g(total)}}{1 \text{ V}} = 274 \text{ nF}$$

(13)

Choose closest available standard value: 330 nF, 10 %.

#### Setting the Undervoltage Lockout

The undervoltage lockout (UVLO) can be adjusted using an external voltage divider network of  $R_1$  and  $R_2$  connected between VS, EN/UVLO and GND pins of the device. The values required for setting the undervoltage and overvoltage are calculated by solving 方程式 14.

$$V_{(UVLOR)} = \frac{R_2}{(R_1 + R_2)} \times VIN_{UVLO}$$

(14)

For minimizing the input current drawn from the power supply, TI recommends to use higher values of resistance for  $R_1$  and  $R_2$ . However, leakage currents due to external active components connected to the resistor string can add error to these calculations. So, the resistor string current,  $I(R_{12})$  must be chosen to be 20 times greater than the leakage current of UVLO pin.

Product Folder Links: TPS1210-Q1

Copyright © 2023 Texas Instruments Incorporated

提交文档反馈

21

22

Product Folder Links: TPS1210-Q1

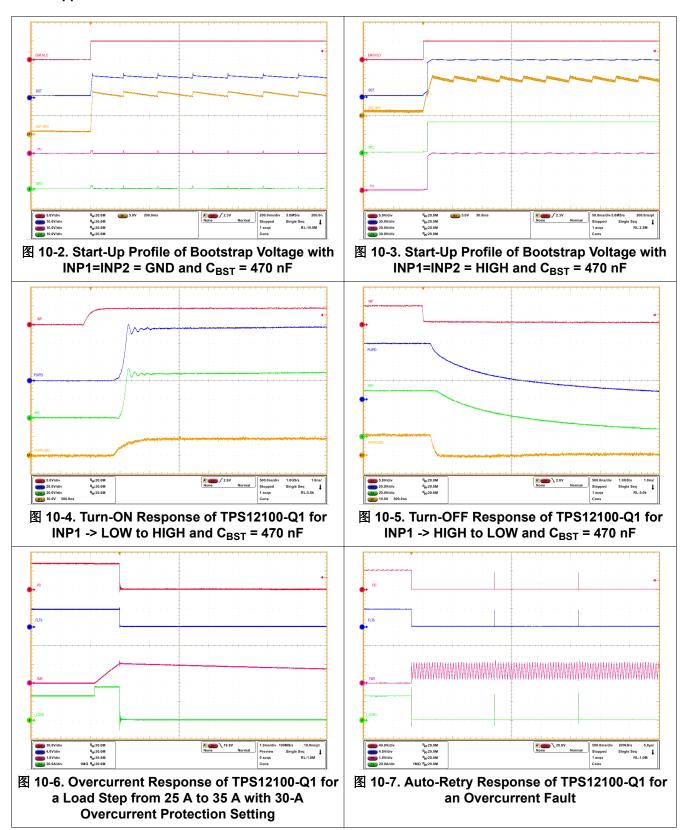

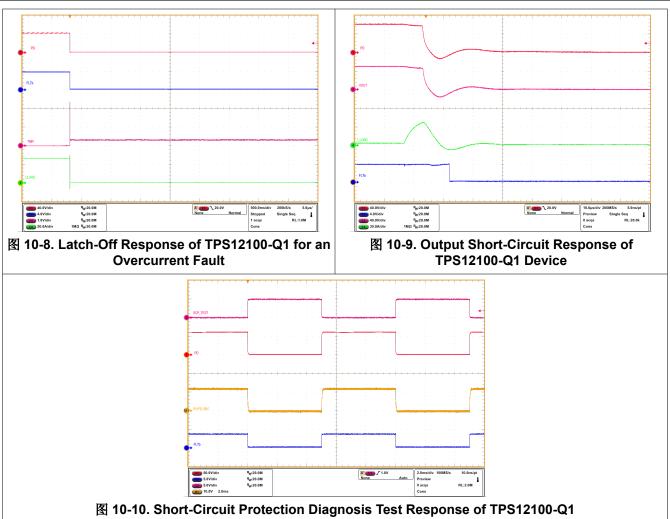

#### 10.2.3 Application Curves

#### 10.3 Power Supply Recommendations

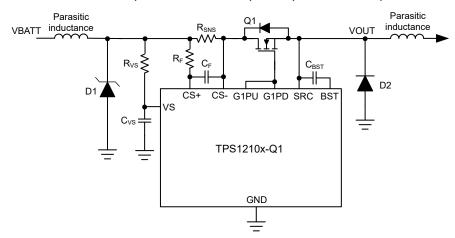

When the external MOSFETs turn-OFF during the conditions such as INP1 control, overcurrent protection causing an interruption of the current flow, the input parasitic line inductance generates a positive voltage spike on the input and output parasitic inductance generates a negative voltage spike on the output. The peak amplitude of voltage spikes (transients) depends on the value of inductance in series to the input or output of the device. These transients can exceed the *Absolute Maximum Ratings* of the device if steps are not taken to address the issue. Typical methods for addressing transients include:

- Use of a TVS diode and input capacitor filter combination across input to and GND to absorb the energy and dampen the positive transients.

- Use of a diode or a TVS diode across the output and GND to absorb negative spikes.

The TPS1210-Q1 gets powered from the VS pin. Voltage at this pin must be maintained above  $V_{(VS\_PORR)}$  level to ensure proper operation. If the input power supply source is noisy with transients, then TI recommends to place a  $R_{VS}$  -  $C_{VS}$  filter between the input supply line and VS pin to filter out the supply noise. TI recommends  $R_{VS}$  value around 100  $\Omega$ .

In case where large di/dt is involved, the system and layout parasitic inductances can generate large differential signal voltages between CS+ and CS- pins. This action can trigger false short-circuit protection and nuisance trips in the system. To overcome such scenario, TI suggests to add placeholder for RC filter components across sense resistor ( $R_{SNS}$ ) and tweak the values during test in the real system. The RC filter components must not be used in current sense designs by MOSFET VDS sensing to avoid impact on the short-circuit protection response.

The following figure shows the circuit implementation with optional protection components.

图 10-11. Circuit Implementation With Optional Protection Components For TPS1210-Q1

#### 10.4 Layout

#### 10.4.1 Layout Guidelines

- Place the sense resistor (R<sub>SNS</sub>) close to the TPS1210x-Q1 and then connect R<sub>SNS</sub> using the Kelvin techniques. Refer to Choosing the Right Sense Resistor Layout for more information on the Kelvin techniques.

- Choose a 0.1 µF or higher value ceramic decoupling capacitor between VS terminal and GND for all the applications. Consider adding RC network at the supply pin (VS) of the controller to improve decoupling against the power line disturbances.

- Make the high-current path from the board input to the load, and the return path, parallel and close to each other to minimize loop inductance.

- Place the external MOSFETs close to the controller GATE drive pins (G1PU/PD and G2) such that the GATE of the MOSFETs are close to the controller GATE drive pins and forms a shorter GATE loop. Consider adding a place holder for a resistor in series with the Gate of each external MOSFET to damp high frequency oscillations if need arises.

- Place a TVS diode at the input to clamp the voltage transients during hot-plug and fast turn-off events.

- Place the external boot-strap capacitor close to BST and SRC pins to form very short loop.

- Connect the ground connections for the various components around the TPS1210x-Q1 directly to each other, and to the TPS1210x-Q1 GND, and then connected to the system ground at one point. Do not connect the various component grounds to each other through the high current ground line.

提交文档反馈

Copyright © 2023 Texas Instruments Incorporated

#### 10.4.2 Layout Example

Via to PGND plane

图 10-12. Typical PCB Layout Example for TPS1210-Q1 With B2B MOSFETs

# 11 Device and Documentation Support

#### 11.1 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击*通知* 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

#### 11.2 支持资源

TI E2E™中文支持论坛是工程师的重要参考资料,可直接从专家处获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题,获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的使用条款。

#### 11.3 Trademarks

TI E2E™ is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

#### 11.4 静电放电警告

静电放电 (ESD) 会损坏这个集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理和安装程序,可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

#### 11.5 术语表

TI术语表本术语表列出并解释了术语、首字母缩略词和定义。

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLUSEZ2

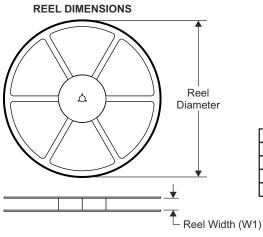

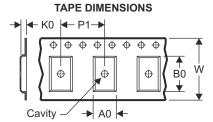

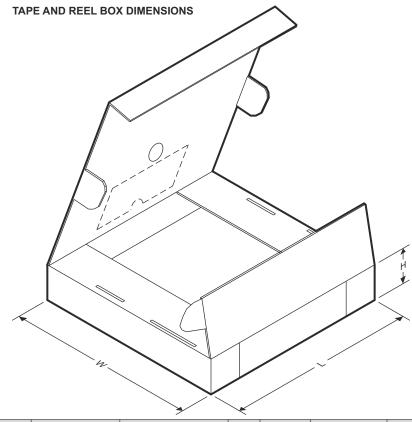

# 12.1 Tape and Reel Information

| Α0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

|    |                                                           |

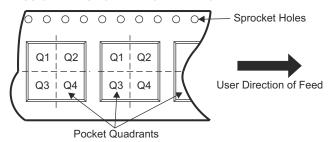

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device           | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| PTPS12100QDGXRQ1 | VSSOP           | DGX                | 19   | 5000 | 330.0                    | 16.4                     | 5.4        | 5.4        | 1.45       | 8.0        | 16.0      | Q1               |

| PTPS12101QDGXRQ1 | VSSOP           | DGX                | 19   | 5000 | 330.0                    | 16.4                     | 5.4        | 5.4        | 1.45       | 8.0        | 16.0      | Q1               |

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| PTPS12100QDGXRQ1 | VSSOP        | DGX             | 19   | 5000 | 356.0       | 356.0      | 35.0        |

| PTPS12101QDGXRQ1 | VSSOP        | DGX             | 19   | 5000 | 356.0       | 356.0      | 35.0        |

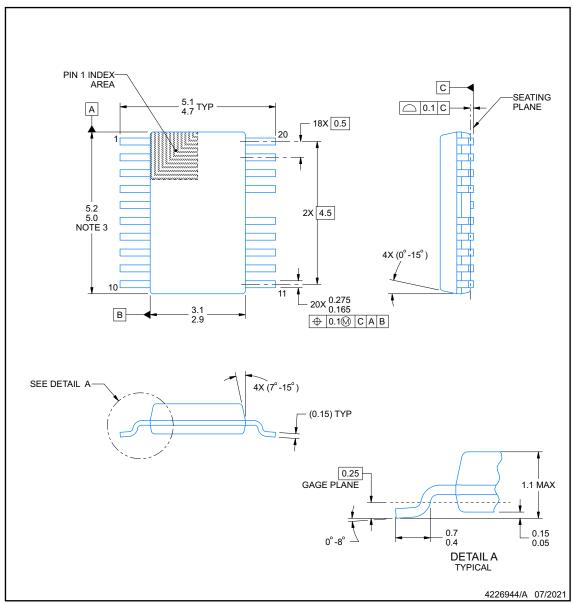

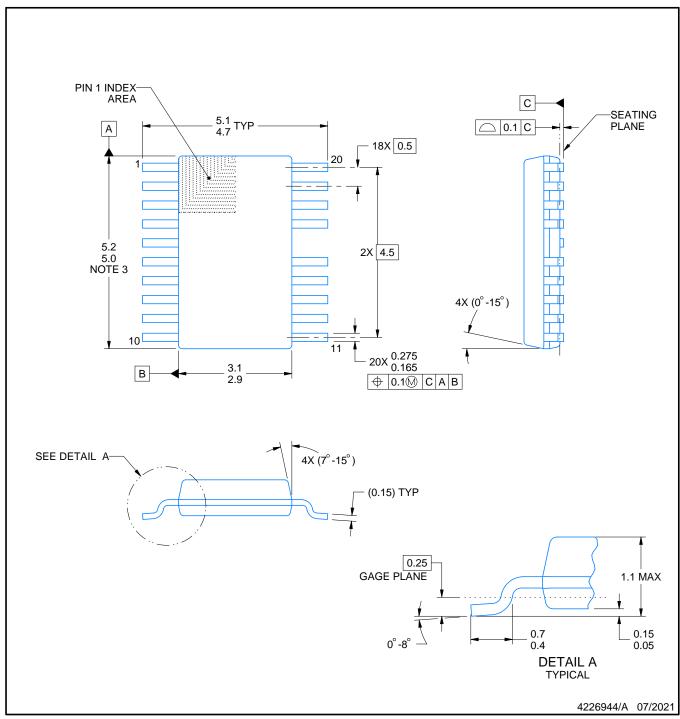

**DGX0019A**

#### **PACKAGE OUTLINE**

# VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing

- per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- 4. No JEDEC registration as of July 2021.

- 5. Features may differ or may not be present.

Product Folder Links: TPS1210-Q1

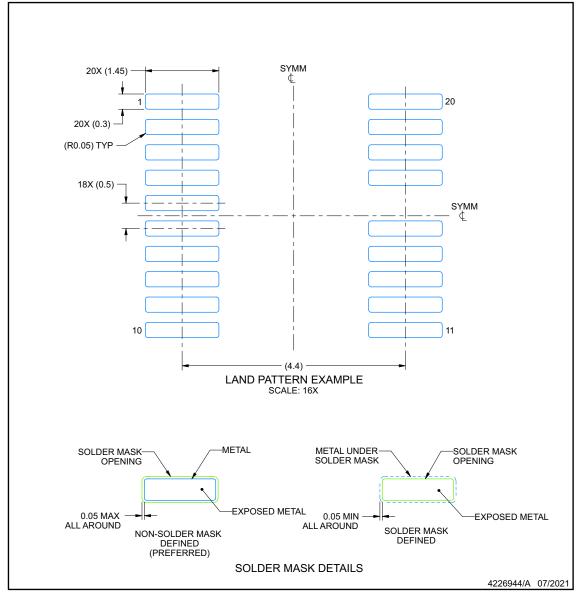

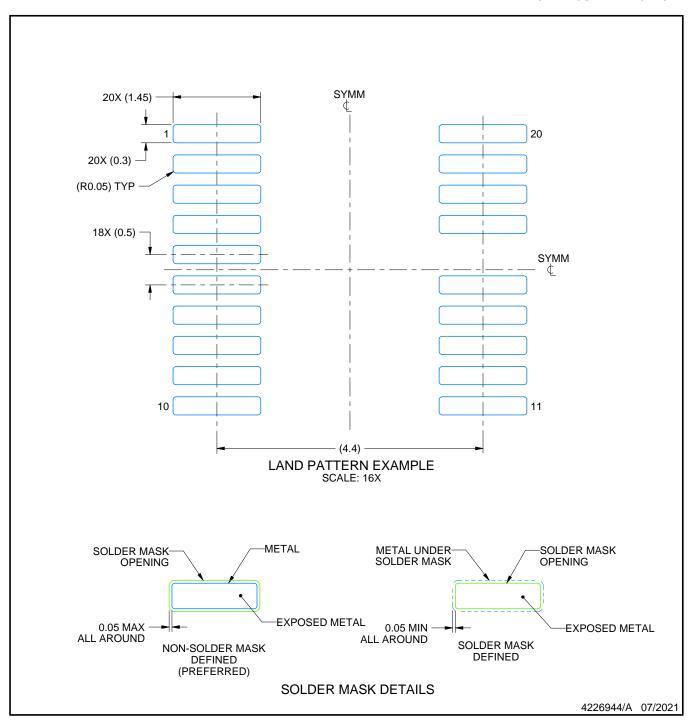

# **EXAMPLE BOARD LAYOUT**

# **DGX0019A**

VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

10. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

Copyright © 2023 Texas Instruments Incorporated

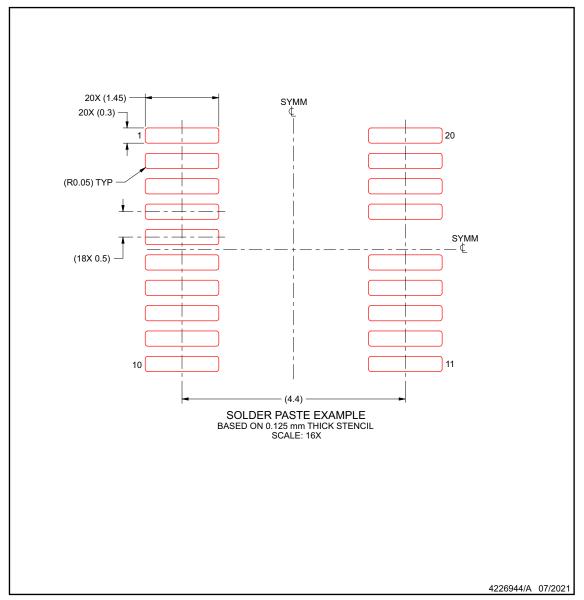

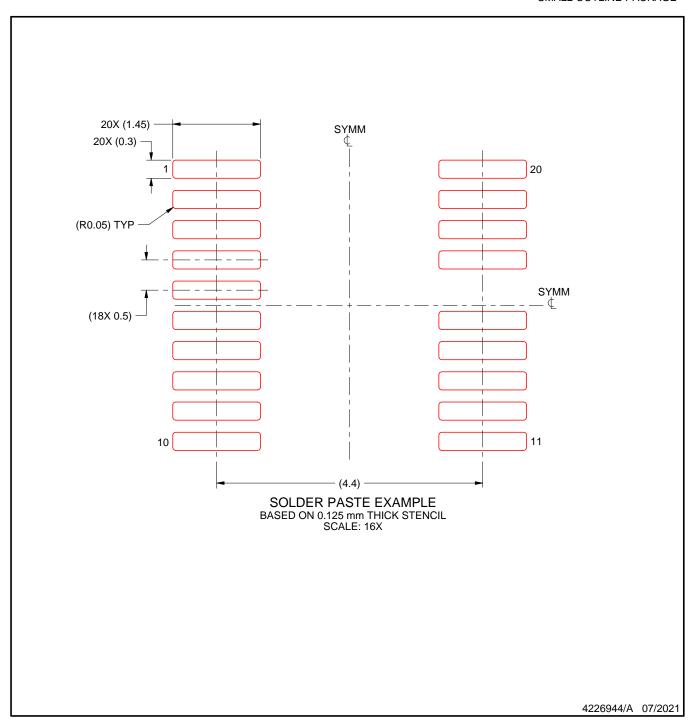

# **EXAMPLE STENCIL DESIGN**

# **DGX0019A**

VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

www.ti.com 1-Dec-2023

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan | Lead finish/<br>Ball material | MSL Peak Temp | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------|-------------------------------|---------------|--------------|-------------------------|---------|

| PTPS12100QDGXRQ1 | ACTIVE | VSSOP        | DGX                | 19   | 5000           | TBD      | Call TI                       | Call TI       | -40 to 125   |                         | Samples |

| PTPS12101QDGXRQ1 | ACTIVE | VSSOP        | DGX                | 19   | 5000           | TBD      | Call TI                       | Call TI       | -40 to 125   |                         | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE OPTION ADDENDUM**

www.ti.com

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. No JEDEC registration as of July 2021.

5. Features may differ or may not be present.

SMALL OUTLINE PACKAGE

#### NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

- Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司