**ADVANCE INFORMATION**

TPS2HB50-Q1 40V、50mΩ 双通道智能高侧开关

### 1 特性

- 符合汽车类 应用要求

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 1:环境工作温度范围 T<sub>A</sub> = -40°C 至 125°C

- 器件 HBM ESD 分类等级 2

- 器件 CDM ESD 分类等级 C4B

- 可承受 40V 负载突降

- 具有  $50m\Omega$   $R_{ON}$   $(T_J = 25^{\circ}C)$  的双通道智能高侧开 关

- 通过可调电流限制提高系统级可靠性

- 电流限制可调范围为 1.6A 至 18A

- 强大的集成输出保护:

- 集成热保护

- 接地短路或电池短路保护

- 反向电池事件保护包括电压反向时自动启动

- 发生失电或接地失效时自动关闭

- 集成输出钳位对电感负载进行消磁

- 可配置故障处理

- 可对模拟检测输出进行配置,以精确测量:

- 负载电流

- 器件温度

- 通过 SNS 引脚提供故障指示

- 开路负载和电池短路检测

### 2 应用

- 信息娱乐显示屏

- ADAS 模块

- 加热元件:

- 座椅加热器

- 火花塞

- 油箱加热器

- 变速器控制单元

- HVAC 空调

- 车身控制模块

- 白炽灯和 LED 照明

### 3 说明

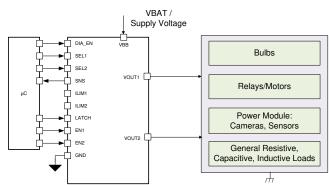

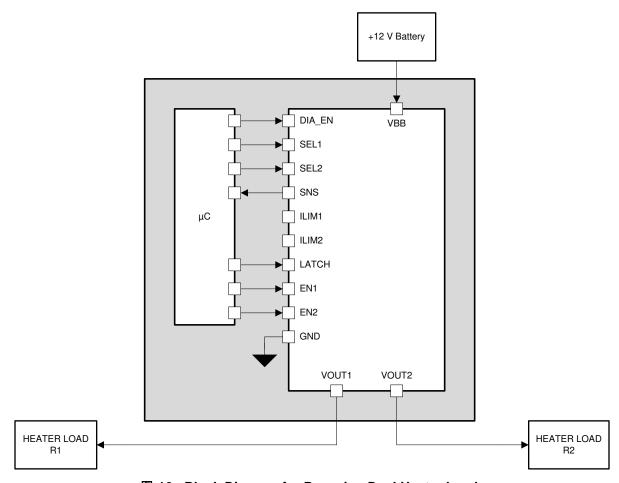

TPS2HB50-Q1 器件是一款适用于 12V 汽车系统的双通道智能高侧开关。该器件集成了强大的保护和诊断功能,以确保即使在汽车系统中发生短路等有害事件时也能提供输出端口保护。该器件通过可靠的电流限制来防止故障,根据器件型号不同,电流限制可调范围为1.6A 至 18A。凭借较高的电流限制范围,该器件可用于需要大瞬态电流的负载,而低电流限制范围可为不需要高峰值电流的负载提供更好的保护。该器件能够可靠地驱动各种负载分布。

TPS2HB50-Q1 还能够提供可改进负载诊断的高精度模拟电流检测。通过向系统 MCU 报告负载电流和器件温度,该器件可实现预测性维护和负载诊断,从而延长系统寿命。

TPS2HB50-Q1 采用 HTSSOP 封装,可减小 PCB 尺寸。

### 器件信息(1)

| 器件型号        | 封装          | 封装尺寸(标称值)       |

|-------------|-------------|-----------------|

| TPS2HB50-Q1 | HTSSOP (16) | 5.00mm × 4.40mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

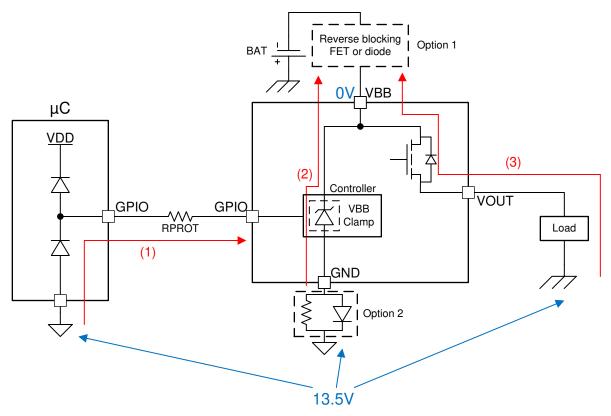

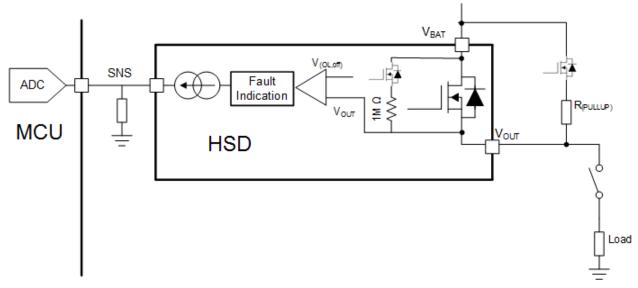

#### 简化原理图

| <b>J</b> /1 | Texas              |

|-------------|--------------------|

| Y           | <b>INSTRUMENTS</b> |

|                                                                                                                                                                                                                                                                                             | 目录 |                |                              |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------|------------------------------|----------|

| Device Comparison Table3Pin Configuration and Functions46.1 Recommended Connections for Unused Pins5Specifications67.1 Absolute Maximum Ratings67.2 ESD Ratings67.3 Recommended Operating Conditions67.4 Thermal Information77.5 Electrical Characteristics77.6 SNS Timing Characteristics9 |    | 10<br>11<br>12 | 9.2 Functional Block Diagram |          |

| Parameter Measurement Information                                                                                                                                                                                                                                                           |    | 14             | 13.5 静电放电警告                  | 36<br>36 |

|                                                                                                                                                                                                                                                                                             | 应用 | 特性             | 特性                           | 特性       |

# 4 修订历史记录

| C | Changes from Original (February 2018) to Revision A |  |

|---|-----------------------------------------------------|--|

| • | 对整篇数据表进行了更改                                         |  |

# 5 Device Comparison Table

# Table 1. TPS2HB50-Q1 Device Options

| Device<br>Version | Part Number           | Current Limit         | Current Limit Range | Overcurrent Behavior       |  |  |

|-------------------|-----------------------|-----------------------|---------------------|----------------------------|--|--|

| Α                 | TPS2HB50 <b>A</b> -Q1 | Resistor Programmable | 1.6 A - 8 A         | Disable switch immediately |  |  |

| В                 | TPS2HB50 <b>B</b> -Q1 | Resistor Programmable | 3.6 A - 18 A        | Disable switch immediately |  |  |

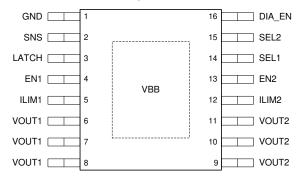

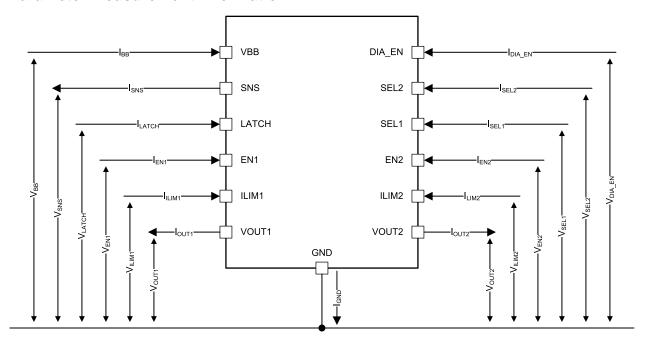

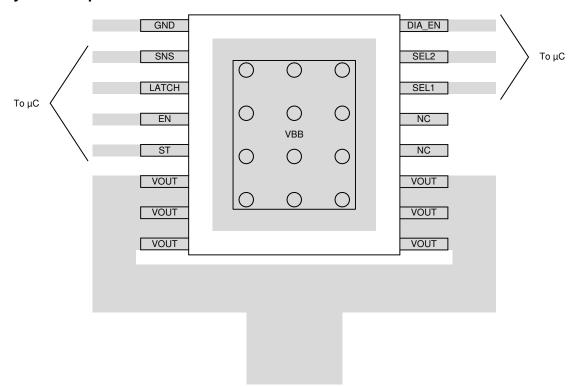

# 6 Pin Configuration and Functions

#### PWP Package 16-Pin HTSSOP Top View

### **Pin Functions**

| PIN         |        | 1/0 | DESCRIPTION                                                                       |  |  |

|-------------|--------|-----|-----------------------------------------------------------------------------------|--|--|

| NO.         | NAME   | 1/0 | DESCRIPTION                                                                       |  |  |

| 1           | GND    | _   | Device ground                                                                     |  |  |

| 2           | SNS    | 0   | ense output                                                                       |  |  |

| 3           | LATCH  | ı   | ets fault handling behavior (latched or auto-retry)                               |  |  |

| 4           | EN1    | ı   | Channel 1 control input, active high                                              |  |  |

| 5           | ILIM1  | 0   | Connect pull-up resistor to V <sub>BB</sub> to set current-limit threshold on CH1 |  |  |

| 6-8         | VOUT1  | 0   | hannel 1 output                                                                   |  |  |

| 9-11        | VOUT2  | 0   | Channel 2 output                                                                  |  |  |

| 12          | ILIM2  | 0   | Connect pull-up resistor to V <sub>BB</sub> to set current-limit threshold on CH2 |  |  |

| 13          | EN2    | ı   | Channel 2 control input, active high                                              |  |  |

| 14          | SEL1   | ı   | Diagnostics select 1                                                              |  |  |

| 15          | SEL2   | ı   | Diagnostics select 2                                                              |  |  |

| 16          | DIA_EN | I   | Diagnostic enable, active high                                                    |  |  |

| Exposed pad | VBB    | I   | Power supply input                                                                |  |  |

## 6.1 Recommended Connections for Unused Pins

The TPS2HB50-Q1 device is designed to provide an enhanced set of diagnostic and protection features. However, if the system design only allows for a limited number of I/O connections, some pins may be considered optional.

**Table 2. Connections for Optional Pins**

| PIN NAME                         | CONNECTION IF NOT USED                             | IMPACT IF NOT USED                                                                                                                                                                                                                               |

|----------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SNS Ground through 1-kΩ resistor |                                                    | Analog sense is not available.                                                                                                                                                                                                                   |

| LATCH                            | Float or ground through R <sub>PROT</sub> resistor | With LATCH unused, the device will auto-retry after a fault. If latched behavior is desired, but the system describes limited I/O, it is possible to use one microcontroller output to control the latch function of several high-side channels. |

|                                  |                                                    | If the ILIMx pin is left floating, the device will be set to the default internal current-limit threshold.                                                                                                                                       |

| SEL1                             | Float or ground through R <sub>PROT</sub> resistor | SEL1 selects the $T_J$ sensing feature. With SEL1 unused, only CH1 and CH2 current sensing and open load detection are available.                                                                                                                |

| SEL 9                            |                                                    | With SEL2 = 0 V, CH2 current sensing and CH2 open load detection are not available.                                                                                                                                                              |

| DIA_EN                           | Float or ground through R <sub>PROT</sub> resistor | With DIA_EN unused, the analog sense, open-load, and short-to-battery diagnostics are not available.                                                                                                                                             |

$R_{PROT}$  is used to protect the pins from excess current flow during reverse battery conditions, for more information please see the section on *Reverse Battery* protection.

### 7 Specifications

### 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                 |                                                                                               | MIN | MAX                | UNIT |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----|--------------------|------|

| Maximum continuous supply voltage, V <sub>BB</sub>              |                                                                                               |     | 36                 | V    |

| Load dump voltage, V <sub>LD</sub>                              | ISO16750-2:2010(E)                                                                            |     | 40                 | V    |

| Reverse battery voltage, V <sub>Rev</sub> , t ≤ 3 minutes       | •                                                                                             | -18 |                    | V    |

| Enable pin voltage, V <sub>EN1</sub> and V <sub>EN2</sub>       |                                                                                               | -1  | 7                  | V    |

| LATCH pin voltage, V <sub>LATCH</sub>                           |                                                                                               | -1  | 7                  | V    |

| Diagnostic Enable pin voltage, V <sub>DIA_EN</sub>              |                                                                                               | -1  | 7                  | V    |

| Sense pin voltage, V <sub>SNS</sub>                             |                                                                                               | -1  | 18                 | V    |

| Select pin voltage, V <sub>SEL1</sub> and V <sub>SEL2</sub>     |                                                                                               | -1  | 7                  | V    |

| Reverse ground current, I <sub>GND</sub>                        | V <sub>BB</sub> < 0 V                                                                         |     | -50                | mA   |

| Energy dissipation during turnoff, E <sub>TOFF</sub>            | Single pulse, one channel, $L_{OUT} = 5$ mH, $T_{J,start} = 125$ °C                           |     | TBD <sup>(2)</sup> | mJ   |

| Energy dissipation during turnoff, E <sub>TOFF</sub>            | Repetitive pulse, one channel, $L_{OUT} = 5 \text{ mH}$ , $T_{J,start} = 125^{\circ}\text{C}$ |     | TBD <sup>(2)</sup> | mJ   |

| Maximum junction temperature, T <sub>J</sub>                    |                                                                                               |     | 150                | °C   |

| Maximum junction temperature - limited duration, T <sub>J</sub> | t < 100 hours                                                                                 |     | 170                | °C   |

| Storage temperature, T <sub>stg</sub>                           |                                                                                               | -65 | 150                | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |               |                                                         |                               |       | UNIT |

|--------------------|---------------|---------------------------------------------------------|-------------------------------|-------|------|

|                    | Electrostatic | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | All pins except VBB and VOUTx | ±2000 |      |

| V <sub>(ESD)</sub> | discharge     |                                                         | VBB and VOUTx                 | ±4000 | V    |

|                    |               | Charged-device model (CDM), per AEC Q100-011            | All pins                      | ±750  |      |

<sup>(1)</sup> AEC-Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specifications.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted) (1)

|                                        |                                        | MIN | MAX | UNIT |

|----------------------------------------|----------------------------------------|-----|-----|------|

| $V_{BB}$                               | Nominal supply voltage (1)             | 6   | 18  | V    |

| $V_{BB}$                               | Extended supply voltage <sup>(2)</sup> | 3   | 28  | V    |

| V <sub>EN1</sub> ,<br>V <sub>EN2</sub> | Enable voltage                         | -1  | 5.5 | V    |

| $V_{LATCH}$                            | LATCH voltage                          | -1  | 5.5 | V    |

| $V_{DIA\_EN}$                          | Diagnostic Enable voltage              | -1  | 5.5 | V    |

| $V_{SEL1}$ , $V_{SEL2}$                | Select voltage                         | -1  | 5.5 | V    |

| V <sub>SNS</sub>                       | Sense voltage                          | -1  | 7   | V    |

| T <sub>A</sub>                         | Operating free-air temperature         | -40 | 125 | °C   |

<sup>(1)</sup> All operating voltage conditions are measured with respect to device GND

<sup>(2)</sup> For further details, see the section regarding switch-off of an inductive load.

<sup>(2)</sup> Device will function within extended operating range, however some parametric values might not apply

### 7.4 Thermal Information

|                        |                                              | TPS2HB50-Q1  |      |

|------------------------|----------------------------------------------|--------------|------|

|                        | THERMAL METRIC <sup>(1)(2)</sup>             | PWP (HTSSOP) | UNIT |

|                        |                                              | 16 PINS      |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 32.9         | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 30.8         | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 9.0          | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 1.8          | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 9.2          | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 2.0          | °C/W |

- (1) For more information about traditional and new thermal metrics, see Tl's SPRA953 application report.

- (2) The thermal parameters are based on a 4-layer PCB according to the JESD51-5 and JESD51-7 standards.

### 7.5 Electrical Characteristics

$V_{BB} = 6 \text{ V to } 18 \text{ V}, T_{J} = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                      | PARAMETER                                      | TEST CONDITIONS                                                                                                               | MIN | TYP  | MAX | UNIT      |

|----------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-----------|

| INPUT VOL            | TAGE AND CURRENT                               |                                                                                                                               |     |      |     |           |

| V <sub>DSCLAMP</sub> | V <sub>DS</sub> clamp voltage                  |                                                                                                                               | 38  |      | 46  | V         |

| V <sub>BBCLAMP</sub> | V <sub>BB</sub> clamp voltage                  |                                                                                                                               | 58  |      | 76  | V         |

| V <sub>UVLOF</sub>   | V <sub>BB</sub> undervoltage lockout falling   | Measured with respect to the GND pin of the device                                                                            | 2.0 |      | 3   | V         |

| V <sub>UVLOR</sub>   | V <sub>BB</sub> undervoltage lockout rising    | Measured with respect to the GND pin of the device                                                                            | 2.2 |      | 3   | V         |

| ı                    | Standby current (total                         | $V_{BB} = 13.5 \text{ V}, T_{J} = 25^{\circ}\text{C}$<br>$V_{ENx} = V_{DIA\_EN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}$         |     |      | 0.5 | μΑ        |

| SB                   | device leakage including both MOSFET channels) | $V_{BB} = 13.5 \text{ V}, T_{J} = 125^{\circ}\text{C},$<br>$V_{ENx} = V_{DIA\_EN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}$       |     |      | 4   | μΑ        |

|                      | Continuous load current,                       | Two channels enabled, T <sub>AMB</sub> = 70°C                                                                                 |     | 3    |     | Α         |

| L <sub>NOM</sub>     | per channel                                    | One channel enabled, T <sub>AMB</sub> = 70°C                                                                                  |     | 4.5  |     | Α         |

|                      | Output leakage current (per channel)           | $V_{BB} = 13.5 \text{ V}, T_{J} = 25^{\circ}\text{C}$<br>$V_{ENx} = V_{DIA\_EN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}$         |     | 0.01 | 0.5 | μΑ        |

| OUT(standby)         |                                                | $V_{BB} = 13.5 \text{ V}, T_{J} = 125^{\circ}\text{C}$<br>$V_{ENx} = V_{DIA\_EN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}$        |     |      | 1.5 | μΑ        |

| I <sub>DIA</sub>     | Current consumption in diagnostic mode         | $V_{BB} = 13.5 \text{ V}, I_{SNS} = 0 \text{ mA}$<br>$V_{ENx} = 0 \text{ V}, V_{DIA\_EN} = 5 \text{ V}, V_{OUT} = 0 \text{V}$ |     | 3    | 6   | mA        |

| la                   | Quiescent current                              | $V_{BB} = 13.5 \text{ V}$<br>$V_{ENx} = V_{DIA\_EN} = 5 \text{ V}, I_{OUTx} = 0 \text{ A}$                                    |     | 3    | 6   | mA        |

| t <sub>STBY</sub>    | Standby mode delay time                        | $V_{ENx} = V_{DIA\_EN} = 0 V $ to standby                                                                                     | 12  | 17   | 22  | ms        |

| RON CHAR             | ACTERISTICS                                    |                                                                                                                               |     |      |     |           |

|                      | On-resistance                                  | $T_J = 25$ °C, 6 V $\leq V_{BB} \leq 28$ V, $I_{OUT1} = I_{OUT2} > 1$ A                                                       |     | 50   |     | mΩ        |

| R <sub>ON</sub>      | (Includes MOSFET and                           | $T_J = 150$ °C, 6 V $\leq V_{BB} \leq 28$ V, $I_{OUT1} = I_{OUT2} > 1$ A                                                      |     |      | 100 | mΩ        |

|                      | package)                                       | $T_J = 25$ °C, 3 V $\leq V_{BB} \leq 6$ V, $I_{OUT1} = I_{OUT2} > 1$ A                                                        |     |      | 75  | $m\Omega$ |

|                      | On-resistance during                           | $T_{J} = 25^{\circ}C, -18 \text{ V} \le V_{BB} \le -7 \text{ V}$                                                              |     | 50   |     | mΩ        |

| R <sub>ON(REV)</sub> | reverse polarity                               | $T_{J} = 105^{\circ}C, -18 \text{ V} \le V_{BB} \le -7 \text{ V}$                                                             |     |      | 100 | mΩ        |

| CURRENT              | SENSE CHARACTERISTIC                           | :s                                                                                                                            |     |      |     |           |

| K <sub>SNS</sub>     | Current sense ratio                            | I <sub>OUTX</sub> = 1 A                                                                                                       |     | 1500 |     |           |

### **Electrical Characteristics (continued)**

|                        | PARAMETER                                                   | TEST CO                                                                                                                                     | ONDITIONS                                          | MIN   | TYP   | MAX  | UNIT    |

|------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------|-------|------|---------|

|                        |                                                             |                                                                                                                                             |                                                    |       | 4.000 |      | mA      |

|                        |                                                             |                                                                                                                                             | $I_{OUT} = 6 A$                                    | -4%   |       | 4%   | %       |

|                        |                                                             |                                                                                                                                             |                                                    |       | 2.000 |      | mA      |

|                        |                                                             |                                                                                                                                             | I <sub>OUT</sub> = 3 A                             | -4%   |       | 4%   | %       |

|                        |                                                             |                                                                                                                                             |                                                    |       | 0.667 |      | mA      |

|                        | Current sense current                                       | $V_{EN} = V_{DIA EN} = 5 V$                                                                                                                 | I <sub>OUT</sub> = 1 A                             | -4%   |       | 4%   | %       |

| I <sub>SNSI</sub>      | and accuracy                                                | $V_{SEL1} = 0 \text{ V}, V_{SEL2} = X$                                                                                                      |                                                    |       | 0.2   |      | mA      |

|                        |                                                             |                                                                                                                                             | I <sub>OUT</sub> = 300 mA                          | -10%  |       | 10%  | %       |

|                        |                                                             |                                                                                                                                             |                                                    |       | 0.067 |      | mA      |

|                        |                                                             |                                                                                                                                             | I <sub>OUT</sub> = 100 mA                          | -25%  |       | 25%  | %       |

|                        |                                                             |                                                                                                                                             |                                                    |       | 0.033 |      | mA      |

|                        |                                                             |                                                                                                                                             | $I_{OUT} = 50 \text{ mA}$                          | -35%  |       | 35%  | %       |

| T.J SENSE              | CHARACTERISTICS                                             |                                                                                                                                             |                                                    | 0070  |       | 0070 | 70      |

| 52.102                 |                                                             |                                                                                                                                             | T <sub>J</sub> = -40°C                             | 0.00  | 0.12  | 0.29 | mA      |

|                        |                                                             |                                                                                                                                             | $T_J = 25^{\circ}C$                                | 0.68  | 0.12  | 1.02 | mA      |

| Ісыст                  | Temperature sense                                           | $V_{DIA\_EN} = 5 V$ , $V_{SEL1} = 5$                                                                                                        | $T_J = 85^{\circ}C$                                | 1.25  | 1.52  | 1.79 | mA      |

| ISNST                  | current                                                     | V, V <sub>SEL2</sub> = 0 V                                                                                                                  | $T_J = 65^{\circ}C$                                | 1.61  | 1.96  | 2.31 | mA      |

|                        |                                                             |                                                                                                                                             | $T_J = 123 \text{ C}$ $T_J = 150 \text{ °C}$       | 1.80  | 2.25  | 2.70 | mA      |

| dl <sub>SNST</sub> /dT | Coefficient                                                 |                                                                                                                                             | 1,1 = 100 0                                        | 1.00  | 0.011 | 2.10 | mA/°C   |

|                        | RACTERISTICS                                                |                                                                                                                                             |                                                    |       | 0.011 |      | 1117V C |

| I <sub>SNSFH</sub>     | I <sub>SNS</sub> fault high-level                           | V <sub>DIA EN</sub> = 5 V, V <sub>SEL1</sub> = 0 \                                                                                          | /, V <sub>SFL2</sub> = X                           | 4     | 4.5   | 5.3  | mA      |

| I <sub>SNSleak</sub>   | I <sub>SNS</sub> leakage                                    | $V_{DIA\_EN} = 0 \text{ V}$                                                                                                                 | JLLL                                               |       |       | 1    | μA      |

|                        | LIMIT CHARACTERISTICS                                       | *                                                                                                                                           |                                                    | 1     |       |      |         |

|                        |                                                             | Device Version A, T <sub>J</sub> =                                                                                                          | R <sub>ILIM</sub> = GND, open, or out of range     |       | 11.8  |      | Α       |

|                        |                                                             | -40°C to 150°C                                                                                                                              | $R_{ILIM} = 5 \text{ k}\Omega$                     | 6.2   | 8     | 9.36 | Α       |

|                        | 0                                                           |                                                                                                                                             | $R_{ILIM} = 25 \text{ k}\Omega$                    | 1.4   | 1.6   | 2.28 | Α       |

| I <sub>CL</sub>        | Current Limit Threshold                                     | Device Version B, T <sub>J</sub> =                                                                                                          | R <sub>ILIM</sub> = GND, open, or out of range     |       | 27    |      | Α       |

|                        |                                                             | -40°C to 150°C                                                                                                                              | $R_{ILIM} = 5 \text{ k}\Omega$                     | 13.68 | 18    | 21.6 | Α       |

|                        |                                                             |                                                                                                                                             | $R_{ILIM} = 25 \text{ k}\Omega$                    | 2.96  | 3.6   | 4.44 | Α       |

| 14                     | 0                                                           | Version A                                                                                                                                   | 1                                                  | 31    | 40    | 57   | A * kΩ  |

| K <sub>CL</sub>        | Current Limit Ratio                                         | Version B                                                                                                                                   |                                                    | 68.4  | 90    | 111  | A * kΩ  |

| FAULT CH               | IARACTERISTICS                                              | 1                                                                                                                                           |                                                    | 1     |       |      |         |

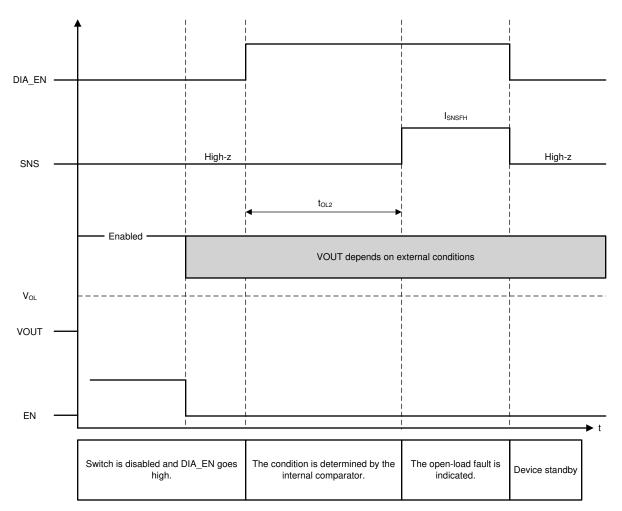

| V <sub>OL</sub>        | Open-load (OL) detection voltage                            | V <sub>ENx</sub> = 0 V, V <sub>DIA_EN</sub> = 5 V                                                                                           |                                                    | 2     | 3     | 4    | V       |

| t <sub>OL1</sub>       | OL and STB indication-<br>time from ENx falling             | $V_{ENx} = 5 \text{ V to 0 V, } V_{DIA\_EN}$<br>$I_{OUT} = 0 \text{ mA, } V_{OUTx} = 4 \text{ V}$                                           |                                                    | 300   | 500   | 700  | μs      |

| t <sub>OL2</sub>       | OL and STB indication-<br>time from DIA_EN rising           | $V_{ENx} = 0 \text{ V, } V_{DIA\_EN} = 0 \text{ V to 5 V, } V_{SEL1} = 0 \text{ V}^{(1)}$ $I_{OUT} = 0 \text{ mA, } V_{OUTx} = 4 \text{ V}$ |                                                    |       |       | 50   | μs      |

| t <sub>OL3</sub>       | OL and STB indication-<br>time from V <sub>OUT</sub> rising | $V_{ENx} = 0 \text{ V}, V_{DIA\_EN} = 5 \text{ V}$<br>$I_{OUT} = 0 \text{ mA}, V_{OUTx} = 0 \text{ V}$                                      | , V <sub>SEL1</sub> = 0 V <sup>(1)</sup><br>to 4 V |       |       | 50   | μs      |

| T <sub>ABS</sub>       | Thermal shutdown                                            |                                                                                                                                             |                                                    | 150   |       |      | °C      |

| T <sub>REL</sub>       | Relative thermal shutdown                                   |                                                                                                                                             |                                                    |       | 50    |      | °C      |

| T <sub>HYS</sub>       | Thermal shutdown hysteresis                                 |                                                                                                                                             |                                                    |       | 28    |      | °C      |

|                        |                                                             | ·                                                                                                                                           |                                                    |       |       |      |         |

SELx must be set to select the relevant channel. Diagnostics are performed on Channel 1 when SELx = 00 and diagnostics are performed on channel 2 when SELx =01

### **Electrical Characteristics (continued)**

$V_{BB} = 6 \text{ V}$  to 18 V,  $T_{J} = -40 ^{\circ}\text{C}$  to 150  $^{\circ}\text{C}$  (unless otherwise noted)

|                               | PARAMETER                      | TEST CO                                                                                                          | NDITIONS | MIN | TYP | MAX | UNIT      |

|-------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------|----------|-----|-----|-----|-----------|

| t <sub>FAULT</sub>            | Fault shutdown indication-time | V <sub>DIA_EN</sub> = 5 V<br>Time between switch shutdown and I <sub>SNS</sub> settling at<br>I <sub>SNSFH</sub> |          |     |     | 50  | μs        |

| t <sub>RETRY</sub>            | Retry time                     | Time from fault shutdown (thermal shutdown or curre                                                              |          | 1   | 2   | 3   | ms        |

| EN1 AND E                     | N2 PIN CHARACTERISTIC          | CS <sup>(2)</sup>                                                                                                | ·        |     |     | ·   |           |

| V <sub>IL, ENx</sub>          | Input voltage low-level        | No GND network diode                                                                                             |          |     |     | 0.8 | V         |

| V <sub>IH, ENx</sub>          | Input voltage high-level       | No GND network diode                                                                                             |          | 2   |     |     | V         |

| V <sub>IHYS, ENx</sub>        | Input voltage hysteresis       |                                                                                                                  |          |     | 350 |     | mV        |

| R <sub>ENx</sub>              | Internal pulldown resistor     |                                                                                                                  |          | 0.5 | 1   | 2   | ΜΩ        |

| I <sub>IL, EN</sub>           | Input current low-level        | V <sub>EN</sub> = 0.8 V                                                                                          |          |     | 0.8 |     | μΑ        |

| I <sub>IH, EN</sub>           | Input current high-level       | V <sub>EN</sub> = 5 V                                                                                            |          |     | 5   |     | μΑ        |

| DIA_EN PII                    | CHARACTERISTICS (2)            |                                                                                                                  |          |     |     |     |           |

| V <sub>IL, DIA_EN</sub>       | Input voltage low-level        | No GND network diode                                                                                             |          |     |     | 0.8 | V         |

| V <sub>IH, DIA_EN</sub>       | Input voltage high-level       | No GND network diode                                                                                             |          | 2.0 |     |     | V         |

| V <sub>IHYS</sub> ,<br>DIA_EN | Input voltage hysteresis       |                                                                                                                  |          | 200 | 350 | 530 | mV        |

| R <sub>DIA_EN</sub>           | Internal pulldown resistor     |                                                                                                                  |          | 0.5 | 1   | 2   | ΜΩ        |

| I <sub>IL, DIA_EN</sub>       | Input current low-level        | $V_{DIA\_EN} = 0.8 \text{ V}$                                                                                    |          |     | 0.8 |     | μΑ        |

| I <sub>IH, DIA_EN</sub>       | Input current high-level       | $V_{DIA\_EN} = 5 V$                                                                                              |          |     | 5   |     | μΑ        |

| SEL1 AND                      | SEL2 PIN Characteristics       |                                                                                                                  |          |     |     |     |           |

| V <sub>IL, SELx</sub>         | Input voltage low-level        | No GND network diode                                                                                             |          |     |     | 0.8 | V         |

| V <sub>IH, SELx</sub>         | Input voltage high-level       | No GND network diode                                                                                             |          | 2   |     |     | V         |

| V <sub>IHYS, SELx</sub>       | Input voltage hysteresis       |                                                                                                                  |          |     | 350 |     | mV        |

| R <sub>SELx</sub>             | Internal pulldown resistor     |                                                                                                                  |          | 0.5 | 1   | 2   | $M\Omega$ |

| I <sub>IL, SELX</sub>         | Input current low-level        | V <sub>SELX</sub> = 0.8 V                                                                                        |          |     | 0.8 |     | μΑ        |

| I <sub>IH, SELX</sub>         | Input current high-level       | V <sub>SELX</sub> = 5 V                                                                                          |          |     | 5   |     | μΑ        |

| LATCH PIN                     | CHARACTERISTICS(2)             |                                                                                                                  |          |     |     |     |           |

| V <sub>IL, LATCH</sub>        | Input voltage low-level        | No GND network diode                                                                                             |          |     |     | 0.8 | V         |

| V <sub>IH, LATCH</sub>        | Input voltage high-level       | No GND network diode                                                                                             |          | 2   |     |     | V         |

| V <sub>IHYS,</sub>            | Input voltage hysteresis       |                                                                                                                  |          | 200 | 350 | 530 | mV        |

| R <sub>LATCH</sub>            | Internal pulldown resistor     |                                                                                                                  |          | 0.5 | 1   | 2   | $M\Omega$ |

| I <sub>IL, LATCH</sub>        | Input current low-level        | V <sub>LATCH</sub> = 0.8 V                                                                                       |          |     | 0.8 |     | μΑ        |

| I <sub>IH, LATCH</sub>        | Input current high-level       | V <sub>LATCH</sub> = 5 V                                                                                         |          |     | 5   |     | μA        |

<sup>(2)</sup>  $V_{BB} = 3 \text{ V to } 28 \text{ V}$

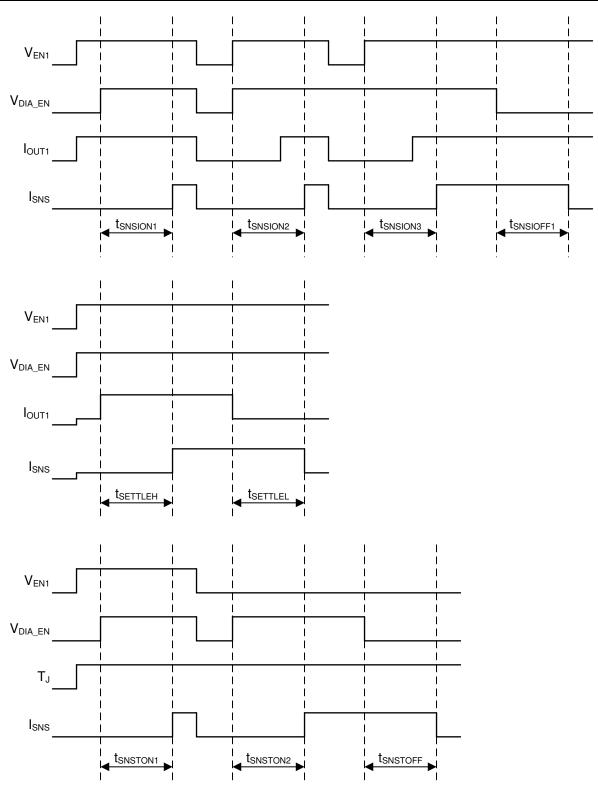

### 7.6 SNS Timing Characteristics

$V_{BB}$  = 6 V to 18 V,  $T_{J}$  = -40°C to +150°C (unless otherwise noted)

| PARAMETER                  |                                                  | TEST CONDITIONS                                                                                              | MIN | TYP | MAX | UNIT |  |  |

|----------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|

| SNS TIMING - CURRENT SENSE |                                                  |                                                                                                              |     |     |     |      |  |  |

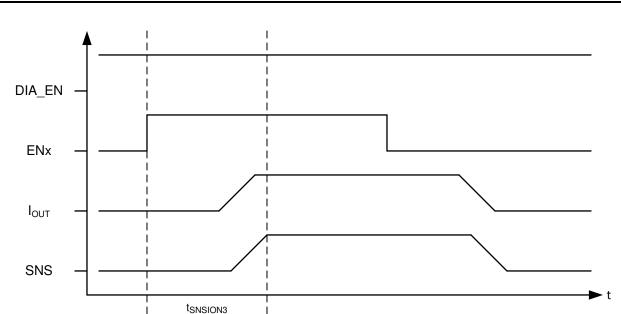

| t <sub>SNSION1</sub>       | Settling time from rising edge of DIA_EN         | $V_{ENx}$ = 5 V, $V_{DIA\_EN}$ = 0 V to 5 V $R_{SNS}$ = 1 k $\Omega$ , $R_L$ ≤ 6 $\Omega$                    |     |     | 40  | μs   |  |  |

| t <sub>SNSION2</sub>       | Settling time from rising edge of ENx and DIA_EN | $V_{ENx} = V_{DIA\_EN} = 0 \text{ V to 5 V}$<br>$R_{SNS} = 1 \text{ k}\Omega, R_L \le 6 \Omega$              |     |     | 165 | μs   |  |  |

| t <sub>SNSION3</sub>       | Settling time from rising edge of ENx            | $V_{ENx} = 0 \text{ V to 5 V}, V_{DIA\_EN} = 5 \text{ V}$<br>$R_{SNS} = 1 \text{ k}\Omega, R_L \le 6 \Omega$ |     |     | 165 | μs   |  |  |

# **SNS Timing Characteristics (continued)**

$V_{BB} = 6 \text{ V}$  to 18 V,  $T_{J} = -40^{\circ}\text{C}$  to +150°C (unless otherwise noted)

| PARAMETER             |                                                       | TEST CONDITIONS                                                                                                                                                       | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>SNSIOFF1</sub> | Settling time from falling edge of DIA_EN             | $V_{ENx}$ = 5 V, $V_{DIA\_EN}$ = 5 V to 0 V<br>$R_{SNS}$ = 1 k $\Omega$ , $R_L$ ≤ 6 $\Omega$                                                                          |     |     | 20  | μs   |

| t <sub>SETTLEH</sub>  | Settling time from rising edge of load step           | $V_{EN1} = 5 \text{ V}, V_{DIA\_EN} = 5 \text{ V}$<br>$R_{SNS} = 1 \text{ k}\Omega, I_{OUT} = 5 \text{ A to 1 A}$                                                     |     |     | 20  | μs   |

| t <sub>SETTLEL</sub>  | Settling time from falling edge of load step          | $V_{ENx} = 5 \text{ V}, V_{DIA\_EN} = 5 \text{ V}$<br>$R_{SNS} = 1 \text{ k}\Omega, I_{OUT} = 5 \text{ A to 1 A}$                                                     |     |     | 20  | μs   |

| SNS TIMIN             | IG - TEMPERATURE SENSE                                |                                                                                                                                                                       |     |     | •   |      |

| t <sub>SNSTON1</sub>  | Settling time from rising edge of DIA_EN              | $V_{ENx} = 5 \text{ V}, V_{DIA\_EN} = 0 \text{ V to } 5 \text{ V}$<br>$R_{SNS} = 1 \text{ k}\Omega$                                                                   |     |     | 40  | μs   |

| t <sub>SNSTON2</sub>  | Settling time from rising edge of DIA_EN              | $V_{ENx} = 0 \text{ V}, V_{DIA\_EN} = 0 \text{ V to 5 V}$<br>$R_{SNS} = 1 \text{ k}\Omega$                                                                            |     |     | 70  | μs   |

| t <sub>SNSTOFF</sub>  | Settling time from falling edge of DIA_EN             | $V_{ENx} = X$ , $V_{DIA\_EN} = 5$ V to 0 V<br>$R_{SNS} = 1$ k $\Omega$                                                                                                |     |     | 20  | μs   |

| SNS TIMIN             | IG - MULTIPLEXER                                      |                                                                                                                                                                       |     |     |     |      |

|                       | Settling time from temperature sense to current sense | $\begin{aligned} &V_{ENx} = X, \ V_{DIA\_EN} = 5 \ V \\ &V_{SEL1} = 5 \ V \ to \ 0 \ V, \ V_{SEL2} = X \\ &R_{SNS} = 1 \ k\Omega, \ R_L \le 6 \ \Omega \end{aligned}$ |     |     | 60  | μs   |

| t <sub>MUX</sub>      | Settling time from current sense on CHx to CHy        | $V_{ENx} = X$ , $V_{DIA\_EN} = 5 V$<br>$V_{SEL1} = 0 V$ , $V_{SEL2} = 0 V$ to 5 V<br>$R_{SNS} = 1 k\Omega$ , $I_{OUT1} = 2 A$ , $I_{OUT2} = 4 A$                      |     |     | 20  | μs   |

|                       | Settling time from current sense to temperature sense | $V_{ENx} = X$ , $V_{DIA\_EN} = 5 V$<br>$V_{SEL1} = 0 V to 5 V$ , $V_{SEL2} = X$<br>$R_{SNS} = 1 k\Omega$ , $R_L \le 6 \Omega$                                         |     |     | 60  | μs   |

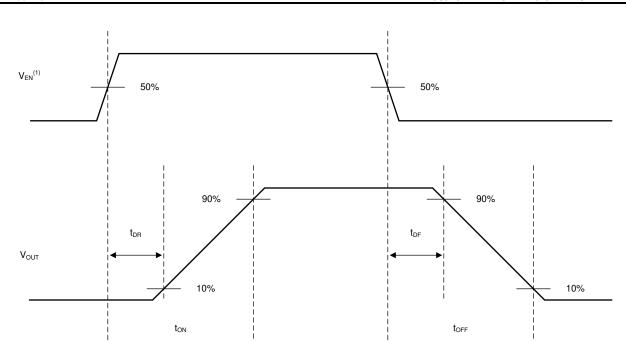

# 7.7 Switching Characteristics

$V_{BB}$  = 13.5 V,  $T_{J}$  = -40°C to +150°C (unless otherwise noted)

|                                    | PARAMETER                              | TEST CONDITIONS                                                                 | MIN | TYP | MAX | UNIT |

|------------------------------------|----------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>DR</sub>                    | Turnon delay time                      | $V_{BB}$ = 13.5 V, $R_L \le 6~\Omega$ , 50% EN rising to 10% $V_{OUT}$ rising   | 20  | 60  | 100 | μs   |

| t <sub>DF</sub>                    | Turnoff delay time                     | $V_{BB}$ = 13.5 V, $R_L \le 6~\Omega$ , 50% EN falling to 90% $V_{OUT}$ Falling | 20  | 60  | 100 | μs   |

| SR <sub>R</sub>                    | VOUTx rising slew rate                 | $V_{BB}$ = 13.5 V, 20% to 80% of $V_{OUT},$ $R_L \leq 6~\Omega$                 | 0.1 | 0.4 | 0.7 | V/µs |

| SR <sub>F</sub>                    | VOUTx falling slew rate                | $V_{BB}$ = 13.5 V, 80% to 20% of $V_{OUT},$ $R_L \leq 6~\Omega$                 | 0.1 | 0.4 | 0.7 | V/µs |

| t <sub>ON</sub>                    | Turnon time                            | $V_{BB}$ = 13.5 V, $R_L \le 6~\Omega$ , 50% EN rising to 80% $V_{OUT}$ rising   | 39  | 87  | 145 | μs   |

| t <sub>OFF</sub>                   | Turnoff time                           | $V_{BB}$ = 13.5 V, $R_{L} \le 6~\Omega$ , 50% EN rising to 80% $V_{OUT}$ rising | 39  | 87  | 147 | μs   |

| t <sub>ON</sub> - t <sub>OFF</sub> | Turnon and turnoff matching            | 200-µs enable pulse                                                             | -50 | 0   | 50  | μs   |

| E <sub>ON</sub>                    | Switching energy losses during turnon  | $V_{BB}$ = 13.5 V, $R_L \le 6 \Omega$                                           |     | 0.4 |     | mJ   |

| E <sub>OFF</sub>                   | Switching energy losses during turnoff | $V_{BB} = 13.5 \text{ V}, R_{L} \le 6 \Omega$                                   |     | 0.4 |     | mJ   |

**INSTRUMENTS**

(1) Rise and fall time of  $V_{\text{ENx}}$  is 100 ns.

图 1. Switching Characteristics Definitions

NOTE1: Rise and fall times of control signals are 100 ns. Control signals include: EN1, EN2, DIA\_EN, SEL1, SEL2.

NOTE2: SEL1 and SEL2 must be set to the appropriate values.

图 2. SNS Timing Characteristics Definitions

# 8 Parameter Measurement Information

图 3. Parameter Definitions

### 9 Detailed Description

#### 9.1 Overview

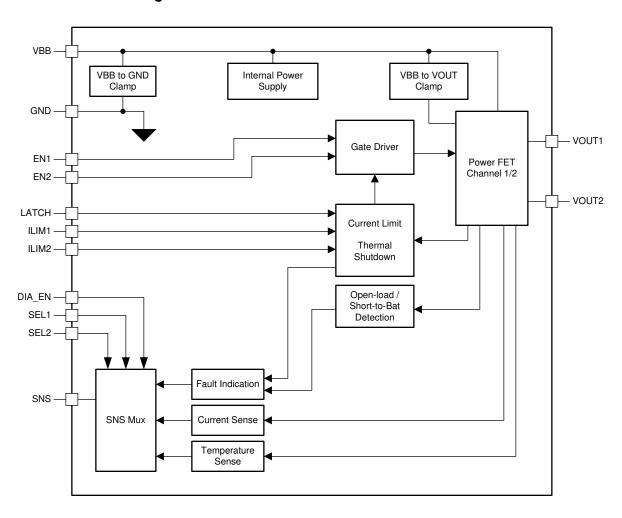

The TPS2HB50-Q1 device is a dual-channel smart high-side switch intended for use with 12-V automotive batteries. Many protection and diagnostic features are integrated in the device.

Diagnostics features include the analog SNS output that is capable of providing a signal that is proportional to load current or device temperature. The high-accuracy load current sense allows for diagnostics of complex loads.

This device includes protection through thermal shutdown, current limiting, transient withstand, and reverse battery operation. For more details on the protection features, refer to the *Feature Description* and *Application Information* sections of the document.

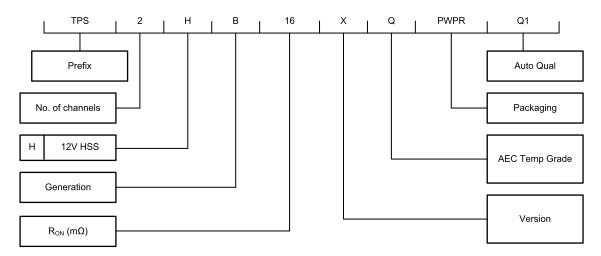

图 4. Naming Convention

# 9.2 Functional Block Diagram

**NSTRUMENTS**

### 9.3 Feature Description

#### 9.3.1 Protection Mechanisms

The TPS2HB50-Q1 is designed to operate in the automotive environment. The protection mechanisms allow the device to be robust against many system-level events such as load dump, reverse battery, short-to-ground, and more.

There are two protection features which, if triggered, will cause the switch to automatically disable:

- Thermal Shutdown

- Current Limit

When any of these protections are triggered, the device will enter the FAULT state. In the FAULT state, the fault indication will be available on the SNS pin (see the *Diagnostic Mechanisms* section of the data sheet for more details).

The switch is no longer held off and the fault indication is reset when all of the below conditions are met:

- LATCH pin is low

- t<sub>RFTRY</sub> has expired

- All faults are cleared (thermal shutdown, current limit)

注

CH1 and CH2 operate independently. If there is a fault on one channel, the other channel is not affected.

#### 9.3.1.1 Thermal Shutdown

The device includes a temperature sensor on each power FET and also within the controller portion of the device. There are two cases that the device will consider to be a thermal shutdown fault:

- $T_{J,FET} > T_{ABS}$

- $(T_{J,FET} T_{J,controller}) > T_{REL}$

After the fault is detected, the relevant switch will turn off. Each channel is turned off based on the measurement of temperature sensor for that channel. Therefore, if the thermal fault is detected on only one channel, the other channel continues operation. If  $T_{J,FET}$  passes  $T_{ABS}$ , the fault is cleared when the switch temperature decreases by the hysteresis value,  $T_{HYS}$ . If instead the  $T_{REL}$  threshold is exceeded, the fault is cleared after  $T_{RETRY}$  passes.

### 9.3.1.2 Current Limit

When  $I_{OUT}$  reaches the current limit threshold,  $I_{CL}$ , the channel will switch off immediately. The  $I_{CL}$  value will vary with slew rate and a fast current increase that occurs during a powered-on short circuit can temporarily go above the specified  $I_{CL}$  value. When the switch is in the FAULT state it will output an output current  $I_{SNSFH}$  on the SNS pin.

During a short circuit event, the device will hit the  $I_{CL}$  value that is listed in the Electrical Characteristics table (for the given device version and  $R_{ILIM}$ ) and then turn the output off to protect the device. The device will register a short circuit event when the output current exceeds  $I_{CL}$ , however the measured maximum current may exceed the  $I_{CL}$  value due to the TPS2HB50-Q1 deglitch filter and turn-off time. The device is guaranteed to protect itself during a short circuit event up to 24 V at 125°C.

#### 9.3.1.2.1 Current Limit Foldback

Version B of the TPS2HB50-Q1 implements a current limit foldback feature that is designed to protect the device in the case of a long-term fault condition. If the device undergoes fault shutdown events (either of thermal shutdown or current limit) seven consecutive times, the current limit will be reduced to half of the original value. The device will revert back to the original current limit threshold if either of the following occurs:

- The device goes to standby mode.

- The switch turns on and turns off without any fault occurring.

Version A does not implement the current limit foldback due to the lower current limit causing less harm during repetitive long-term faults.

#### 9.3.1.2.2 Programmable Current Limit

The TPS2HB50-Q1 includes an adjustable current limit. Some applications (for example, incandescent bulbs) will require a high current limit. Other applications can benefit from a lower current limit threshold. In general, wherever possible a lower current limit is recommended due to allowing system advantages through:

- Reduced size and cost in current carrying components such as PCB traces and module connectors

- Less disturbance at the power supply (V<sub>BB</sub> pin) during a short circuit event

- · Improved protection of the downstream load

To set the current limit threshold, connect a resistor from  $I_{LIM}$  to  $V_{BB}$ . The current limit threshold is determined by Equation 1 ( $R_{ILIM}$  in  $k\Omega$ ):

$$I_{CL} = K_{CL} / R_{ILIM}$$

(1)

The  $R_{ILIM}$  range is between 5 k $\Omega$  and 25 k $\Omega$ . An  $R_{ILIM}$  resistor is required, however in the fault case where the pin is floating, grounded, or outside of this range the current limit will default to an internal level that is defined in the *Specifications* section of this document.

注

Capacitance on the  $I_{LIM}$  pin can cause  $I_{LIM}$  to go out of range during short circuit events. For accurate current limiting, place  $R_{ILIM}$  near to the device with short traces to ensure <5 pF capacitance to GND on the  $I_{LIM}$  pin.

#### 9.3.1.2.3 Undervoltage Lockout (UVLO)

The device monitors the supply voltage  $V_{BB}$  to prevent unpredicted behaviors in the event that the supply voltage is too low. When the supply voltage falls down to  $V_{UVLOF}$ , the output stage is shut down automatically. When the supply rises up to  $V_{UVLOR}$ , the device turns back on.

During an initial ramp of  $V_{BB}$  from 0 V at a ramp rate slower than 1 V/ms,  $V_{EN}$  pin will have to be  $V_{BB}$  held low until V<sub>BB</sub> is above UVLO threshold (with respect to board ground) and the supply voltage to the device has reliably reached above the UVLO condition. For best operation, ensure that V has risen above UVLO before setting the V<sub>EN</sub> pin to high.

### 9.3.1.2.4 V<sub>BB</sub> During Short-to-Ground

When  $V_{OUT}$  is shorted to ground, the module power supply  $(V_{BB})$  can have a transient decrease. This is caused by the sudden increase in current flowing through the wiring harness cables. To achieve ideal system behavior, it is recommended that the module maintain  $V_{BB} > 3$  V (above the maximum  $V_{UVLOF}$ ) during  $V_{OUT}$  short-to-ground. This is typically accomplished by placing bulk capacitance on the power supply node.

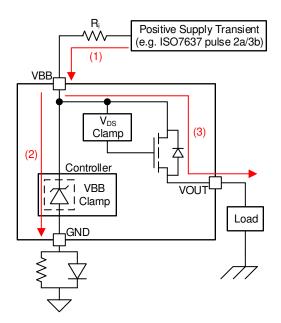

### 9.3.1.3 Voltage Transients

The TPS2HB50-Q1 device describes two types of voltage clamps which protect the FET against system-level voltage transients. The two different clamps are shown in ₹ 5.

The clamp from  $V_{BB}$  to GND is primarily used to protect the controller from positive transients on the supply line (for example, ISO7637-2). The clamp from  $V_{BB}$  to  $V_{OUT}$  is primarily used to limit the voltage across the FET when switching off an inductive load. If the voltage potential from  $V_{BB}$  to GND exceeds the  $V_{BB}$  clamp level, the clamp will allow current to flow through the device from  $V_{BB}$  to GND (Path 2). If the voltage potential from  $V_{BB}$  to  $V_{OUT}$  exceeds the clamping voltage, the power FET will allow current to flow from  $V_{BB}$  to  $V_{OUT}$  (Path 3). Additional capacitance from  $V_{BB}$  to GND can increase the reliability of the system during ISO 7637 pulse 2A testing.

图 5. Current Path During Supply Voltage Transient

#### 9.3.1.3.1 Load Dump

The TPS2HB50-Q1 device is tested according to ISO 16750-2:2010(E) suppressed load dump pulse. The device supports up to 40-V load dump transient and will maintain normal operation during the load dump pulse. If the switch is enabled, it will stay enabled and if the switch is disabled, it will stay disabled.

#### 9.3.1.4 Driving Inductive Loads

When switching off an inductive load, the inductor may impose a negative voltage on the output of the switch. The TPS2HB50-Q1 includes a voltage clamp to limit voltage across the FET. The maximum acceptable load inductance is a function of the device robustness.

For more information on driving inductive loads, refer to TI's *How To Drive Inductive, Capacitive, and Lighting Loads with Smart High Side Switches* application report.

#### 9.3.1.5 Reverse Battery

In the reverse battery condition, the switch will automatically be enabled regardless of the state of EN1/EN2 to prevent excess power dissipation inside the MOSFET body diode. In many applications (for example, resistive loads), the full load current may be present during reverse battery. In order to activate the automatic switch on feature, the SEL2 pin must have a path to module ground. This may be path 1 as shown in 8 6, or if the SEL2 pin is unused, the path may be through  $R_{PROT}$  to module ground.

Protection features like thermal shutdown are not available during a reverse battery event. Care must be taken to ensure that excessive power is not dissipated in the switch during the reverse battery condition.

There are two options for blocking reverse current in the system. The first option is to place a blocking device (FET or diode) in series with the battery supply, blocking all current paths. The second option is to place a blocking diode in series with the GND node of the high-side switch. This method will protect the controller portion of the switch (path 2), but it will not prevent current from flowing through the load (path 3). The diode used for the second option may be shared amongst multiple high-side switches.

Path 1 shown in \begin{array}{c} \begin{array}{c} 6 \end{array} is blocked inside of the device.

图 6. Current Path During Reverse Battery

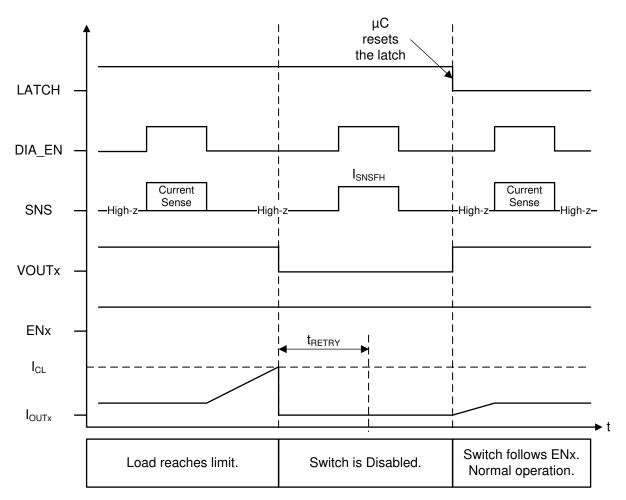

### 9.3.1.6 Fault Event – Timing Diagrams

注

All timing diagrams assume that the SELx pins are set to select the relevant channel.

The LATCH, DIA\_EN, and ENx pins are controlled by the user. The timing diagrams represent a possible use-case.

₹ 7 shows the immediate current limit switch off and the retry behavior of versions A and B of the device. As shown, the switch will remain latched off until the LATCH pin is low.

图 7. Current Limit - Version A and B - Latched Behavior

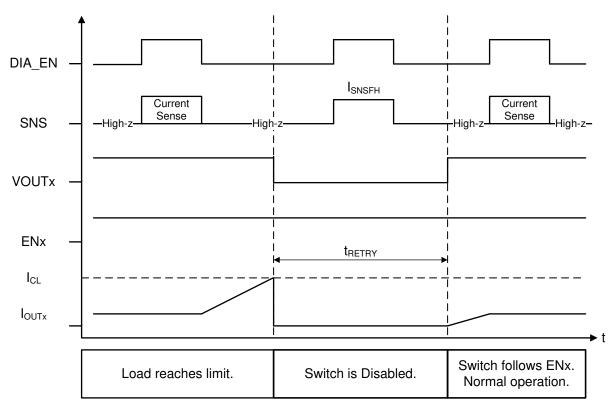

8 shows the immediate current limit switch off behavior of versions A and B. In this example, LATCH is tied to GND; hence, the switch will retry after the fault is cleared and t<sub>RETRY</sub> has expired.

图 8. Current Limit – Version A and B - LATCH = 0

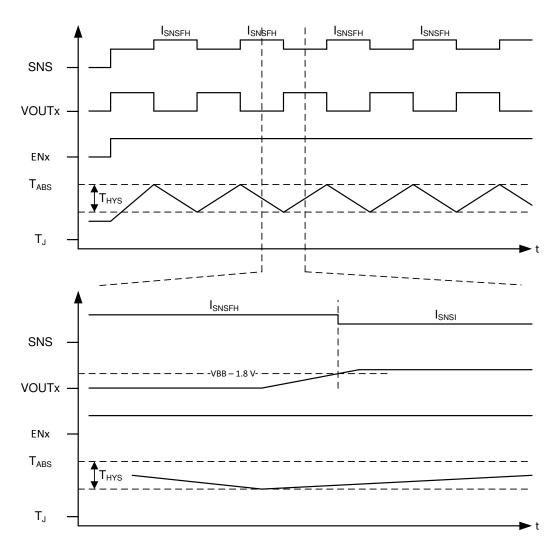

$\ensuremath{\mathbb{E}}$  9 illustrates auto-retry behavior and provides a zoomed-in view of the fault indication during retry. When the switch retries after a shutdown event, the SNS fault indication will remain at the fault state until  $V_{OUT}$  has risen to  $V_{BB} - 1.8 \ V$ . Once  $V_{OUT}$  has risen, the SNS fault indication is reset and current sensing is available. If there is a short-to-ground and  $V_{OUT}$  cannot rise, the SNS fault indication will remain indefinitely.

注

89 9 assumes that  $t_{RETRY}$  has expired by the time that  $T_J$  reaches the hysteresis threshold.

LATCH = 0 V and DIA\_EN = 5 V

图 9. Fault Indication During Retry

### 9.3.2 Diagnostic Mechanisms

### 9.3.2.1 VOUTx Short-to-Battery and Open-Load

The TPS2HB50-Q1 is capable of detecting short-to-battery and open-load events regardless of whether the switch is turned on or off, however the two conditions use different methods.

#### 9.3.2.1.1 Detection With Switch Enabled

When the switch is enabled, the VOUTx short-to-battery and open-load conditions can be detected by the current sense feature. In both cases, the load current will be measured through the SNS pin as below the expected value.

#### 9.3.2.1.2 Detection With Switch Disabled

While the switch is disabled, if DIA\_EN is high, an internal comparator will detect the condition of  $V_{OUT}$ . If the load is disconnected (open load condition) or there is a short to battery the  $V_{OUT}$  voltage will be higher than the open load threshold ( $V_{OL,off}$ ) and a fault is indicated on the SNS pin . An internal pull-up of 1 M $\Omega$  is in series with an internal MOSFET switch, so no external component is required if only a completely open load must be detected. However, if there is significant leakage or other current draw even when the load is disconnected, a lower value pull-up resistor and switch can be added externally to set the  $V_{OUT}$  voltage above the  $V_{OL,off}$  during open load conditions.

(1) This figure assumes that the device ground and the load ground are at the same potential. In a real system, there may be a ground shift voltage of 1 V to 2 V.

#### 图 10. Short to Battery and Open Load Detection

The detection circuitry is only enabled when DIA\_EN = HIGH and EN = LOW. If  $V_{OUT} > V_{OL}$ , the SNS pin will go to the fault level, but if  $V_{OUT} < V_{OL}$  there will be no fault indication. The fault indication will only occur if the SEL1 pin is set to diagnose the respective channel.

While the switch is disabled and DIA\_EN is high, the fault indication mechanisms will continuously represent the present status. For example, if  $V_{OUT}$  decreases from greater than  $V_{OL}$  to less than  $V_{OL}$ , the fault indication is reset. Additionally, the fault indication is reset upon the falling edge of DIA\_EN or the rising edge of EN.

图 11. Open Load

#### 9.3.2.2 SNS Output

The SNS output may be used to sense the load current or device temperature. The SELx pins will select the desired sense signal. The sense circuit will provide a current that is proportional to the selected parameter. This current will be sourced into an external resistor to create a voltage that is proportional to the selected parameter. This voltage may be measured by an ADC or comparator.

To ensure accurate sensing measurement, the sensing resistor should be connected to the same ground potential as the  $\mu C$  ADC.

表 3. Analog Sense Transfer Function

| PARAMETER          | TRANSFER FUNCTION                                             |

|--------------------|---------------------------------------------------------------|

| Load current       | $I_{SNSI} = I_{OUT} / K_{SNS} (1500)$                         |

| Device temperature | $I_{SNST} = (T_J - 25^{\circ}C) \times dI_{SNST} / dT + 0.85$ |

The SNS output will also be used to indicate system faults.  $I_{SNS}$  will go to the predefined level,  $I_{SNSFH}$ , when there is a fault.  $I_{SNSFH}$ ,  $dI_{SNST}/dT$ , and  $K_{SNS}$  are defined in the *Specifications* section.

#### 9.3.2.2.1 R<sub>SNS</sub> Value

The following factors should be considered when selecting the R<sub>SNS</sub> value:

Current sense ratio (K<sub>SNS</sub>)

- Largest and smallest diagnosable load current required for application operation

- Full-scale voltage of the ADC

- Resolution of the ADC

For an example of selecting  $R_{SNS}$  value, reference Selecting the  $R_{SNS}$  Value in the applications section of this datasheet.

#### 9.3.2.2.1.1 High Accuracy Load Current Sense

In many automotive modules, it is required that the high-side switch provide diagnostic information about the downstream load. With more complex loads, high accuracy sensing is required. A few examples follow:

- **LED lighting**: In many architectures, the body control module (BCM) must be compatible with both incandescent bulbs and also LED modules. The bulb may be relatively simple to diagnose. However, the LED module will consume less current and also can include multiple LED strings in parallel. The same BCM is used in both cases, so the high-side switch can accurately diagnose both load types.

- **Solenoid protection**: Often solenoids are precisely controlled by low-side switches. However, in a fault event, the low-side switch cannot disconnect the solenoid from the power supply. A high-side switch can be used to continuously monitor several solenoids. If the system current becomes higher than expected, the high-side switch can disable the module.

#### 9.3.2.2.1.2 SNS Output Filter

To achieve the most accurate current sense value, it is recommended to filter the SNS output. There are two methods of filtering:

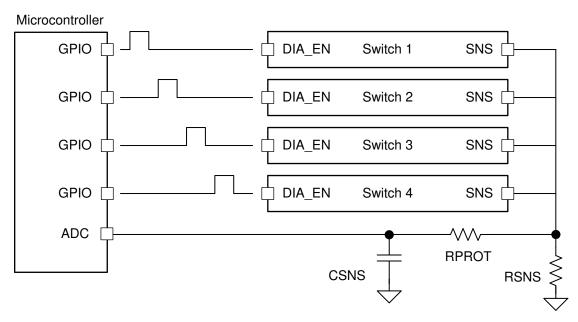

- Low-Pass RC filter between the SNS pin and the ADC input. This filter is illustrated in <a> 15</a> with typical values for the resistor and capacitor. The designer should select a C<sub>SNS</sub> capacitor value based on system requirements. A larger value will provide improved filtering but a smaller value will allow for faster transient response.

- The ADC and microcontroller can also be used for filtering. It is recommended that the ADC collects several

measurements of the SNS output. The median value of this data set should be considered as the most

accurate result. By performing this median calculation, the microcontroller can filter out any noise or outlier

data.

#### 9.3.2.3 Fault Indication and SNS Mux

The following faults will be communicated through the SNS output:

- · Switch shutdown, due to:

- Thermal Shutdown

- Current limit

- Open-Load / V<sub>OUT</sub> shorted-to-battery

Open-load / Short-to-battery are not indicated while the switch is enabled, although these conditions can still be detected through the sense current. Hence, if there is a fault indication corresponding to an enabled channel, then it must be either due to an over-current or over-temperature event.

The SNS pin will only indicate the fault if the SELx pins are selecting the relevant channel. When the device is set to measure temperature, the pin will be measuring the temperature of whichever channel is at a higher temperature.

表 4. Version A/B SNS Mux

|        | OUTPUTS |      |                             |                    |

|--------|---------|------|-----------------------------|--------------------|

| DIA_EN | SEL1    | SEL2 | FAULT DETECT <sup>(1)</sup> | SNS                |

| 0      | X       | X    | X                           | High-Z             |

| 1      | 0       | 0    | 0                           | CH1 current        |

| 1      | 0       | 1    | 0                           | CH2 current        |

| 1      | 1       | 0    | 0                           | Device temperature |

- (1) Fault Detect encompasses multiple conditions:

- (a) Switch shutdown and waiting for retry

- (b) Open Load / Short To Battery

#### 表 4. Version A/B SNS Mux (接下页)

|        | OUTPUTS |      |                             |                    |

|--------|---------|------|-----------------------------|--------------------|

| DIA_EN | SEL1    | SEL2 | FAULT DETECT <sup>(1)</sup> | SNS                |

| 1      | 1       | 1    | 0                           | N/A                |

| 1      | 0       | 0    | 1                           | I <sub>SNSFH</sub> |

| 1      | 0       | 1    | 1                           | I <sub>SNSFH</sub> |

| 1      | 1       | 0    | 1                           | Device temperature |

| 1      | 1       | 1    | 1                           | N/A                |

#### 9.3.2.4 Resistor Sharing

Multiple high-side channels may use the same SNS resistor as shown in the figure below. This reduces the total number of passive components in the system and the number of ADC terminals that are required of the microcontroller.

图 12. Sharing R<sub>SNS</sub> Among Multiple Devices

### 9.3.2.5 High-Frequency, Low Duty-Cycle Current Sensing

Some applications will operate with a high-frequency, low duty-cycle PWM or require fast settling of the SNS output. For example, a 250 Hz, 5% duty cycle PWM will have an on-time of only 200 µs that must be accommodated. The micro-controller ADC may sample the SNS signal after the defined settling time t<sub>SNSION3</sub>.

**NSTRUMENTS**

图 13. Current Sensing in Low-Duty Cycle Applications

#### 9.4 Device Functional Modes

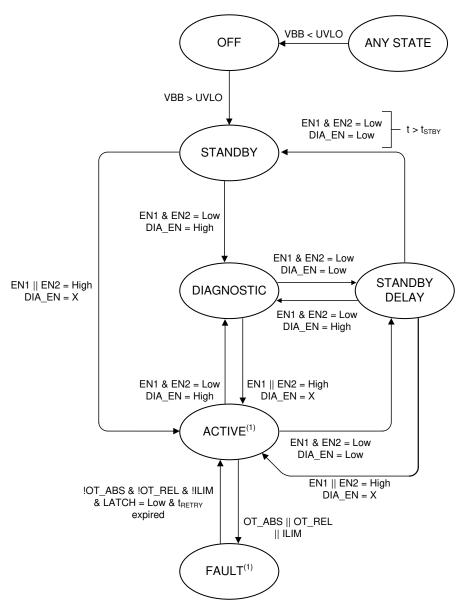

During typical operation, the TPS2HB50-Q1 can operate in a number of states that are described below and shown as a state diagram in ₹ 14.

#### 9.4.1 Off

Off state occurs when the device is not powered.

#### 9.4.2 Standby

Standby state is a low-power mode used to reduce power consumption to the lowest level. Diagnostic capabilities are not available in Standby mode.

### 9.4.3 Diagnostic

Diagnostic state may be used to perform diagnostics while the switches are disabled.

### 9.4.4 Standby Delay

The Standby Delay state is entered when EN1, EN2, and DIA\_EN are low. After t<sub>STBY</sub>, if the ENx and DIA\_EN pins are still low, the device will go to Standby State.

#### 9.4.5 Active

In Active state, one or more of the switches are enabled. The diagnostic functions may be turned on or off during Active state.

#### 9.4.6 Fault

The Fault state is entered if a fault shutdown occurs (thermal shutdown or current limit). After all faults are cleared, the LATCH pin is low, and the retry timer has expired, the device will transition out of Fault state. If the relevant ENx pin is high, the switch will re-enable. If the relevant ENx pin is low, the switch will remain off.

# Device Functional Modes (接下页)

(1) CH1 and CH2 operate independently. Each channel is enabled/disabled independently. Also, if there is a fault on one channel, the other channel is not affected.

图 14. State Diagram

# 10 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 10.1 Application Information

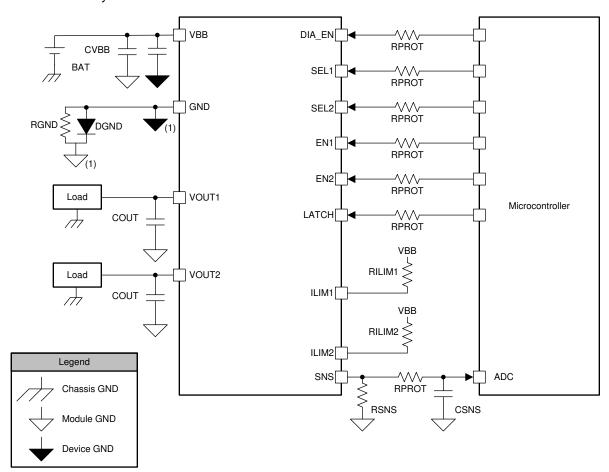

₹ 15 shows the schematic of a typical application for the TPS2HB50-Q1. It includes all standard external components. This section of the datasheet discusses the considerations in implementing commonly required application functionality.

(1) With the ground protection network, the device ground will be offset relative to the microcontroller ground.

图 15. System Diagram

### 表 5. Recommended External Components

| COMPONENT         | TYPICAL VALUE  | PURPOSE                                                   |

|-------------------|----------------|-----------------------------------------------------------|

| R <sub>PROT</sub> | 15 kΩ          | Protect microcontroller and device I/O pins               |

| R <sub>SNS</sub>  | 1 kΩ           | Translate the sense current into sense voltage            |

| C <sub>SNS</sub>  | 100 pF - 10 nF | Low-pass filter for the ADC input                         |

| $R_{GND}$         | 4.7 kΩ         | Stabilize GND potential during turn-off of inductive load |

| D <sub>GND</sub>  | BAS21 Diode    | Protects device during reverse battery                    |

### Application Information (接下页)

### 表 5. Recommended External Components (接下页)

| COMPONENT         | TYPICAL VALUE                         | PURPOSE                                                                              |

|-------------------|---------------------------------------|--------------------------------------------------------------------------------------|

| R <sub>ILIM</sub> | 5 kΩ - 25 kΩ                          | Set current limit threshold                                                          |

| C <sub>VBB</sub>  | 220 nF to Device GND                  | Filtering of voltage transients (for example, ESD, ISO7637-2) and improved emissions |

|                   | 100 nF to Module GND                  | Stabilize the input supply and filter out low frequency noise.                       |

| C <sub>OUT</sub>  | 22 nF                                 | Filtering of voltage transients (for example, ESD, ISO7637-2)                        |

| $C_GND$           | 1 μF from Device GND to<br>Module GND | Optional capacitance to help with RF immunity.                                       |

#### 10.1.1 Ground Protection Network

As discussed in the *Reverse Battery* section,  $D_{GND}$  may be used to prevent excessive reverse current from flowing into the device during a reverse battery event. Additionally,  $R_{GND}$  is placed in parallel with  $D_{GND}$  if the switch is used to drive an inductive load. The ground protection network ( $D_{GND}$  and  $R_{GND}$ ) may be shared amongst multiple high-side switches.

A minimum value for  $R_{GND}$  may be calculated by using the absolute maximum rating for  $I_{GND}$ . During the reverse battery condition,  $I_{GND} = V_{BB} / R_{GND}$ :

$R_{GND} \ge V_{BB} / I_{GND}$

- Set  $V_{BB} = -13.5 \text{ V}$

- Set  $I_{GND} = -50$  mA (absolute maximum rating)

$$R_{GND} \ge -13.5 \text{ V} / -50 \text{ mA} = 270 \Omega$$

(2)

In this example, it is found that  $R_{GND}$  must be at least 270  $\Omega$ . It is also necessary to consider the power dissipation in  $R_{GND}$  during the reverse battery event:

$$P_{RGND} = V_{BB}^2 / R_{GND}$$

(3)

$P_{RGND} = (13.5 \text{ V})^2 / 270 \Omega = 0.675 \text{ W}$

In practice, R<sub>GND</sub> may not be rated for such a high power. In this case, a larger resistor value should be selected.

#### 10.1.2 Interface With Microcontroller

The ground protection network will cause the device ground to be at a higher potential than the module ground (and microcontroller ground). This offset will impact the interface between the device and the microcontroller.

Logic pin voltage will be offset by the forward voltage of the diode. For input pins (for example, EN1), the designer must consider the  $V_{IH}$  specification of the switch and the  $V_{OH}$  specification of the microcontroller. For a system that *does not* include  $D_{GND}$ , it is required that  $V_{OH} > V_{IH}$ . For a system that *does* include  $D_{GND}$ , it is required that  $V_{OH} > (V_{IH} + V_F)$ .  $V_F$  is the forward voltage of  $D_{GND}$ .

The sense resistor, R<sub>SNS</sub>, should be terminated to the microcontroller ground. In this case, the ADC can accurately measure the SNS signal even if there is an offset between the microcontroller ground and the device ground.

#### 10.1.3 I/O Protection