# 超低功率、轨到轨输出、完全差分放大器

查询样品: THS4531

#### 特性

- 超低功耗

- 电压: 2.5V 至 5.5V

- 电流: 250μA

- 断电模式 0.5µA (典型值)

- 完全差分架构

- 带宽: 36MHz

- 转换速率: 200V/µs

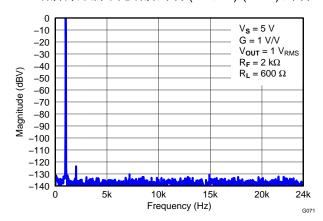

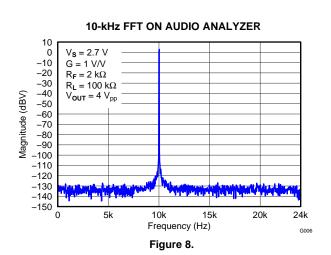

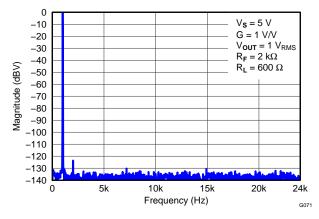

- 总谐波失真: 1kHz (1V<sub>RMS</sub>, R<sub>L</sub> = 2kΩ) 时为-120dBc

- 输入电压噪声: 10nV/√Hz (f=1 kHz)

- 高 DC 精度

- $V_{os}$  偏移 =  $\pm 4\mu V/^{\circ}C$  (-40°C 至 +125°C)

- A<sub>OI</sub>: 114 dB

- RRO 轨至轨输出

- NRI 负电源轨输入

- 输出共模控制

#### 应用范围

- 低功耗逐次逼近式 (SAR)、三角积分模数转换器 (ΔΣ ADC) 驱动器

- 低功耗、高性能

- 差分到差分放大器

- 单端至差分放大器

- 低功耗、宽带宽差分驱动器

- 低功耗、宽带宽差分信号调节

- 高通道数量和功率密集系统

#### 说明

THS4531 是一款低功耗、完全差分运算放大器,此放大器具有低于负电源轨和轨到轨输出的输入共模范围。此器件设计用于能耗和功率耗散都十分关键的低功率数据采集系统和高密度应用。

此器件特有精确输出共模控制,此控制可实现驱动 ADC 时的 dc 耦合。 与低于负电源轨和轨到轨输出的输入共模范围相耦合可轻松实现来自单端接地基准信号源的接口与 SAR 的连接,并允许 ΔΣ ADC 只使用 2.5V 至 5V 的单一电源。 它也是一个针对通用低功耗差分信号调节应用的有用的工具。

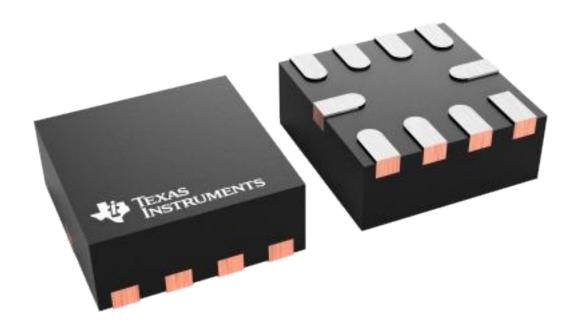

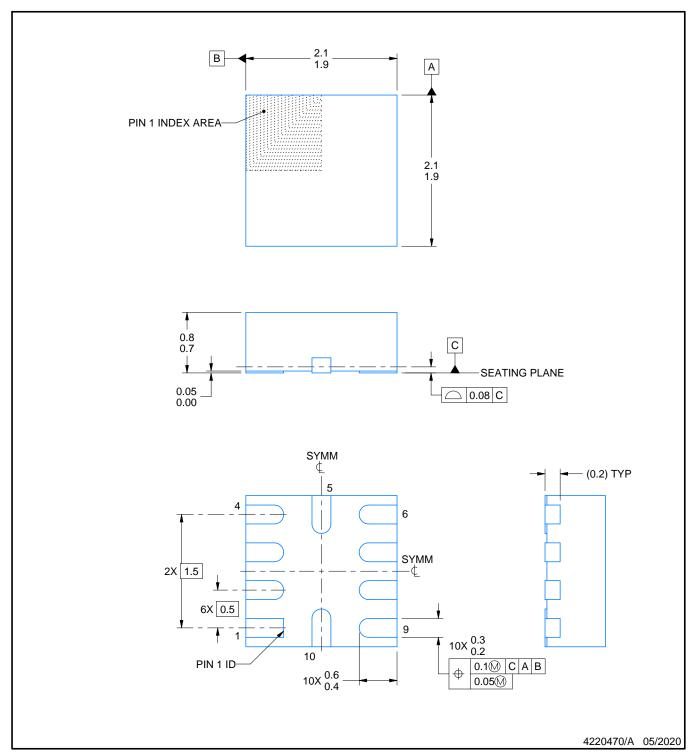

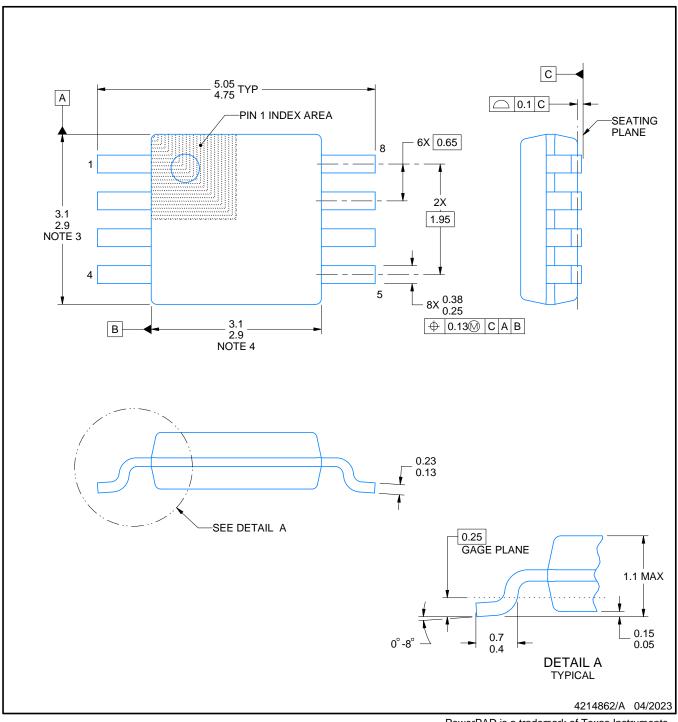

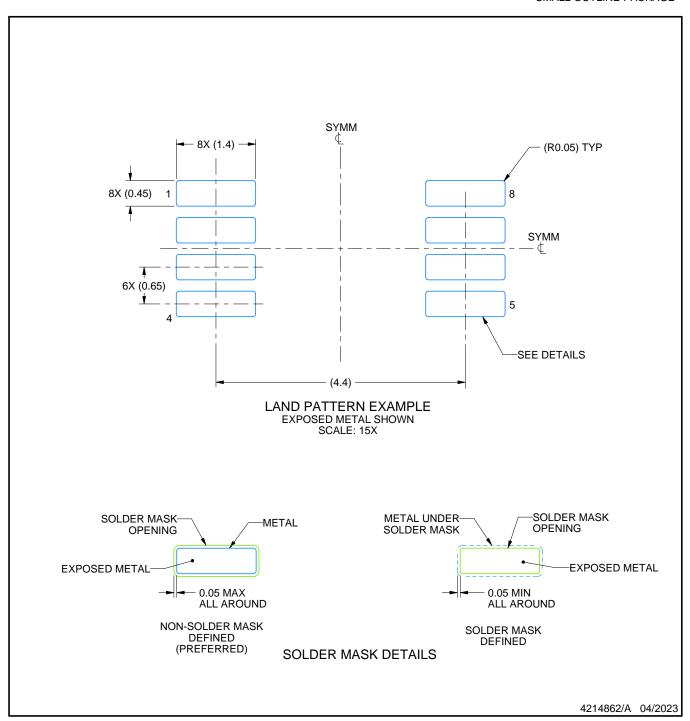

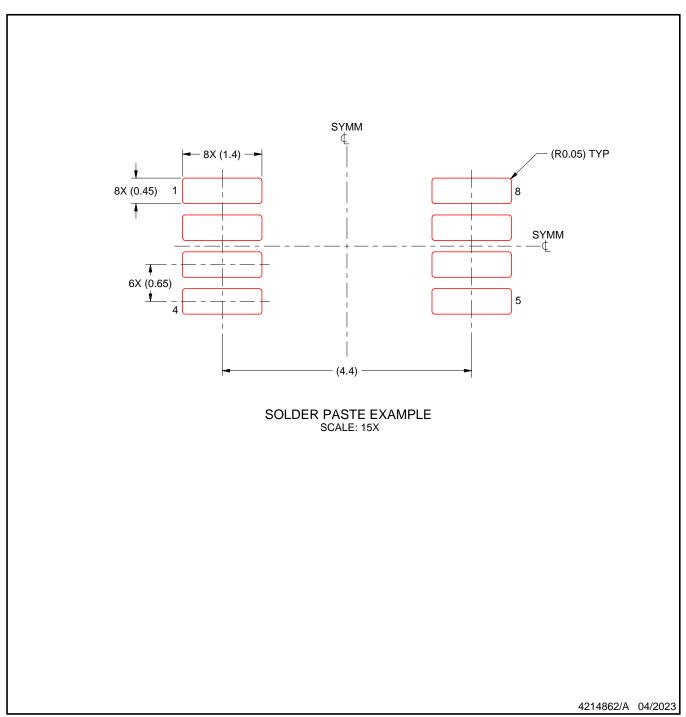

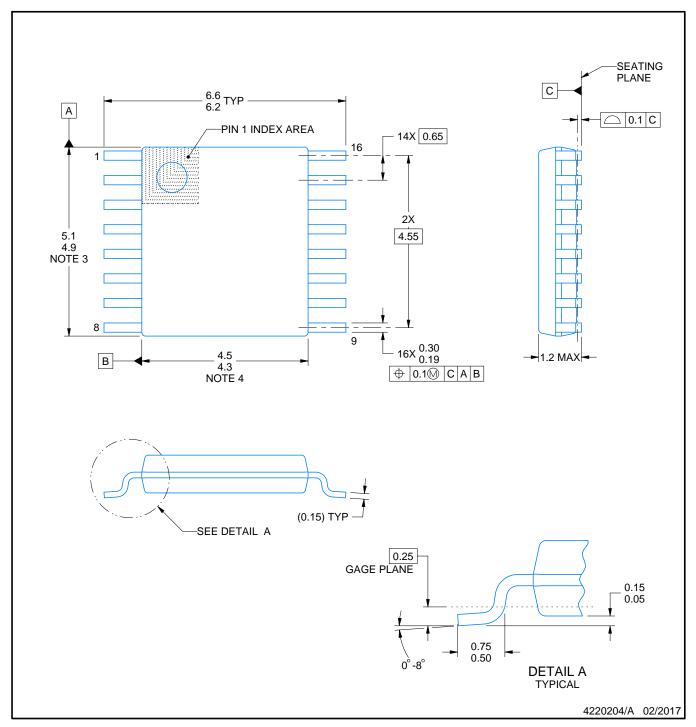

THS4531 可在介于 -40℃ 至 +125℃ 的扩展温度范围 内运行。 可提供下列封装选项:

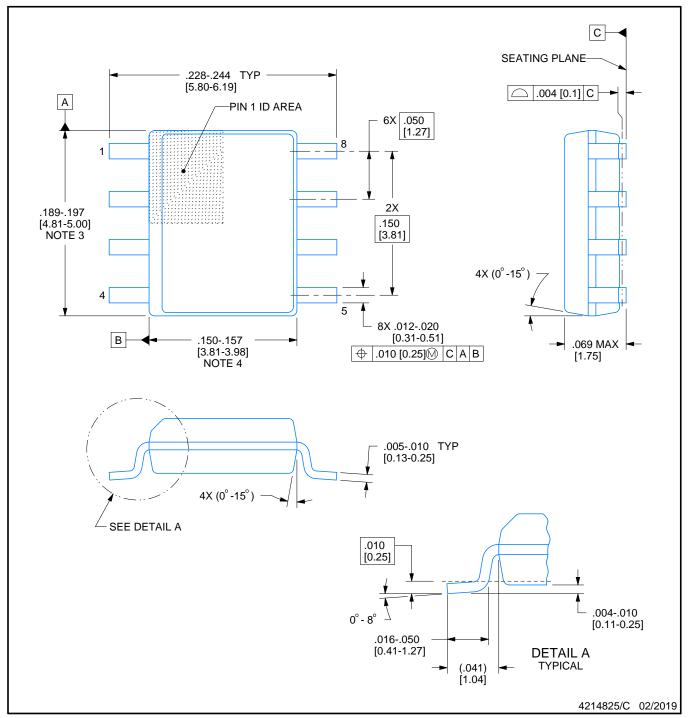

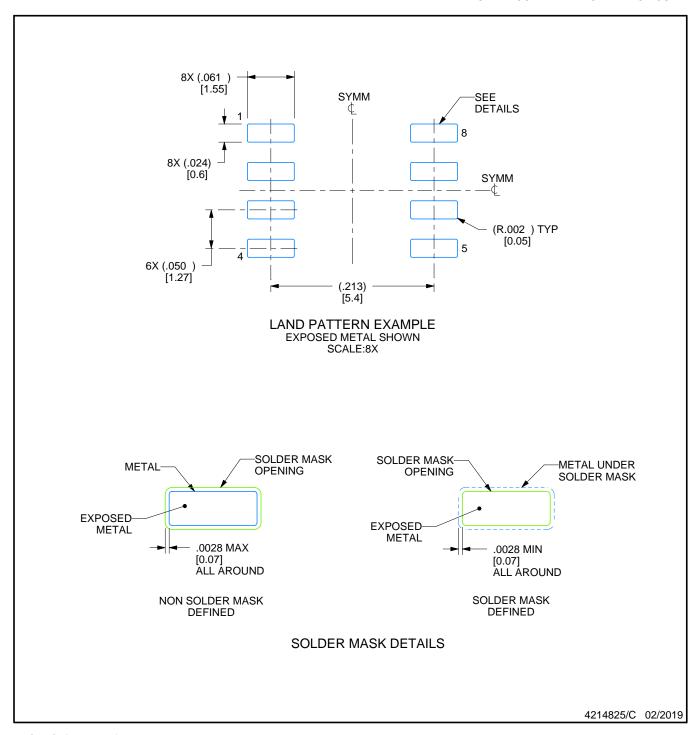

- 8 引脚小尺寸集成电路 (SOIC) / 超小型小尺寸封装 (VSSOP) (微型小尺寸封装 (MSOP)) (D/DGK)

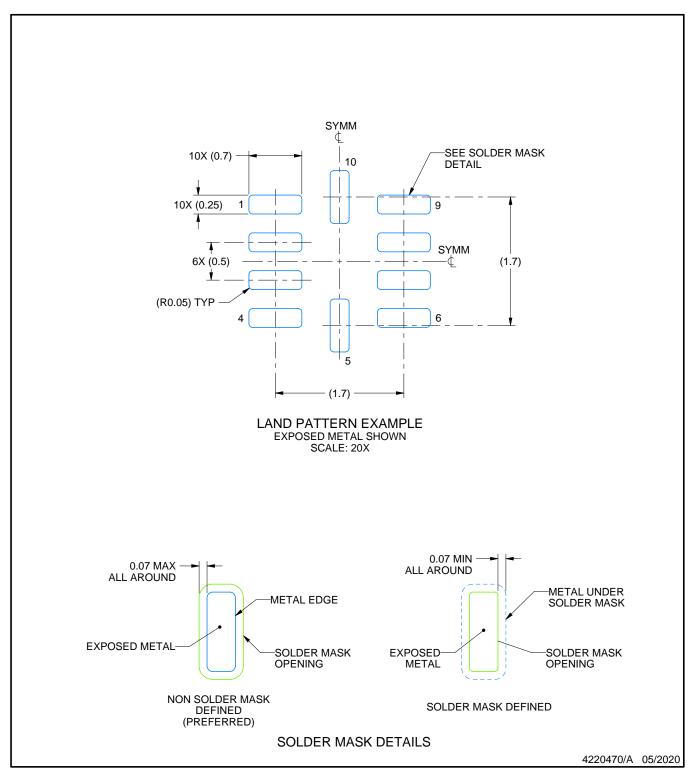

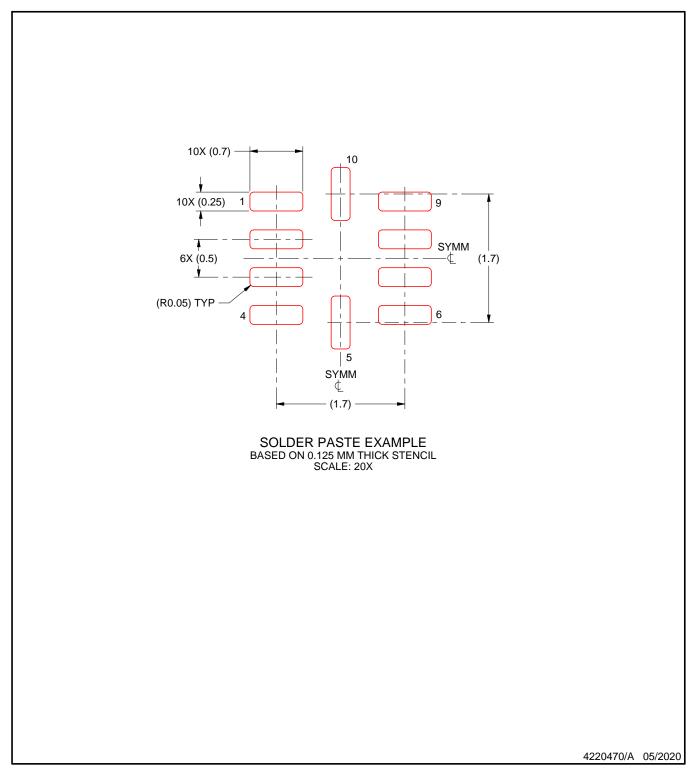

- 10 引脚方形扁平无引脚封装 (WQFN) (RUN) 封装

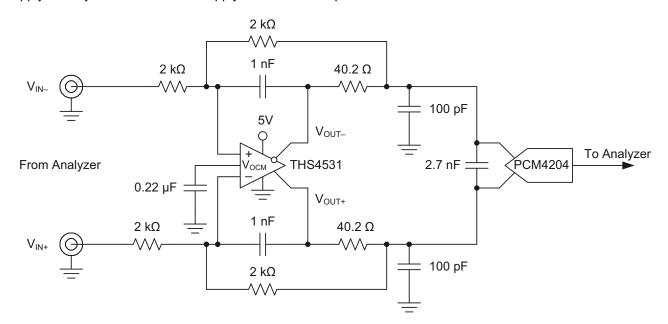

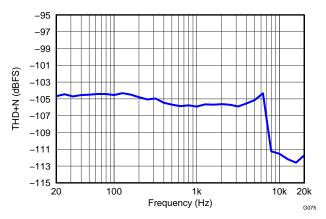

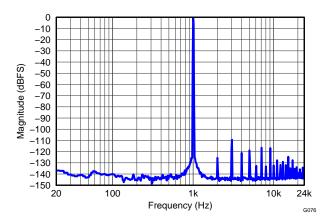

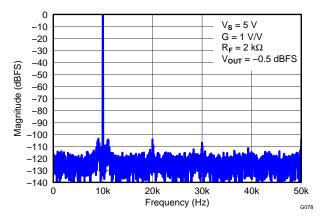

图 1. 音频分析仪上的1kHz 快速傅里叶变换(FFT) 幅 值频率

表 1. 相关产品

| 器件      | 带宽 (BW) (MHz) | I <sub>Q</sub> (mA) | 100kHz 下的总谐波<br>失真 (dBc) | V <sub>N</sub> (nV/√ <del>Hz</del> ) | 轨到轨   |

|---------|---------------|---------------------|--------------------------|--------------------------------------|-------|

| THS4521 | 145           | 1.14                | -120                     | 4.6                                  | 输出    |

| THS4520 | 570           | 15.3                | -114                     | 2                                    | 输出    |

| THS4121 | 100           | 16                  | <b>–</b> 79              | 5.4                                  | 输入/输出 |

| THS4131 | 150           | 16                  | -107                     | 1.3                                  | 否     |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

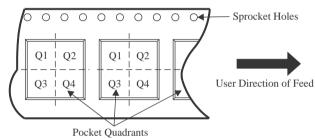

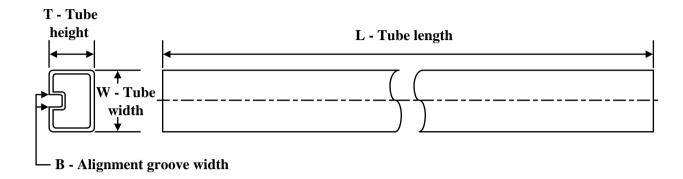

## PACKAGING/ORDERING INFORMATION(1)

| PRODUCT | CHANNEL<br>COUNT | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING  | ORDERING<br>NUMBER | TRANSPORT MEDIA,<br>QUANTITY |                     |

|---------|------------------|------------------|-----------------------|-----------------------------------|---------------------|--------------------|------------------------------|---------------------|

|         | 1                | SOIC-8           | D                     | -40°C to +125°C                   | T4531               | THS4531ID          | Rails, 75                    |                     |

|         | 1                | SOIC-8           | D                     | D -40 C to +125 C                 | T4531               | THS4531IDR         | Tape and reel, 2500          |                     |

| TUC4504 | 1                | V000D 0          | DOK                   | 4000 +- +40500                    | 4531                | THS4531IDGK        | Rails, 80                    |                     |

| THS4531 | 1                | VSSOP-8          | DGK                   | DGK                               | DGK -40°C to +125°C |                    | THS4531IDGKR                 | Tape and reel, 2500 |

|         | 1                | WOEN 10          | DUN                   | 40°C to 140E°C                    | 4531                | THS4531IRUNT       | Tape and reel, 250           |                     |

|         | 1                | WQFN-10          | RUN                   | –40°C to +125°C                   | 4531                | THS4531IRUNR       | Tape and reel, 3000          |                     |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

|                                          |                                                                     | VALUE                                | UNITS |

|------------------------------------------|---------------------------------------------------------------------|--------------------------------------|-------|

| Supply voltage, V <sub>S</sub>           | _ to V <sub>S+</sub>                                                | 5.5                                  |       |

| Input/output voltag                      | e, V <sub>IN±</sub> , V <sub>OUT±</sub> , and V <sub>OCM</sub> pins | $(V_{S-}) - 0.7$ to $(V_{S+}) + 0.7$ | V     |

| Differential input vo                    | oltage, V <sub>ID</sub>                                             | 1                                    | ٧     |

| Continuous output                        | current, I <sub>O</sub>                                             | 50                                   | mA    |

| Continuous input current, I <sub>i</sub> |                                                                     | 0.75                                 | mA    |

| Continuous power dissipation             |                                                                     | See Thermal Information              |       |

| Maximum junction                         | temperature, T <sub>J</sub>                                         | 150                                  | °C    |

| Operating free-air                       | temperature range, T <sub>A</sub>                                   | -40 to +125                          | °C    |

| Storage temperatu                        | re range, T <sub>stg</sub>                                          | -65 to +150                          | °C    |

| Electrostatic                            | Human body model (HBM)                                              | 3000                                 | V     |

| discharge (ESD)                          | Charge device model (CDM)                                           | 500                                  | V     |

| ratings:                                 | Machine model (MM)                                                  | 200                                  | V     |

#### THERMAL INFORMATION

|                               |                                              | THS4531     | THS4531                  | THS4531       |       |

|-------------------------------|----------------------------------------------|-------------|--------------------------|---------------|-------|

| THERMAL METRIC <sup>(1)</sup> |                                              | SOIC<br>(P) | VSSOP<br>(MSOP)<br>(DGK) | WQFN<br>(RUN) | UNITS |

|                               |                                              | 8 PINS      | 8 PINS                   | 10 PINS       |       |

| $\theta_{JA}$                 | Junction-to-ambient thermal resistance       | 133         | 198                      | 163           |       |

| $\theta_{JCtop}$              | Junction-to-case (top) thermal resistance    | 78          | 84                       | 66            |       |

| $\theta_{JB}$                 | Junction-to-board thermal resistance         | 73          | 120                      | 113           | °C/W  |

| ΨЈТ                           | Junction-to-top characterization parameter   | 26          | 19                       | 17            | *C/VV |

| ΨЈВ                           | Junction-to-board characterization parameter | 73          | 118                      | 113           |       |

| $\theta_{JCbot}$              | Junction-to-case (bottom) thermal resistance | N/A         | N/A                      | N/A           |       |

(1) 有关传统和新的热度量的更多信息,请参阅 IC 封装热度量 应用报告 SPRA953。

# **ELECTRICAL CHARACTERISTICS:** V<sub>S</sub> = 2.7 V

Test conditions at  $T_A = 25^{\circ}C$ ,  $V_{S+} = 2.7$  V,  $V_{S-} = 0$  V,  $V_{OCM} = open$ ,  $V_{OUT} = 2$   $V_{PP}$ ,  $R_F = 2$   $k\Omega$ ,  $R_L = 2$   $k\Omega$  differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                            | CONDITIONS                                       | MIN TYP | MAX | UNITS              | TEST<br>LEVEL <sup>(1)</sup> |  |

|--------------------------------------|--------------------------------------------------|---------|-----|--------------------|------------------------------|--|

| AC PERFORMANCE                       |                                                  |         | 1   |                    | I.                           |  |

|                                      | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 1  | 34      |     |                    |                              |  |

| Concil pianol bandwidth              | $V_{OUT} = 100 \text{ mV}_{PP}, G = 2$           | 16      |     | NAL I-             |                              |  |

| Small-signal bandwidth               | $V_{OUT} = 100 \text{ mV}_{PP}, G = 5$           | 6       |     | MHz                |                              |  |

|                                      | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10 | 2.7     |     |                    |                              |  |

| Gain-bandwidth product               | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10 | 27      |     | MHz                |                              |  |

| Large-signal bandwidth               | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1     | 34      |     | MHz                |                              |  |

| Bandwidth for 0.1-dB flatness        | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1     | 12      |     | MHz                |                              |  |

| Slew rate, rise/fall, 25% to 75%     |                                                  | 190/320 |     | V/µs               |                              |  |

| Rise/fall time, 10% to 90%           |                                                  | 5.2/6.1 |     | ns                 |                              |  |

| Settling time to 1%, rise/fall       | V OV star                                        | 25/20   |     |                    |                              |  |

| Settling time to 0.1%, rise/fall     | V <sub>OUT</sub> = 2-V step                      | 60/60   | ns  | ns                 |                              |  |

| Settling time to 0.01%, rise/fall    |                                                  | 150/110 |     | ns                 |                              |  |

| Overshoot/undershoot, rise/fall      |                                                  | 1/1     |     | %                  |                              |  |

|                                      | f = 1 kHz, V <sub>OUT</sub> = 1 V <sub>RMS</sub> | -122    |     |                    | С                            |  |

| 2nd-order harmonic distortion        | f = 10 kHz                                       | -127    |     | dBc                |                              |  |

|                                      | f = 1 MHz                                        | -59     |     |                    |                              |  |

|                                      | f = 1 kHz, V <sub>OUT</sub> = 1 V <sub>RMS</sub> | -130    |     |                    |                              |  |

| 3rd-order harmonic distortion        | f = 10 kHz                                       | -135    |     | dBc                |                              |  |

|                                      | f = 1 MHz                                        | -70     |     |                    |                              |  |

| 2nd-order intermodulation distortion | f = 1 MHz, 200-Hz tone spacing,                  | -83     |     | dBc                |                              |  |

| 3rd-order intermodulation distortion | V <sub>OUT</sub> envelope = 1 V <sub>PP</sub>    | -81     |     |                    |                              |  |

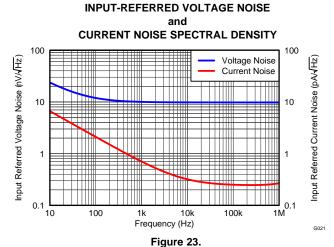

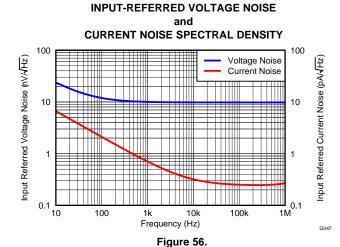

| Input voltage noise                  | f = 1 kHz                                        | 10      |     | nV/√ <del>Hz</del> |                              |  |

| Voltage noise 1/f corner frequency   |                                                  | 45      |     | Hz                 |                              |  |

| Input current noise                  | f = 100 kHz                                      | 0.25    |     | pA/√ <del>Hz</del> |                              |  |

| Current noise 1/f corner frequency   |                                                  | 6.5     |     | kHz                |                              |  |

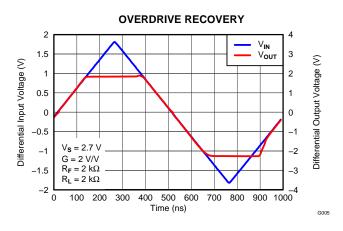

| Overdrive recovery time              | Overdrive = 0.5 V                                | 65      |     | ns                 |                              |  |

| Output balance error                 | V <sub>OUT</sub> = 100 mV, f = 1 MHz             | -65     |     | dB                 |                              |  |

| Closed-loop output impedance         | f = 1 MHz (differential)                         | 2.5     |     | Ω                  |                              |  |

<sup>(1)</sup> Test levels (all values set by characterization and simulation): (A) 100% tested at +25°C; over temperature limits by characterization and simulation. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

Test conditions at  $T_A = 25^{\circ}C$ ,  $V_{S+} = 2.7$  V,  $V_{S-} = 0$  V,  $V_{OCM} = open$ ,  $V_{OUT} = 2$   $V_{PP}$ ,  $R_F = 2$   $k\Omega$ ,  $R_L = 2$   $k\Omega$  differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                 | CONDITIONS                                           | MIN                   | TYP                    | MAX                   | UNITS    | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------------------------------|------------------------------------------------------|-----------------------|------------------------|-----------------------|----------|------------------------------|

| DC PERFORMANCE                            |                                                      |                       |                        |                       |          |                              |

| Open-loop voltage gain (A <sub>OL</sub> ) |                                                      | 100                   | 113                    |                       | dB       | Α                            |

|                                           | T <sub>A</sub> = +25°C                               |                       | ±200                   | ±1000                 |          | Α                            |

| Input referred effect valtage             | $T_A = 0$ °C to +70°C                                |                       |                        | ±1405                 | /        |                              |

| Input-referred offset voltage             | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$  |                       |                        | ±1585                 | μV       | В                            |

|                                           | $T_A = -40$ °C to +125°C                             |                       |                        | ±2000                 |          |                              |

|                                           | $T_A = 0$ °C to +70°C                                |                       | ±1.7                   | ±9                    |          |                              |

| Input offset voltage drift (2)            | $T_A = -40$ °C to +85°C                              |                       | ±1.8                   | ±9                    | μV/°C    | В                            |

|                                           | $T_A = -40$ °C to +125°C                             |                       | ±2                     | ±10                   |          |                              |

|                                           | T <sub>A</sub> = +25°C                               |                       | 160                    | 210                   |          | Α                            |

|                                           | $T_A = 0$ °C to +70°C                                |                       |                        | 221                   |          |                              |

| Input bias current                        | $T_A = -40$ °C to +85°C                              |                       |                        | 222                   | nA       | В                            |

|                                           | $T_A = -40$ °C to +125°C                             |                       |                        | 233                   |          |                              |

|                                           | $T_A = 0$ °C to +70°C                                |                       |                        | 0.25                  |          | В                            |

| Input bias current drift <sup>(2)</sup>   | $T_A = -40$ °C to +85°C                              |                       |                        | 0.25                  | nA/°C    |                              |

|                                           | $T_A = -40$ °C to +125°C                             |                       |                        | 0.25                  |          |                              |

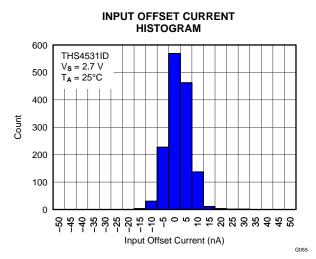

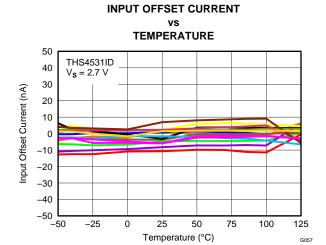

|                                           | T <sub>A</sub> = +25°C                               |                       | ±5                     | ±50                   |          | Α                            |

|                                           | $T_A = 0$ °C to +70°C                                |                       |                        | ±59                   | _        |                              |

| Input offset current                      | $T_A = -40$ °C to +85°C                              |                       |                        | ±60                   | nA       | В                            |

|                                           | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |                       |                        | ±75                   |          |                              |

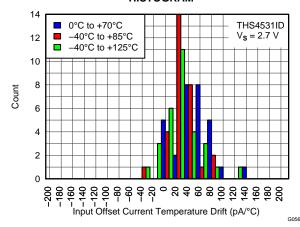

|                                           | $T_A = 0$ °C to +70°C                                |                       | ±0.05                  | ±0.2                  | nA/°C    |                              |

| Input offset current drift <sup>(2)</sup> | $T_A = -40$ °C to +85°C                              |                       | ±0.05                  | ±0.2                  |          | В                            |

|                                           | $T_A = -40$ °C to +125°C                             |                       | ±0.05                  | ±0.2                  |          |                              |

| INPUT                                     |                                                      | I                     |                        |                       |          |                              |

|                                           | T <sub>A</sub> = +25°C, CMRR > 87 dB                 |                       | V <sub>S-</sub> - 0.2  | V <sub>S-</sub>       |          | Α                            |

| Common-mode input low                     | $T_A = -40$ °C to +125°C, CMRR > 87 dB               |                       | V <sub>S-</sub> - 0.2  | V <sub>S-</sub>       | V        | В                            |

|                                           | T <sub>A</sub> = +25°C, CMRR > 87 dB                 | V <sub>S+</sub> – 1.2 | V <sub>S+</sub> – 1.1  |                       |          | Α                            |

| Common-mode input high                    | $T_A = -40$ °C to +125°C, CMRR > 87 dB               | V <sub>S+</sub> – 1.2 | V <sub>S+</sub> – 1.1  |                       | V        | В                            |

| Common-mode rejection ratio               |                                                      | 90                    | 116                    |                       | dB       | Α                            |

| Input impedance common-mode               |                                                      |                       | 200    1.2             |                       |          | С                            |

| Input impedance differential mode         |                                                      |                       | 200    1               |                       | kΩ    pF | С                            |

| OUTPUT                                    |                                                      |                       |                        |                       |          |                              |

| Single-ended output voltage: low          | T <sub>A</sub> = +25°C                               |                       | V <sub>S-</sub> + 0.06 | V <sub>S-</sub> + 0.2 | .,       | А                            |

|                                           | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |                       | V <sub>S-</sub> + 0.06 | V <sub>S-</sub> + 0.2 | V        | В                            |

| 0. 1 1 1                                  | T <sub>A</sub> = +25°C                               | V <sub>S+</sub> - 0.2 | V <sub>S+</sub> - 0.11 |                       |          | Α                            |

| Single-ended output voltage: high         | $T_A = -40$ °C to +125°C                             | V <sub>S+</sub> - 0.2 | V <sub>S+</sub> - 0.11 |                       | V        | В                            |

| Output saturation voltage: high/low       |                                                      |                       | 110/60                 |                       | mV       | С                            |

|                                           | T <sub>A</sub> = +25°C                               | ±15                   | ±22                    |                       | _        | Α                            |

| Linear output current drive               | $T_A = -40$ °C to +125°C                             | ±15                   |                        |                       | mA       | В                            |

<sup>(2)</sup> Input offset voltage drift, input bias current drift, and input offset current drift are average values calculated by taking data at the end points, computing the difference, and dividing by the temperature range.

Test conditions at  $T_A = 25^{\circ}C$ ,  $V_{S+} = 2.7$  V,  $V_{S-} = 0$  V,  $V_{OCM} = open$ ,  $V_{OUT} = 2$   $V_{PP}$ ,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                                          | CONDITIONS                                                                                 | MIN  | TYP         | MAX  | UNITS    | TEST<br>LEVEL <sup>(1)</sup> |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|-------------|------|----------|------------------------------|

| POWER SUPPLY                                                       |                                                                                            |      |             |      |          |                              |

| Specified operating voltage                                        |                                                                                            | 2.5  |             | 5.5  | V        | В                            |

| Quiescent operating current/ch                                     | $T_A = +25$ °C, $\overline{PD} = V_{S+}$                                                   |      | 230         | 330  |          | Α                            |

| Quiescent operating current/cn                                     | $T_A = -40$ °C to +125°C, $\overline{PD} = V_{S+}$                                         |      | 270         | 370  | μA       | В                            |

| Power-supply rejection (±PSRR)                                     |                                                                                            | 87   | 108         |      | dB       | Α                            |

| POWER DOWN                                                         |                                                                                            |      |             |      |          |                              |

| Enable voltage threshold                                           | Specified on above 2.1 V                                                                   |      |             | 2.1  | V        | Α                            |

| Disable voltage threshold                                          | Specified off below 0.7 V                                                                  | 0.7  |             |      |          | Α                            |

| Disable pin bias current                                           | PD = V <sub>S-</sub> + 0.5 V                                                               |      | 50          | 500  | nA       | Α                            |

| Power-down quiescent current                                       | PD = V <sub>S-</sub> + 0.5 V                                                               |      | 0.5         | 2    | μA       | Α                            |

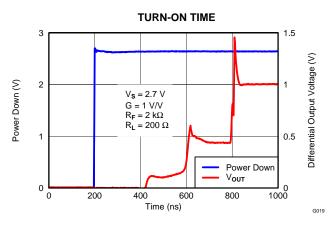

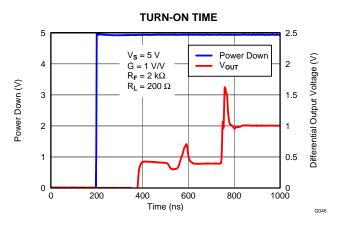

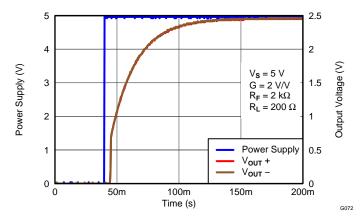

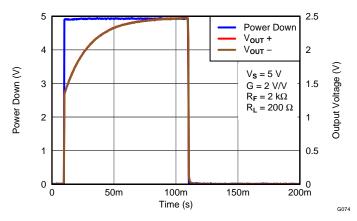

| Turn-on time delay                                                 | Time from $\overline{PD}$ = high to $V_{OUT}$ = 90% of final value, $R_L$ = 200 $\Omega$   |      | 650         |      |          |                              |

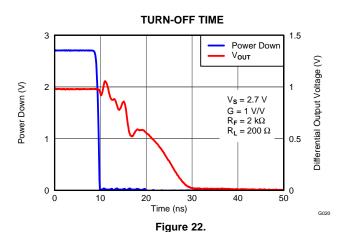

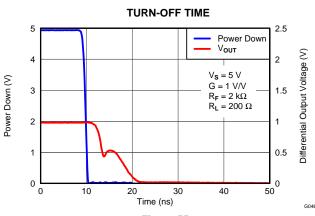

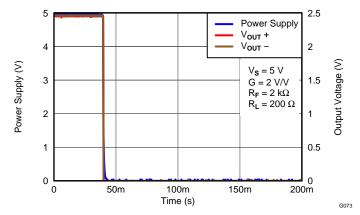

| Turn-off time delay                                                | Time from $\overline{PD}$ = low to $V_{OUT}$ = 10% of original value, $R_L$ = 200 $\Omega$ |      | 20          |      | ns       | С                            |

| OUTPUT COMMON-MODE VOLT                                            | TAGE CONTROL (V <sub>OCM</sub> )                                                           |      |             |      |          |                              |

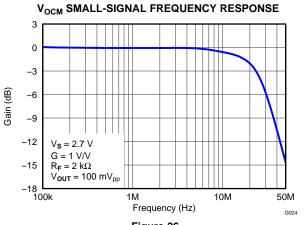

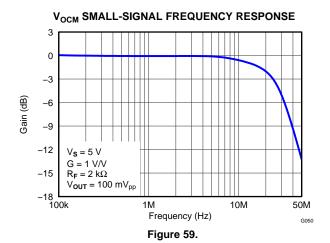

| Small-signal bandwidth                                             | V <sub>OCM</sub> input = 100 mV <sub>PP</sub>                                              |      | 23          |      | MHz      | С                            |

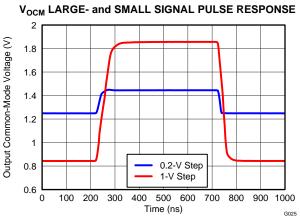

| Slew rate                                                          | V <sub>OCM</sub> input = 1 V <sub>STEP</sub>                                               |      | 14          |      | V/µs     | С                            |

| Gain                                                               |                                                                                            | 0.99 | 0.996       | 1.01 | V/V      | Α                            |

| Common-mode offset voltage                                         | Offset = output common-mode voltage – V <sub>OCM</sub> input voltage                       |      | ±1          | ±5   | mV       | А                            |

| V <sub>OCM</sub> input bias current                                | $V_{OCM} = (V_{S+} - V_{S-})/2$                                                            |      | ±20         | ±100 | nA       | Α                            |

| V <sub>OCM</sub> input voltage range                               |                                                                                            | 0.8  | 0.75 to 1.9 | 1.75 | V        | Α                            |

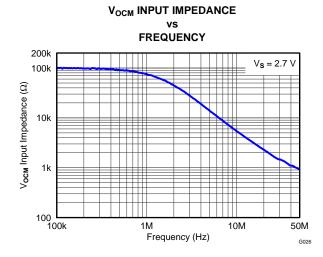

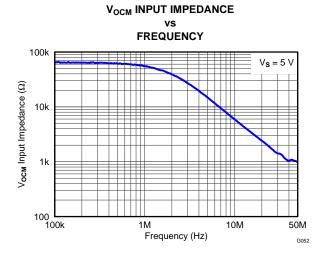

| V <sub>OCM</sub> input impedance                                   |                                                                                            |      | 100    1.6  |      | kΩ    pF | С                            |

| Default voltage offset from (V <sub>S+</sub> – V <sub>S-</sub> )/2 | Offset = output common-mode voltage – (V <sub>S+</sub> – V <sub>S-</sub> )/2               |      | ±3          | ±10  | mV       | А                            |

# **ELECTRICAL CHARACTERISTICS:** V<sub>s</sub> = 5 V

Test conditions at  $T_A = +25^{\circ}C$ ,  $V_{S+} = 5$  V,  $V_{S-} = 0$  V,  $V_{OCM} = open$ ,  $V_{OUT} = 2$   $V_{PP}$ ,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                            | CONDITIONS                                       | MIN TYP MA | X UNITS | TEST<br>LEVEL <sup>(1)</sup> |

|--------------------------------------|--------------------------------------------------|------------|---------|------------------------------|

| AC PERFORMANCE                       |                                                  |            |         |                              |

|                                      | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 1  | 36         |         |                              |

| Consult aimmed be an abridath        | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 2  | 17         | N41.1-  |                              |

| Small-signal bandwidth               | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 5  | 6          | MHz     |                              |

|                                      | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10 | 2.7        |         |                              |

| Gain-bandwidth product               | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10 | 27         | MHz     |                              |

| Large-signal bandwidth               | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1     | 36         | MHz     |                              |

| Bandwidth for 0.1-dB flatness        | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1     | 15         | MHz     |                              |

| Slew rate, rise/fall, 25% to 75%     |                                                  | 220/390    | V/µs    |                              |

| Rise/fall time, 10% to 90%           |                                                  | 4.6/5.6    | ns      |                              |

| Settling time to 1%, rise/fall       | , , , , , , , , , , , , , , , , , , ,            | 25/20      | ns      | <u> </u>                     |

| Settling time to 0.1%, rise/fall     | V <sub>OUT</sub> = 2 V <sub>Step</sub>           | 60/60      | ns      |                              |

| Settling time to 0.01%, rise/fall    |                                                  | 150/110    | ns      |                              |

| Overshoot/undershoot, rise/fall      |                                                  | 1/1        | %       |                              |

|                                      | f = 1 kHz, V <sub>OUT</sub> = 1 V <sub>RMS</sub> | -122       |         | С                            |

| 2nd-order harmonic distortion        | f = 10 kHz                                       | -128       | dBc     | C                            |

|                                      | f = 1 MHz                                        | -60        |         |                              |

|                                      | f = 1 kHz, V <sub>OUT</sub> = 1 V <sub>RMS</sub> | -130       |         |                              |

| 3rd-order harmonic distortion        | f = 10 kHz                                       | -137       | dBc     |                              |

|                                      | f = 1 MHz                                        | -71        |         |                              |

| 2nd-order intermodulation distortion | f = 1 MHz, 200-kHz tone spacing,                 | -85        | dBc     |                              |

| 3rd-order intermodulation distortion | V <sub>OUT</sub> envelope = 2 V <sub>PP</sub>    | -83        | UBC     |                              |

| Input voltage noise                  | f = 1 kHz                                        | 10         | nV/√Hz  |                              |

| Voltage noise 1/f corner frequency   |                                                  | 45         | Hz      |                              |

| Input current noise                  | f = 100 kHz                                      | 0.25       | pA/√Hz  |                              |

| Current noise 1/f corner frequency   |                                                  | 6.5        | kHz     |                              |

| Overdrive recovery time              | Overdrive = 0.5 V                                | 65         | ns      |                              |

| Output balance error                 | V <sub>OUT</sub> = 100 mV, f = 1 MHz             | -67        | dB      |                              |

| Closed-loop output impedance         | f = 1 MHz (differential)                         | 2.5        | Ω       |                              |

<sup>(1)</sup> Test levels (all values set by characterization and simulation): (A) 100% tested at +25°C; over temperature limits by characterization and simulation. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

# **ELECTRICAL CHARACTERISTICS:** V<sub>s</sub> = 5 V (continued)

Test conditions at  $T_A = +25$ °C,  $V_{S+} = 5$  V,  $V_{S-} = 0$  V,  $V_{OCM} = open$ ,  $V_{OUT} = 2$   $V_{PP}$ ,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                 | CONDITIONS                                                                         | MIN                    | TYP                    | MAX                    | UNITS    | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------------------------------|------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|----------|------------------------------|

| DC PERFORMANCE                            |                                                                                    | <u> </u>               |                        |                        |          |                              |

| Open-loop voltage gain (A <sub>OL</sub> ) |                                                                                    | 100                    | 114                    |                        | dB       | Α                            |

|                                           | T <sub>A</sub> = +25°C                                                             |                        | ±200                   | ±1000                  |          | Α                            |

| langua mafanna di affa at contana         | $T_A = 0$ °C to +70°C                                                              |                        |                        | ±1405                  | /        |                              |

| Input-referred offset voltage             | $T_A = -40$ °C to +85°C                                                            |                        |                        | ±1650                  | μV       | В                            |

|                                           | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                               |                        |                        | ±2000                  |          |                              |

|                                           | $T_A = 0$ °C to +70°C                                                              |                        | ±1.7                   | ±9                     |          |                              |

| Input offset voltage drift (2)            | $T_A = -40$ °C to +85°C                                                            |                        | ±2                     | ±10                    | μV/°C    | В                            |

|                                           | $T_A = -40$ °C to +125°C                                                           |                        | ±2                     | ±10                    |          |                              |

|                                           | T <sub>A</sub> = +25°C                                                             |                        | 160                    | 210                    |          | Α                            |

|                                           | $T_A = 0$ °C to +70°C                                                              |                        |                        | 222                    |          |                              |

| Input bias current                        | $T_A = -40$ °C to +85°C                                                            |                        |                        | 223                    | nA       | В                            |

|                                           | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                               |                        |                        | 235                    |          |                              |

|                                           | $T_A = 0$ °C to +70°C                                                              |                        | 0.04                   | 0.25                   | nA/°C    | В                            |

| Input bias current drift <sup>(2)</sup>   | $T_A = -40$ °C to +85°C                                                            |                        | 0.04                   | 0.25                   |          |                              |

| •                                         | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                               |                        | 0.04                   | 0.25                   |          |                              |

|                                           | T <sub>A</sub> = +25°C                                                             |                        | ±5                     | ±50                    |          | Α                            |

|                                           | $T_A = 0$ °C to +70°C                                                              |                        |                        | ±59                    |          |                              |

| Input offset current                      | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                |                        |                        | ±60                    | nA       | В                            |

|                                           | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                               |                        |                        | ±75                    |          |                              |

|                                           | $T_A = 0$ °C to +70°C                                                              |                        | ±0.05                  | ±0.2                   |          |                              |

| Input offset current drift <sup>(2)</sup> | $T_A = -40$ °C to +85°C                                                            |                        | ±0.05                  | ±0.2                   | nA/°C    | В                            |

|                                           | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                               |                        | ±0.05                  | ±0.2                   |          |                              |

| INPUT                                     | 1                                                                                  |                        |                        |                        |          |                              |

|                                           | T <sub>A</sub> = +25°C, CMRR > 87 dB                                               |                        | V <sub>S</sub> 0.2     | V <sub>S-</sub>        |          | Α                            |

| Common-mode input: low                    | $T_A = -40$ °C to +125°C, CMRR > 87 dB                                             |                        | V <sub>S</sub> 0.2     | V <sub>S</sub> _       | V        | В                            |

|                                           | T <sub>A</sub> = +25°C, CMRR > 87 dB                                               | V <sub>S+</sub> - 1.2  |                        | -                      |          | Α                            |

| Common-mode input: high                   | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ CMRR} > 87 \text{ dB}$ | V <sub>S+</sub> – 1.2  |                        |                        | V        | В                            |

| Common-mode rejection ratio               |                                                                                    | 90                     | 116                    |                        | dB       | Α                            |

| Input impedance common-mode               |                                                                                    |                        | 200    1.2             |                        |          | С                            |

| Input impedance differential mode         |                                                                                    |                        | 200    1               |                        | kΩ    pF | С                            |

| OUTPUT                                    |                                                                                    |                        |                        |                        |          |                              |

|                                           | T <sub>A</sub> = +25°C                                                             |                        | V <sub>S-</sub> + 0.1  | V <sub>S-</sub> + 0.2  |          | Α                            |

| Linear output voltage: low                | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                               |                        | V <sub>S-</sub> + 0.1  | V <sub>S</sub> _ + 0.2 |          | В                            |

|                                           | T <sub>A</sub> = +25°C                                                             | V <sub>S+</sub> - 0.25 | V <sub>S+</sub> - 0.12 |                        | V        | Α                            |

| Linear output voltage: high               | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                               | V <sub>S+</sub> - 0.25 | V <sub>S+</sub> - 0.12 |                        |          | В                            |

| Output saturation voltage: high/low       |                                                                                    |                        | 120/100                |                        | mV       | С                            |

| Linear output current drive               | $T_A = +25$ °C                                                                     | ±15                    | ±25                    |                        | m ^      | Α                            |

| Linear output current drive               | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                     | ±15                    |                        |                        | mA       | В                            |

<sup>(2)</sup> Input offset voltage drift, input bias current drift, and input offset current drift are average values calculated by taking data at the end points, computing the difference, and dividing by the temperature range.

# **ELECTRICAL CHARACTERISTICS:** V<sub>S</sub> = 5 V (continued)

Test conditions at  $T_A$  = +25°C,  $V_{S+}$  = 5 V,  $V_{S-}$  = 0 V,  $V_{OCM}$  = open,  $V_{OUT}$  = 2  $V_{PP}$ ,  $V_{PP}$ ,  $V_{PP}$  = 2  $V_{PP}$ ,  $V_{L}$  = 2  $V_{L}$  differential,  $V_{L}$  = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                                          | CONDITIONS                                                                                 | MIN  | TYP             | MAX  | UNITS    | TEST<br>LEVEL <sup>(1)</sup> |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|-----------------|------|----------|------------------------------|

| POWER SUPPLY                                                       |                                                                                            |      |                 |      |          |                              |

| Specified operating voltage                                        |                                                                                            | 2.5  |                 | 5.5  | V        | В                            |

| Ouissess as arating augreent/ob                                    | $T_A = 25^{\circ}C, \overline{PD} = V_{S+}$                                                |      | 250             | 350  |          | Α                            |

| Quiescent operating current/ch                                     | $T_A = -40$ °C to 125°C, $\overline{PD} = V_{S+}$                                          |      | 290             | 390  | μA       | В                            |

| Power-supply rejection (±PSRR)                                     |                                                                                            | 87   | 108             |      | dB       | Α                            |

| POWER DOWN                                                         |                                                                                            |      |                 |      |          |                              |

| Enable voltage threshold                                           | Specified on above 2.1 V                                                                   |      |                 | 2.1  | V        | Α                            |

| Disable voltage threshold                                          | Specified off below 0.7 V                                                                  | 0.7  |                 |      | V        | Α                            |

| Disable pin bias current                                           | $\overline{PD} = V_{S-} + 0.5 \text{ V}$                                                   |      | 50              | 500  | nA       | Α                            |

| Power-down quiescent current                                       | <del>PD</del> = V <sub>S-</sub> + 0.5 V                                                    |      | 0.5             | 2    | μA       | Α                            |

| Turn-on time delay                                                 | Time from $\overline{PD}$ = high to $V_{OUT}$ = 90% of final value, $R_L$ = 200 $\Omega$   |      | 600             |      |          |                              |

| Turn-off time delay                                                | Time from $\overline{PD}$ = low to $V_{OUT}$ = 10% of original value, $R_L$ = 200 $\Omega$ |      | 15              |      | ns       | С                            |

| OUTPUT COMMON-MODE VOLTA                                           | AGE CONTROL (V <sub>OCM</sub> )                                                            |      |                 |      |          |                              |

| Small-signal bandwidth                                             | V <sub>OCM</sub> input = 100 mV <sub>PP</sub>                                              |      | 24              |      | MHz      | С                            |

| Slew rate                                                          | V <sub>OCM</sub> input = 1 V <sub>STEP</sub>                                               |      | 15              |      | V/µs     | С                            |

| Gain                                                               |                                                                                            | 0.99 | 0.996           | 1.01 | V/V      | Α                            |

| Common-mode offset voltage                                         | Offset = output common-mode voltage – V <sub>OCM</sub> input voltage                       |      | ±1              | ±5   | mV       | Α                            |

| V <sub>OCM</sub> input bias current                                | $V_{OCM} = (V_{S+} - V_{S-})/2$                                                            |      | ±20             | ±120 | nA       | Α                            |

| V <sub>OCM</sub> input voltage range                               |                                                                                            | 0.95 | 0.75 to<br>4.15 | 4.0  | V        | Α                            |

| V <sub>OCM</sub> input impedance                                   |                                                                                            |      | 65    0.86      |      | kΩ    pF | С                            |

| Default voltage offset from (V <sub>S+</sub> – V <sub>S-</sub> )/2 | Offset = output common-mode voltage – (V <sub>S+</sub> – V <sub>S-</sub> )/2               |      | ±3              | ±10  | mV       | А                            |

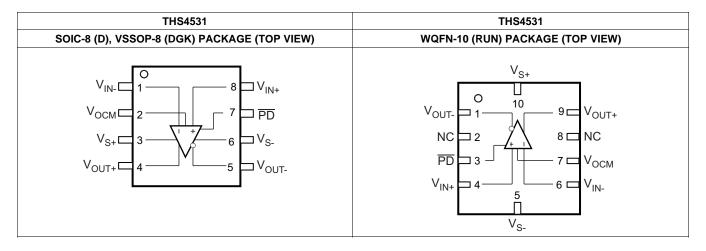

#### **DEVICE INFORMATION**

# **PIN CONFIGURATIONS**

#### **PIN FUNCTIONS**

| NUMBER      | NAME                  | DESCRIPTION                                                                                                                    |  |  |  |  |  |

|-------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| -           | HS4531 D, DGK PACKAGE |                                                                                                                                |  |  |  |  |  |

| 1           | V <sub>IN</sub> _     | Inverted (negative) output feedback                                                                                            |  |  |  |  |  |

| 2           | V <sub>OCM</sub>      | Common-mode voltage input                                                                                                      |  |  |  |  |  |

| 3           | V <sub>S+</sub>       | Amplifier positive power-supply input                                                                                          |  |  |  |  |  |

| 4           | V <sub>OUT+</sub>     | Noninverted amplifier output                                                                                                   |  |  |  |  |  |

| 5           | V <sub>OUT</sub>      | Inverted amplifier output                                                                                                      |  |  |  |  |  |

| 6           | V <sub>S-</sub>       | Amplifier negative power-supply input. Note V <sub>S</sub> tied together on multichannel devices.                              |  |  |  |  |  |

| 7           | PD                    | Power-down, $\overline{PD}$ = logic low = low power mode, $\overline{PD}$ = logic high = normal operation (PIN MUST BE DRIVEN) |  |  |  |  |  |

| 8           | V <sub>IN+</sub>      | Noninverted amplifier input                                                                                                    |  |  |  |  |  |

| THS4531 RUN | PACKAG                | E                                                                                                                              |  |  |  |  |  |

| 1           | V <sub>OUT</sub>      | Inverted amplifier output                                                                                                      |  |  |  |  |  |

| 2, 8        | NC                    | No internal connection                                                                                                         |  |  |  |  |  |

| 3           | PD                    | Power-down, $\overline{PD}$ = logic low = low power mode, $\overline{PD}$ = logic high = normal operation (PIN MUST BE DRIVEN) |  |  |  |  |  |

| 4           | V <sub>IN+</sub>      | Noninverted amplifier input                                                                                                    |  |  |  |  |  |

| 5           | V <sub>S-</sub>       | Amplifier negative power-supply input. Note V <sub>S</sub> tied together on multichannel devices.                              |  |  |  |  |  |

| 6           | V <sub>IN</sub> -     | Inverting amplifier input                                                                                                      |  |  |  |  |  |

| 7           | V <sub>OCM</sub>      | Common-mode voltage input                                                                                                      |  |  |  |  |  |

| 9           | V <sub>OUT+</sub>     | Noninverted amplifier output                                                                                                   |  |  |  |  |  |

| 10          | V <sub>S+</sub>       | Amplifier positive power-supply input                                                                                          |  |  |  |  |  |

# **TABLE OF GRAPHS**

| Description                                                         | V <sub>S</sub> = 2.7 V | V <sub>S</sub> = 5 V |

|---------------------------------------------------------------------|------------------------|----------------------|

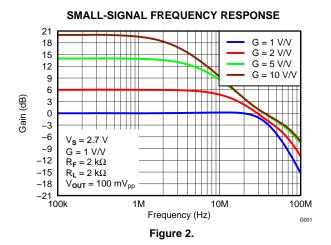

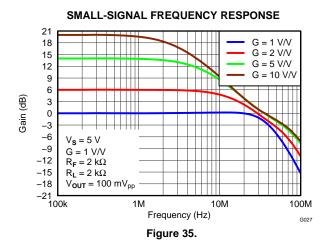

| Small-signal frequency response                                     | Figure 2               | Figure 35            |

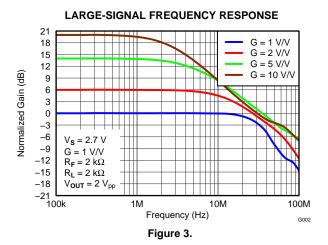

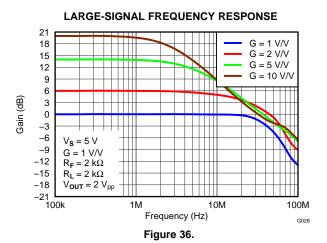

| Large-signal frequency response                                     | Figure 3               | Figure 36            |

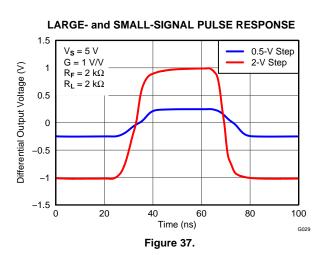

| Large- and small- signal pulse response                             | Figure 4               | Figure 37            |

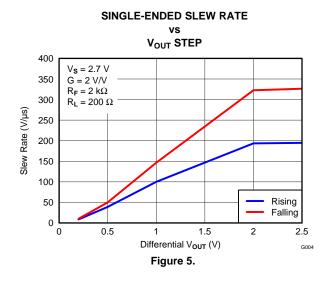

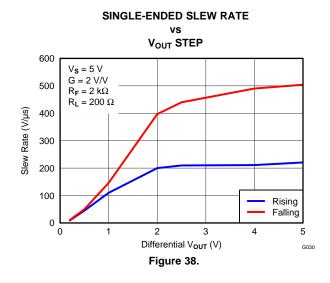

| Single-ended slew rate vs V <sub>OUT</sub> step                     | Figure 5               | Figure 38            |

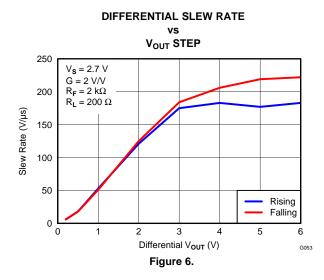

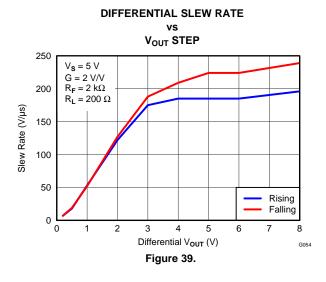

| Differential slew rate vs V <sub>OUT</sub> step                     | Figure 6               | Figure 39            |

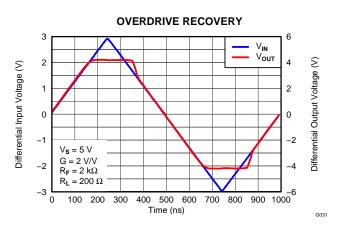

| Overdrive recovery                                                  | Figure 7               | Figure 40            |

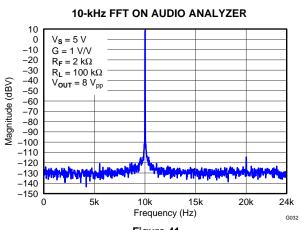

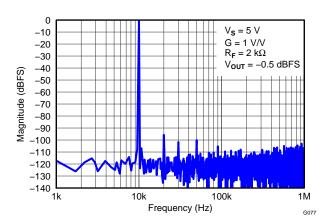

| 10-kHz FFT on audio analyzer                                        | Figure 8               | Figure 41            |

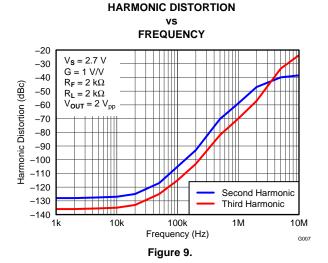

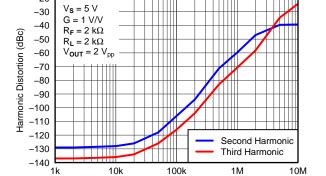

| Harmonic distortion vs Frequency                                    | Figure 9               | Figure 42            |

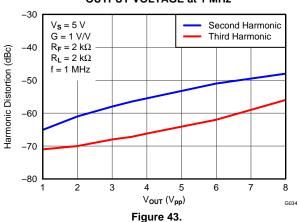

| Harmonic distortion vs Output voltage at 1 MHz                      | Figure 10              | Figure 43            |

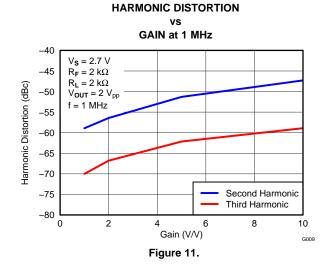

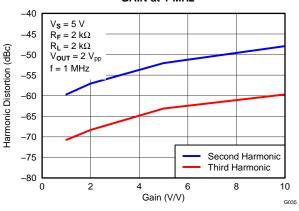

| Harmonic distortion vs Gain at 1 MHz                                | Figure 11              | Figure 44            |

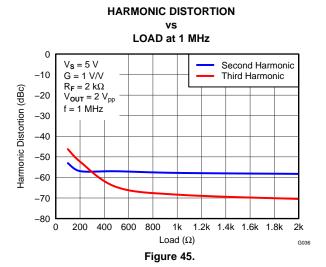

| Harmonic distortion vs Load at 1 MHz                                | Figure 12              | Figure 45            |

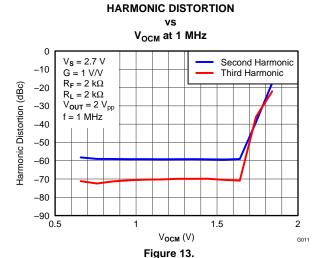

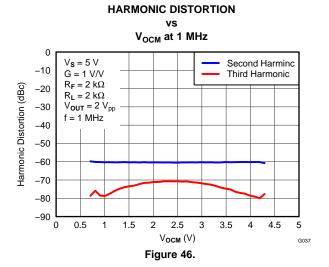

| Harmonic distortion vs V <sub>OCM</sub> at 1 MHz                    | Figure 13              | Figure 46            |

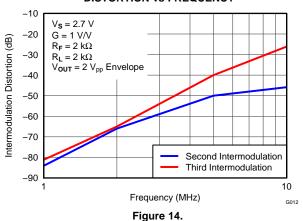

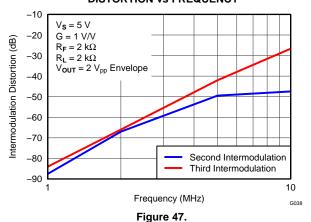

| Two-tone, 2nd and 3rd order intermodulation distortion vs Frequency | Figure 14              | Figure 47            |

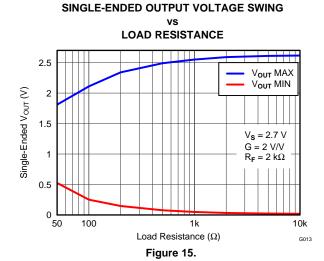

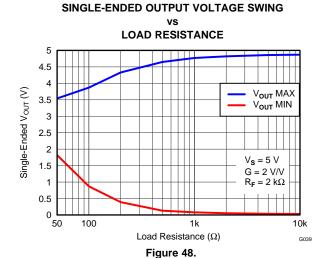

| Single-ended output voltage swing vs Load resistance                | Figure 15              | Figure 48            |

| Single-ended output saturation voltage vs Load current              | Figure 16              | Figure 49            |

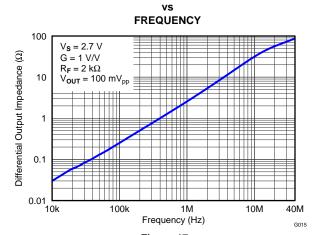

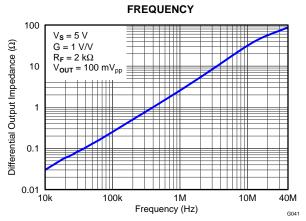

| Main amplifier differential output impedance vs Frequency           | Figure 17              | Figure 50            |

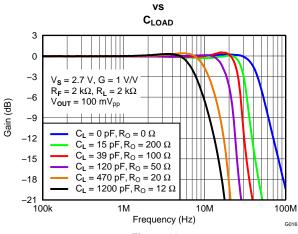

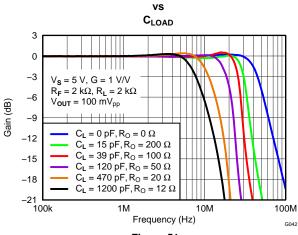

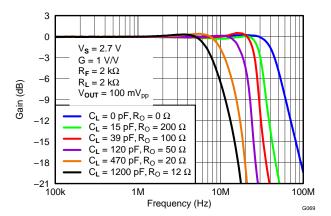

| Frequncy response vs C <sub>LOAD</sub>                              | Figure 18              | Figure 51            |

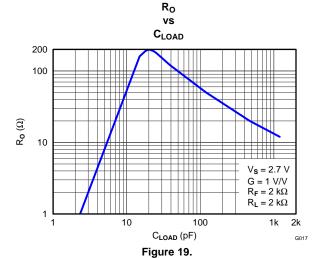

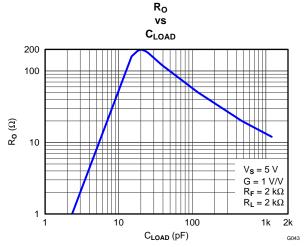

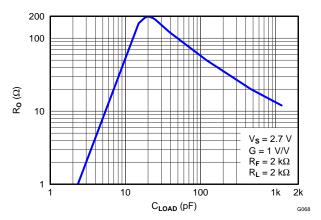

| R <sub>O</sub> vs C <sub>LOAD</sub>                                 | Figure 19              | Figure 52            |

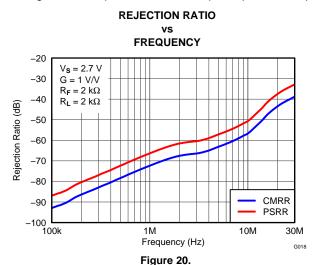

| Rejection ratio vs Frequency                                        | Figure 20              | Figure 53            |

| Turn-on time                                                        | Figure 21              | Figure 54            |

| Turn-off time                                                       | Figure 22              | Figure 55            |

| Input-referred voltage noise and current noise spectral density     | Figure 23              | Figure 56            |

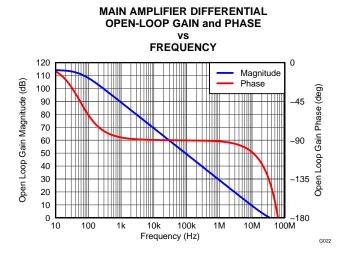

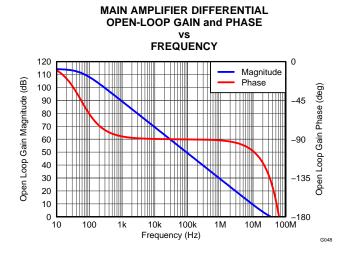

| Main amplifier differential open-loop gain and phase vs Frequency   | Figure 24              | Figure 57            |

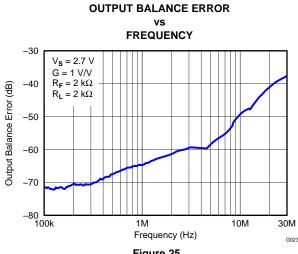

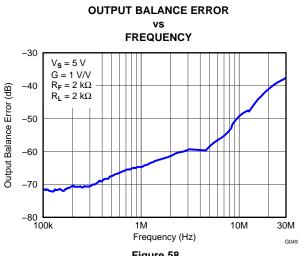

| Output balance error vs Frequency                                   | Figure 25              | Figure 58            |

| V <sub>OCM</sub> small signal frequency response                    | Figure 26              | Figure 59            |

| V <sub>OCM</sub> large and small signal pulse response              | Figure 27              | Figure 60            |

| V <sub>OCM</sub> input impedance vs frequency                       | Figure 28              | Figure 61            |

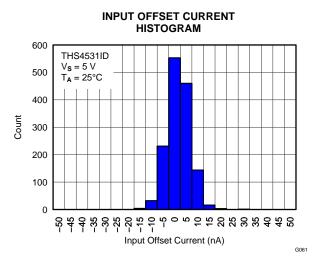

| Count vs input offset current                                       | Figure 29              | Figure 62            |

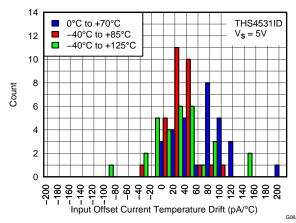

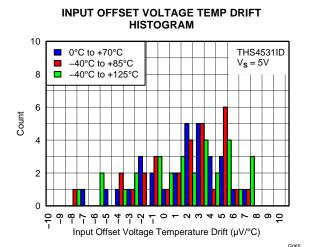

| Count vs input offset current temperature drift                     | Figure 30              | Figure 63            |

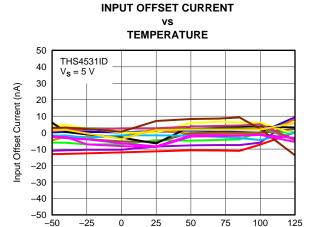

| Input offset current vs temperature                                 | Figure 31              | Figure 64            |

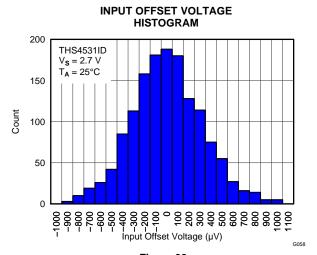

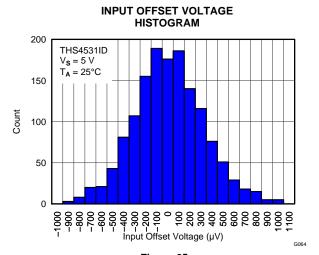

| Count vs input offset voltage                                       | Figure 32              | Figure 65            |

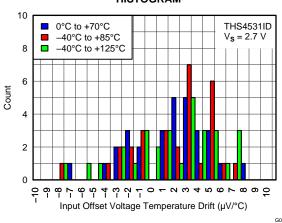

| Count vs input offset voltage temperature drift                     | Figure 33              | Figure 66            |

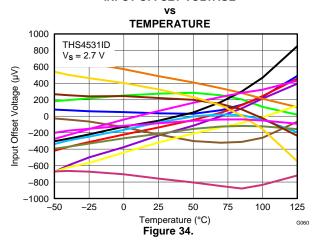

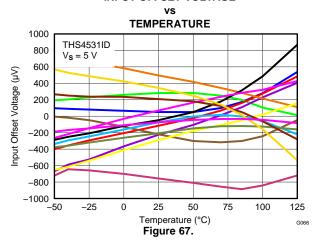

| Input offset voltage vs temperature                                 | Figure 34              | Figure 67            |

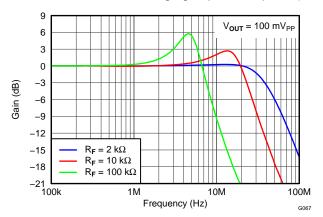

## TYPICAL CHARACTERISTICS: V<sub>S</sub> = 2.7V

Test conditions unless otherwise noted:  $V_{S+}=2.7~V,~V_{S-}=0V,~CM=open,~V_{OUT}=2Vpp,~R_F=2k\Omega,~R_L=2k\Omega$  Differential, G = 1V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply unless otherwise noted.

#### LARGE- and SMALL-SIGNAL PULSE RESPONSE 1.5 $V_{S} = 2.7 \ V$ 0.5-V Step G = 1 V/V 2-V Step Differential Output Voltage (V) $R_F = 2 k\Omega$ $R_L = 2 k\Omega$ 0.5 0 -0.5 -1.5 20 100 Time (ns) G003 Figure 4.

Test conditions unless otherwise noted:  $V_{S+}=2.7~V,~V_{S-}=0V,~CM=open,~V_{OUT}=2Vpp,~R_F=2k\Omega,~R_L=2k\Omega$  Differential, G=1V/V,~Single-Ended~Input,~Differential~Output,~Input~and~Output~Referenced~to~mid-supply~unless~otherwise~noted.

#### HARMONIC DISTORTION **OUTPUT VOLTAGE at 1 MHz** -10 Second Harmonic -20 Third Harmonic Harmonic Distortion (dBc) V<sub>S</sub> = 2.7 V -30 G = 1 V/V $R_F = 2 k\Omega$ -40 $R_L = 2 k\Omega$ f = 1 MHz -50 -60 -70 -80 3 4 $V_{OUT} (V_{pp})$ G008 Figure 10.

Test conditions unless otherwise noted:  $V_{S+}=2.7~V,~V_{S-}=0V,~CM=open,~V_{OUT}=2Vpp,~R_F=2k\Omega,~R_L=2k\Omega$  Differential, G=1V/V,~Single-Ended~Input,~Differential~Output,~Input~and~Output~Referenced~to~mid-supply~unless~otherwise~noted.

#### HARMONIC DISTORTION VS LOAD at 1 MHz 0 $V_{S} = 2.7 \ V$ Second Harmonic -10 G = 1 V/VThird Harmonic $R_F = 2 k\Omega$ Harmonic Distortion (dBc) -20 $V_{OUT} = 2 V_{pp}$ f = 1 MHz -30 -40 -50 -60 -70 -80 800 1k 1.2k 1.4k 1.6k 1.8k 400 600 Load $(\Omega)$ Figure 12.

# TWO-TONE, 2<sup>nd</sup> and 3<sup>rd</sup>ORDER INTERMODULATION DISTORTION vs FREQUENCY

Test conditions unless otherwise noted:  $V_{S+}=2.7~V,~V_{S-}=0V,~CM=open,~V_{OUT}=2Vpp,~R_F=2k\Omega,~R_L=2k\Omega$  Differential, G=1V/V,~Single-Ended~Input,~Differential~Output,~Input~and~Output~Referenced~to~mid-supply~unless~otherwise~noted.

# SINGLE-ENDED OUTPUT SATURATION VOLTAGE

####

Figure 16.

#### MAIN AMPLIFIER DIFFERENTIAL OUTPUT IMPEDANCE

Figure 17.

#### FREQUENCY RESPONSE

Figure 18.

Test conditions unless otherwise noted:  $V_{S+}=2.7~V,~V_{S-}=0V,~CM=open,~V_{OUT}=2Vpp,~R_F=2k\Omega,~R_L=2k\Omega$  Differential, G=1V/V,~Single-Ended~Input,~Differential~Output,~Input~and~Output~Referenced~to~mid-supply~unless~otherwise~noted.

Figure 21.

Copyright © 2011–2012, Texas Instruments Incorporated

Test conditions unless otherwise noted:  $V_{S+}=2.7~V,~V_{S-}=0V,~CM=open,~V_{OUT}=2Vpp,~R_F=2k\Omega,~R_L=2k\Omega$  Differential, G=1V/V,~Single-Ended~Input,~Differential~Output,~Input~and~Output~Referenced~to~mid-supply~unless~otherwise~noted.

Figure 24.

Figure 25.

Figure 26.

Figure 27.

Test conditions unless otherwise noted:  $V_{S+}=2.7~V,~V_{S-}=0V,~CM=open,~V_{OUT}=2Vpp,~R_F=2k\Omega,~R_L=2k\Omega$  Differential, G=1V/V,~Single-Ended~Input,~Differential~Output,~Input~and~Output~Referenced~to~mid-supply~unless~otherwise~noted.

Figure 28.

Figure 29.

# INPUT OFFSET CURRENT TEMP DRIFT HISTOGRAM

Figure 30.

Figure 31.

Test conditions unless otherwise noted:  $V_{S+}=2.7~V,~V_{S-}=0V,~CM=open,~V_{OUT}=2Vpp,~R_F=2k\Omega,~R_L=2k\Omega$  Differential, G=1V/V,~Single-Ended~Input,~Differential~Output,~Input~and~Output~Referenced~to~mid-supply~unless~otherwise~noted.

# INPUT OFFSET VOLTAGE TEMP DRIFT HISTOGRAM

Figure 32.

Figure 33.

#### **INPUT OFFSET VOLTAGE**

# TYPICAL CHARACTERISTICS: V<sub>s</sub> = 5V

Test conditions unless otherwise noted:  $V_{S+} = 5 \text{ V}$ ,  $V_{S-} = 0 \text{V}$ ,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2 \text{Vpp}$ ,  $R_F = 2 \text{k}\Omega$ ,  $R_L = 2 \text{k}\Omega$  Differential, G = 1 V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^{\circ}\text{Cunless}$  otherwise noted.

## TYPICAL CHARACTERISTICS: $V_s = 5V$ (continued)

Test conditions unless otherwise noted:  $V_{S+} = 5 \text{ V}$ ,  $V_{S-} = 0 \text{V}$ ,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2 \text{Vpp}$ ,  $R_F = 2 \text{k}\Omega$ ,  $R_L = 2 \text{k}\Omega$  Differential, G = 1 V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^{\circ}\text{Cunless}$  otherwise noted.

-20

HARMONIC DISTORTION

**FREQUENCY**

#### Figure 41.

HARMONIC DISTORTION

vs

OUTPUT VOLTAGE at 1 MHz

HARMONIC DISTORTION

Figure 42.

Frequency (Hz)

Figure 44.

Test conditions unless otherwise noted:  $V_{S+} = 5 \text{ V}$ ,  $V_{S-} = 0 \text{V}$ ,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2 \text{Vpp}$ ,  $R_F = 2 \text{k}\Omega$ ,  $R_L = 2 \text{k}\Omega$  Differential, G = 1 V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^{\circ}\text{Cunless}$  otherwise noted.

# TWO-TONE, 2<sup>nd</sup> and 3<sup>rd</sup>ORDER INTERMODULATION DISTORTION vs FREQUENCY

Output Saturation Voltage (V)

0.2

0.1

#### TYPICAL CHARACTERISTICS: $V_s = 5V$ (continued)

Test conditions unless otherwise noted:  $V_{S+} = 5 \text{ V}$ ,  $V_{S-} = 0 \text{V}$ ,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2 \text{Vpp}$ ,  $R_F = 2 \text{k}\Omega$ ,  $R_L = 2 \text{k}\Omega$  Differential, G = 1 V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^{\circ}\text{Cunless}$  otherwise noted.

30

# SINGLE-ENDED OUTPUT SATURATION VOLTAGE vs LOAD CURRENT 1.2 1.2 V<sub>SAT</sub> High V<sub>SAT</sub> Low V<sub>S</sub> = 5 V G = 2 V/V R<sub>F</sub> = 2 k $\Omega$ 0.4

Differential Load Current (mA) Figure 49.

# MAIN AMPLIFIER DIFFERENTIAL OUTPUT IMPEDANCE vs

Figure 50.

#### FREQUENCY RESPONSE

Figure 51.

Figure 52.

Test conditions unless otherwise noted:  $V_{S+} = 5 \text{ V}$ ,  $V_{S-} = 0 \text{V}$ ,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2 \text{Vpp}$ ,  $R_F = 2 \text{k}\Omega$ ,  $R_L = 2 \text{k}\Omega$  Differential, G = 1 V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^{\circ}\text{Cunless}$  otherwise noted.

#### **REJECTION RATIO** vs **FREQUENCY** -20 V<sub>S</sub> = 5 V -30 G = 1 V/V $R_F = 2 k\Omega$ -40 $R_L = 2 k\Omega$ Rejection Ratio (dB) -50 -60 -70 -80 CMRR -90 **PSRR** -100 **└** 100k

10M 30M Frequency (Hz) Figure 53.

Figure 54.

1000

## TYPICAL CHARACTERISTICS: V<sub>s</sub> = 5V (continued)

Test conditions unless otherwise noted:  $V_{S+} = 5 \text{ V}$ ,  $V_{S-} = 0 \text{V}$ ,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2 \text{Vpp}$ ,  $R_F = 2 \text{k}\Omega$ ,  $R_L = 2 \text{k}\Omega$  Differential, G = 1 V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^{\circ}\text{Cunless}$  otherwise noted.

Figure 57.

Figure 58.

$V_{\text{OCM}}$  LARGE- and SMALL SIGNAL PULSE RESPONSE

Figure 60.

Output Common-Mode Voltage (V) 0.2-V Step 2.2 1-V Step 2 1.8 100 200 300 400 500 600 700 800 0

3

2.8

2.6

2.4

24

Test conditions unless otherwise noted:  $V_{S+} = 5 \text{ V}$ ,  $V_{S-} = 0 \text{V}$ ,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2 \text{Vpp}$ ,  $R_F = 2 \text{k}\Omega$ ,  $R_L = 2 \text{k}\Omega$  Differential, G = 1 V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^{\circ}\text{Cunless}$  otherwise noted.

Figure 61.

Figure 62.

# INPUT OFFSET CURRENT TEMP DRIFT HISTOGRAM

Figure 63.

Figure 64.

Temperature (°C)

Test conditions unless otherwise noted:  $V_{S+} = 5 \text{ V}$ ,  $V_{S-} = 0 \text{V}$ ,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2 \text{Vpp}$ ,  $R_F = 2 \text{k}\Omega$ ,  $R_L = 2 \text{k}\Omega$  Differential, G = 1 V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^{\circ}\text{Cunless}$  otherwise noted.

Figure 65.

Figure 66.

#### **INPUT OFFSET VOLTAGE**

#### APPLICATION INFORMATION

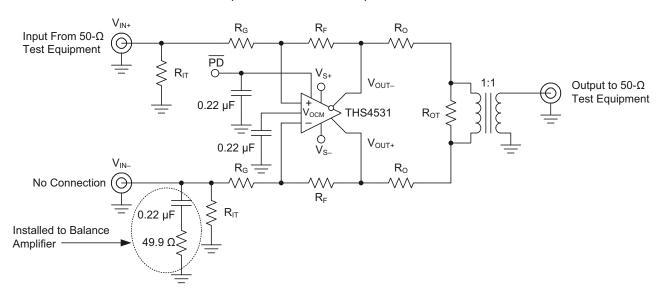

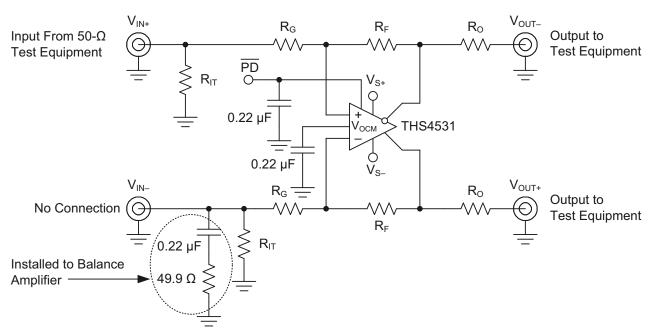

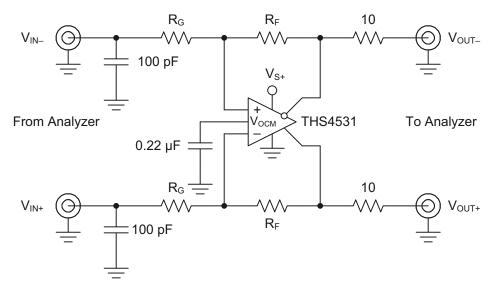

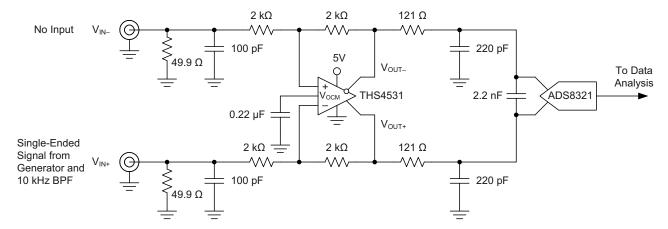

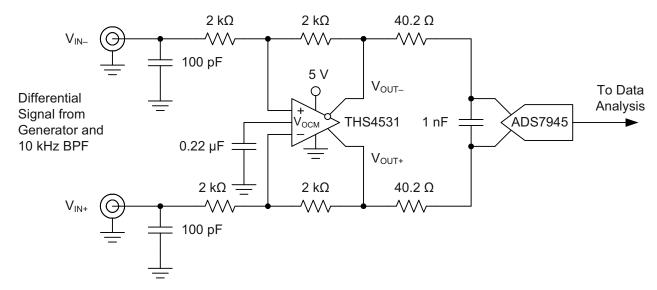

#### TYPICAL CHARACTERISTICS TEST CIRCUITS

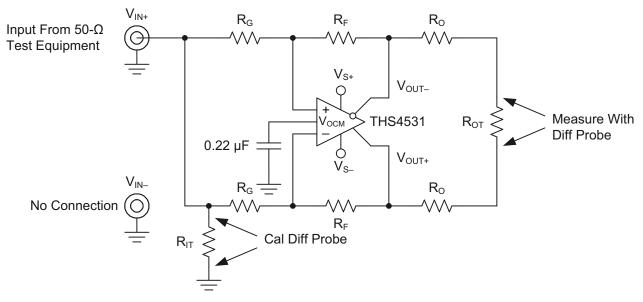

Figure 68 shows the general test circuit built on the EVM that was used for testing the THS4531. For simplicity, power supply decoupling is not shown – please see layout in the applications section for recommendations. Depending on the test conditions, component values are changed per Table 2 and Table 3, or as otherwise noted. Some of the signal generators used are ac coupled  $50\Omega$  sources and a  $0.22\mu F$  cap and  $49.9\Omega$  resistor to ground are inserted across  $R_{IT}$  on the un-driven or alternate input as shown to balance the circuit. Split-power supply is used to ease the interface to common lab test equipment, but if properly biased, the amplifier can be operated single-supply as described in the applications section with no impact on performance. For most of the tests, the devices are tested with single ended input and a transformer on the output to convert the differential output to single ended because common lab test equipment have single ended inputs and outputs. Performance is the same or better with differential input and differential output.

Figure 68. General Test Circuit

Table 2. Gain Component Values for Single-Ended Input<sup>(1)</sup>

| GAIN   | R <sub>F</sub> | $R_G$ | R <sub>IT</sub> |

|--------|----------------|-------|-----------------|

| 1 V/V  | 2kΩ            | 2kΩ   | 51.1Ω           |

| 2 V/V  | 2kΩ            | 1kΩ   | 52.3Ω           |

| 5 V/V  | 2kΩ            | 392Ω  | 53.6Ω           |

| 10 V/V | 2kΩ            | 187kΩ | 57.6Ω           |

<sup>(1)</sup> Note components are chosen to achieve gain and 50Ω input termination. Resistor values shown are closest standard values so gains are approximate.

Table 3. Load Component Values For 1:1 Differential to Single-Ended Output Transformer (1)

| $R_L$ | R <sub>O</sub> | R <sub>OT</sub> | ATTEN |

|-------|----------------|-----------------|-------|

| 100Ω  | 25Ω            | open            | 6     |

| 200Ω  | 86.6Ω          | 69.8Ω           | 16.8  |

| 499Ω  | 237Ω           | 56.2Ω           | 25.5  |

| 1kΩ   | 487Ω           | 52.3Ω           | 31.8  |

| 2kΩ   | 976Ω           | 51.1Ω           | 37.9  |

<sup>(1)</sup> Note the total load includes  $50\Omega$  termination by the test equipment. Components are chosen to achieve load and  $50\Omega$  line termination through a 1:1 transformer. Resistor values shown are closest standard values so loads are approximate.

Due to the voltage divider on the output formed by the load component values, the amplifier's output is attenuated. The column "Atten" in Table 3 shows the attenuation expected from the resistor divider. When using a transformer at the output as shown in Figure 68, the signal will see slightly more loss due to transformer and line loss, and these numbers will be approximate. The standard output load used for most tests is  $2k\Omega$  with associated 37.9dB of loss.

#### Frequency Response, and Output Impedance

The circuit shown in Figure 68 is used to measure the frequency response of the amplifier.

A network analyzer is used as the signal source and the measurement device. The output impedance of the network analyzer is  $50\Omega$  and is DC coupled.  $R_{IT}$  and  $R_{G}$  are chosen to impedance match to  $50\Omega$  and maintain the proper gain. To balance the amplifier, a  $49.9\Omega$  resistor to ground is inserted across  $R_{IT}$  on the alternate input.

The output is routed to the input of the network analyzer via  $50\Omega$  coax. For 2k load, 37.9dB is added to the measurement to refer back to the amplifier's output per Table 3.

For output impedance, the signal is injected at  $V_{OUT}$  with  $V_{IN}$  left open. The voltage drop across the 2x  $R_{O}$  resistors is measured with a high impedance differential probe and used to calculate the impedance seen looking into the amplifier's output.

#### Distortion

At 1MHz and above, the circuit shown in Figure 68 is used to measure harmonic, intermodulation distortion, and output impedance of the amplifier.

A signal generator is used as the signal source and the output is measured with a spectrum analyzer. The output impedance of the signal generator is  $50\Omega$  and is AC coupled.  $R_{IT}$  and  $R_{G}$  are chosen to impedance match to  $50\Omega$  and maintain the proper gain. To balance the amplifier, a  $0.22\mu F$  cap and  $49.9\Omega$  resistor to ground is inserted across  $R_{IT}$  on the alternate input. A low-pass filter is inserted in series with the input to reduce harmonics generated at the signal source. The level of the fundamental is measured and then a high-pass filter is inserted at the output to reduce the fundamental so it does not generate distortion in the input of the spectrum analyzer.

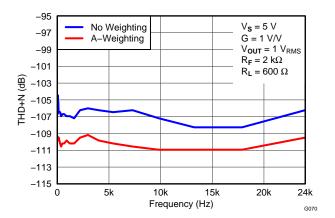

Distortion in the audio band is measured using an audio analyzer. Refer to audio measurement section for detail.

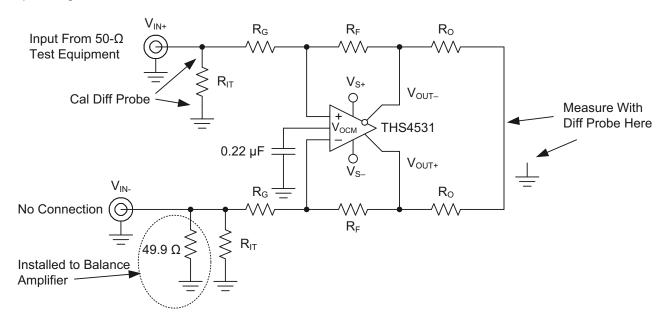

#### Slew Rate, Transient Response, Settling Time, Overdrive, Output Voltage, and Turn-On/Off Time

The circuit shown in Figure 69 is used to measure slew rate, transient response, settling time, overdrive recovery, and output voltage swing. Turn on and turn off times are measured with  $50\Omega$  input termination on the PD input, by replacing the  $0.22\mu F$  capacitor with  $49.9\Omega$  resistor.

Figure 69. Slew Rate, Transient Response, Settling Time, Z<sub>O</sub>, Overdrive Recovery, V<sub>OUT</sub> Swing, and Turn-on/off Test Circuit

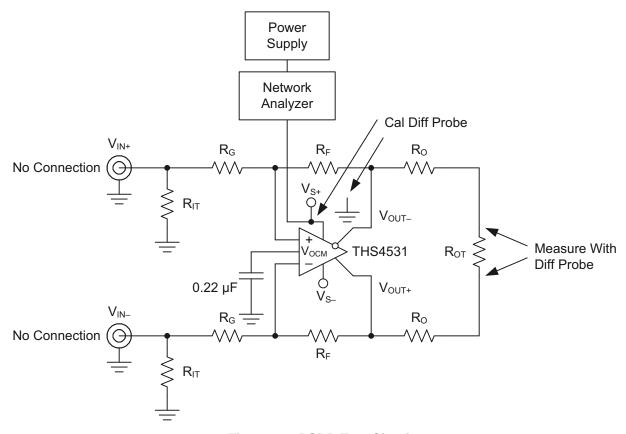

## **Common-Mode and Power Supply Rejection**

The circuit shown in Figure 70 is used to measure the CMRR. The signal from the network analyzer is applied common-mode to the input.

Figure 70. CMRR Test Circuit

Figure 71 is used to measure the PSRR of  $V_{S+}$  and  $V_{S-}$ . The power supply is applied to the network analyzer's DC offset input. For both CMRR and PSRR, the output is probed using a high impedance differential probe across  $R_{OT}$ .

Figure 71. PSRR Test Circuit

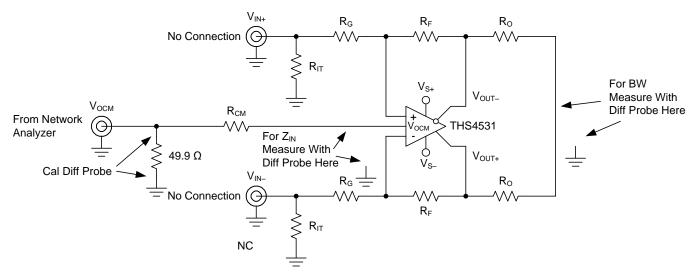

#### **V<sub>OCM</sub> Input**

The circuit shown in Figure 72 is used to measure the transient response, frequency response and input impedance of the  $V_{OCM}$  input. For these tests, the cal point is across the  $49.9\Omega~V_{OCM}$  termination resistor. Transient response and frequency response are measured with  $R_{CM}=0\Omega$  and using a high impedance differential probe at the summing junction of the two  $R_{O}$  resistors, with respect to ground. The input impedance is measured using a high impedance differential probe at the  $V_{OCM}$  pin and the drop across  $R_{CM}$  is used to calculate the impedance seen looking into the amplifier's  $V_{OCM}$  input.

Figure 72. V<sub>OCM</sub> Input Test Circuit

#### **Balance Error**

The circuit shown in Figure 73 is used to measure the balance error of the main differential amplifier. A network analyzer is used as the signal source and the measurement device. The output impedance of the network analyzer is  $50\Omega$  and is DC coupled.  $R_{IT}$  and  $R_{G}$  are chosen to impedance match to  $50\Omega$  and maintain the proper gain. To balance the amplifier, a  $49.9\Omega$  resistor to ground is inserted across  $R_{IT}$  on the alternate input. The output is measured using a high impedance differential probe at the summing junction of the two  $R_{O}$  resistors, with respect to ground.

Figure 73. Balance Error Test Circuit

#### **APPLICATION CIRCUITS**

The following circuits show application information for the THS4531. For simplicity, power supply decoupling capacitors are not shown in these diagrams – please see the EVM and Layout Recommendations section for recommendations. For more detail on the use and operation of fully differential op amps refer to application report "Fully-Differential Amplifiers" SLOA054D.

#### **Differential Input to Differential Output Amplifier**

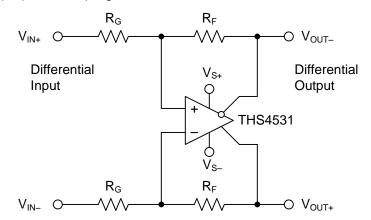

The THS4531 is a fully differential op amp and can be used to amplify differential <u>inp</u>ut signals to differential output signals. A basic block diagram of the circuit is shown in Figure 74 ( $V_{OCM}$  and PD inputs not shown). The gain of the circuit is set by  $R_F$  divided by  $R_G$ .

Figure 74. Differential Input to Differential Output Amplifier

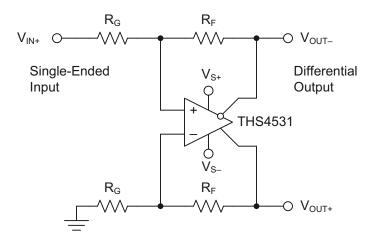

#### Single-Ended Input to Differential Output Amplifier

The THS4531 can also be used to amplify and convert single-ended input signals to differential output signals. A basic block diagram of the circuit is shown in Figure 75 ( $V_{OCM}$  and  $\overline{PD}$  inputs not shown). The gain of the circuit is again set by  $R_F$  divided by  $R_G$ .

Figure 75. Single-Ended Input to Differential Output Amplifier

#### **Differential Input to Single-Ended Output Amplifier**

Fully differential op amps like the THS4531 are not recommended for differential to single-ended conversion. This application is best performed with an instrumentation amplifier or with a standard op amp configured as a classic differential amplifier. See application section of the OPA835 data sheet (SLOS713).

#### Input Common-Mode Voltage Range

The input common-model voltage of a fully differential op amp is the voltage at the "+ and -" input pins of the op amp.

It is important to not violate the input common-mode voltage range ( $V_{ICR}$ ) of the op amp. Assuming the op amp is in linear operation the voltage across the input pins is only a few millivolts at most. So finding the voltage at one input pin will determine the input common-mode voltage of the op amp.

Treating the negative input as a summing node, the voltage is given by:

$$\left(V_{OUT+} \times \frac{R_G}{R_G + R_F}\right) + \left(V_{IN-} \times \frac{R_F}{R_G + R_F}\right) \tag{1}$$

To determine the V<sub>ICR</sub> of the op amp, the voltage at the negative input is evaluated at the extremes of V<sub>OUT+</sub>.

As the gain of the op amp increases, the input common-mode voltage becomes closer and closer to the input common-mode voltage of the source.

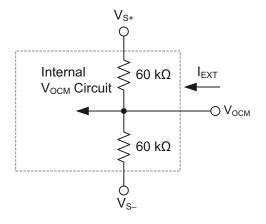

#### **Setting the Output Common-Mode Voltage**