ZHCACB6 March 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507 , MSPM0L1105 , MSPM0L1106 , MSPM0L1303 , MSPM0L1304 , MSPM0L1305 , MSPM0L1306 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346

设计说明

该子系统演示了如何在可编程增益放大器 (PGA) 配置中设置 MSPM0 内部运算放大器,动态更改增益,输出放大的信号以及使用 ADC 读取结果。该配置使用户能够使用具有高增益的小输入电压信号极大地提高分辨率,但随后仍然能够通过更改为较低的增益来对较大的信号进行采样。下载该示例的代码。

图 1 显示了该子系统的功能图。

图 1 子系统功能方框图

图 1 子系统功能方框图所需外设

该应用需要一个集成的 OPA 和 ADC。

| 子块功能 | 外设使用 | 说明 |

|---|---|---|

| 增益放大器 | (1 个)OPA | 在代码中称为“OPA_0_INST” |

| 模拟信号捕获 | (1 个)ADC12 | 在代码中称为“ADC12_0_INST” |

兼容器件

根据表 1 中的要求,该示例与表 2 中的器件兼容。相应的 EVM 可用于原型设计。

| 兼容器件 | EVM |

|---|---|

| MSPM0L13xx | LP-MSPM0L1306 |

| MSPM0G35xx、 MSPM0G15xx |

LP-MSPM0G3507 |

设计步骤

- 确定要应用于所需信号的最高和最低增益设置。OPA 模块可提供的最低增益为 2,最大增益为 32。如果还使用 ADC 进行采样,请参阅“设计注意事项”。

- 计算系统相对于最大输入电压的最小增益:Equation1.

- 计算系统相对于所需的最小输入电压的最大增益:Equation2.

其中:

- Gmax 是为 OPA 选择的最大系统增益设置

- Gmin 是为 OPA 选择的最小系统增益设置

- Vin_max 是最大输入电压。

- Vin_min 是所需的最小输入电压。

- VADC_Ref 是 ADC 基准电压。

- 计算系统相对于最大输入电压的最小增益:

-

计算给定输入电压和增益下进入 ADC 的电压:

Equation3.其中:

- VADCin 是 ADC 输入采样的电压

- VOPAin 是 OPA 的电压输入

- GOPA 是为 OPA 设置的电流增益

- 计算给定 ADC 输入电压的 ADC 代码:Equation4.

其中:

- NADC 是 ADC 转换生成的数字代码

- 使用以下公式计算给定 ADC 代码的 OPA 输入电压。在确定 OPA 增益转换的 ADC 窗口比较器值时,该公式和设计步骤 3 中的公式在以下步骤中很有用。Equation5.

- 计算高侧转换电平。如果 ADC 读数高于该值,则此示例会在可能的情况下减小 OPA 增益。在本示例中,高侧转换电平设置为最大 ADC 电平的上 5%。Equation6.

其中 HT 是上限百分比。

- 计算低侧转换电平。如果 ADC 读数低于该值,则此示例会在可能的情况下增大 OPA 增益。在本示例中,低侧转换电平设置为最大 ADC 电平的下 40%。Equation7.

其中 LT 是下限百分比。

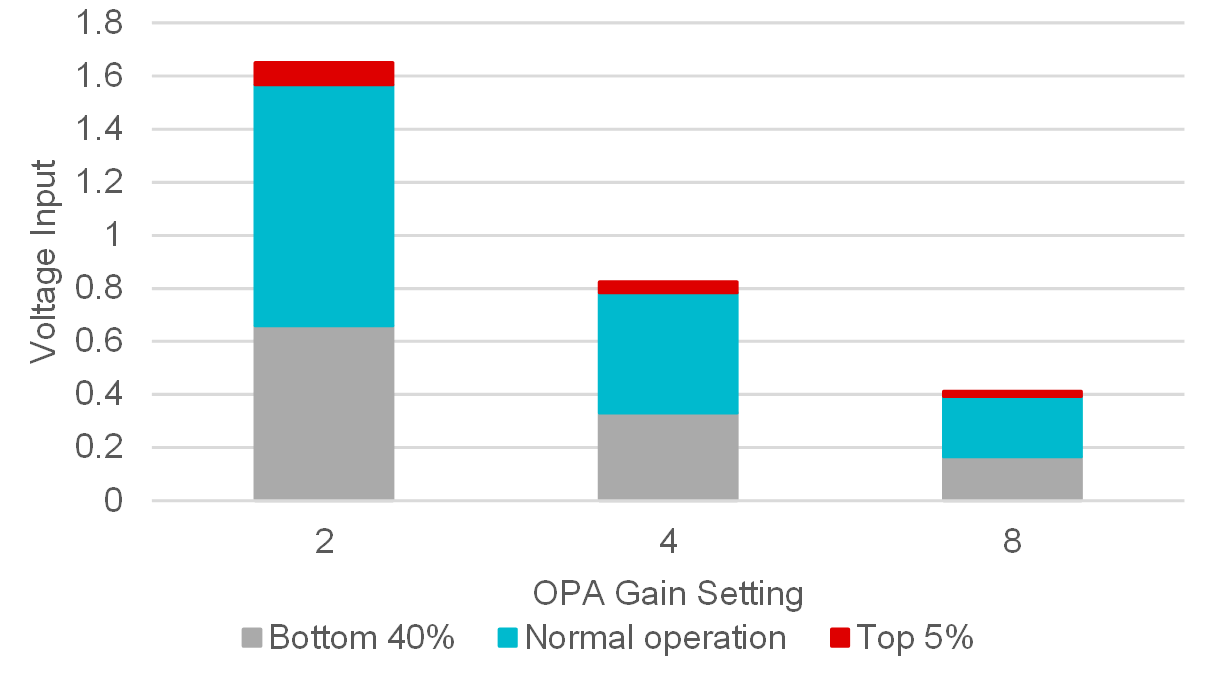

- 可以在下图中以可视化方式显示不同 OPA 增益设置下设计步骤 5 和 6 中讨论的电平(HT 是上 5%;LT 是下 40%)。选择这些值有助于在较低电压电平输入下尽可能地提高分辨率,并为转换提供一些缓冲。在下图中,红色对应于设计步骤 5 转换电平,灰色表示设计步骤 6 转换电平,最后蓝色区域表示增益保持不变的电压范围。有关选择转换电平的更多信息,请参阅“设计注意事项”中的第 6 条。

- 使用外部输入和外部输出在 SysConfig 中设置 OPA 以进行 PGA 配置。

- 在 SysConfig 中将 ADC 设置为以 VCC 为基准 (VRef_ADC) 的窗口比较器模式,对 OPA 输出进行采样。

- 使用设计步骤 3 中的公式将设计步骤 5 和 6 中确定的转换电平转换为 ADC 代码,并将其置于 SysConfig 中的 ADC 窗口比较器限制中。

- (可选)设置 ADC 以同时使用所选的 ADCMEMx 对 OPA 输出进行采样。

- 将 SysConfig 中的 ADC 采样时间设置为器件数据表中给出的 tSample_PGA 的最小时间。

设计注意事项

- OPA 电源是 MSPM0 的 VCC。

- OPA GBW 设置:OPA 的较低 GBW 设置消耗的电流较小,但响应速度较慢。相反,较高的 GBW 消耗的电流较大,但压摆率较大,使能和稳定时间较短。有关这些模式之间的确切规格差异,请查看特定于器件的数据表

- OPA 增益转换:如果需要跳过 OPA 增益水平,则必须在 ADC 窗口比较器中断服务例程 (ISR) 中添加额外的代码,以显式配置 OPA 增益设置,而不是仅增大或减小增益水平。请注意,在设计步骤 5 和 6 中计算的转换电平也反映了这种类型的转换。

- 最小 OPA 增益:MSPM0 MCU 能够在不禁用 OPA 的情况下动态更改 OPA 增益设置。PGA 配置中 OPA 的最小增益为 2。要从增益 2 更改为 OPA 缓冲器配置(OPA 增益 = 1),必须执行本文档范围之外的额外程序以将 OPA 重新配置为该模式。

- ADC 基准选择:MSPM0 器件可以从内部基准发生器 (VREF)、外部源或 MCU VCC 向 ADC 提供基准电压。请查看 MSPM0 器件数据表,了解可用于所选器件的选项。所选基准电压设置了 ADC 可以采样的满量程范围,并且必须适应最大 OPA 输出电压。

-

ADC 窗口比较器电平:

- 在通过从较低的增益值转换为较高的增益值(例如:G = 2 -> 4)来增大输入信号的放大率时,使用设计步骤 2 中的公式确定为转换选择的电压电平是否未隔离新增益设置下的信号。

- 在通过从较高的增益值向下转换为较低的增益值(例如:G = 4 -> 2)来减小输入信号的放大率时,确保选择的电压电平大于在“设计注意事项”第 6.a 条中选择的转换电平。这是为了避免可能导致系统不稳定的增益变化循环。

- ADC 采样:该示例在窗口比较器模式下持续对 OPA 输出进行采样。如果不需要持续监控 OPA 输出,则可使用计时器设置固定的采样间隔。

- ADC 结果:具有 OPA 输出的可选 ADC 采样的代码示例仅在全局变量 gADCResult 中存储最新捕获的结果。对数据执行操作之前,完整应用可以在一个数组中存储多个读数。

- ADC 结果:如果使用捕获 ADC 结果的选项,则必须添加代码以处理与当前 OPA 增益设置相关的正在处理的数据。这是因为 ADC 满量程范围随 OPA 增益设置而变化,因此在 OPA 的不同输入电压电平下可以看到相同的 ADC 代码。

- gCheckADC 上的竞态条件:该应用会尽快清除 gCheckADC。如果应用等待清除 gCheckADC 的时间过长,则可能会无意中丢失新数据。

软件流程图

图 2 显示了 Dynamic_PGA_Example2 的代码流程图,该流程图说明了 ADC 如何对 OPA 输出进行采样并更改 OPA 增益。Dynamic_PGA1_Example 的软件流程图略微简化了以下流程,因为主循环在启动 ADC 后进入睡眠状态,并且不存在 ADC 中断服务例程 (ISR) 的中心 switch case。

图 2 应用软件流程图

图 2 应用软件流程图器件配置

该应用利用 TI 系统配置工具 (SysConfig) 图形界面为 OPA 和 ADC 生成配置代码。使用图形界面配置器件外设可简化应用原型设计过程。

可以在 Dynamic_PGA1_Example.c 或 Dynamic_PGA_Example2.c 文件的 main() 开头部分找到图 2 中所示流程图的代码。

应用代码

以下代码片段显示了在何处调整 OPA 增益水平和转换点(与占最大 ADC 代码的百分比相关),如设计步骤 2 中所述。有关可用的 OPA 增益定义,请参阅 MSPM0 SDK 和 DriverLib 文档。

#include "ti_msp_dl_config.h"

#define HIGHMARGIN 3890 // 4095*0.75 = 75% of max ADC value

#define LOWMARGIN 1638 // 4095*0.25 = 25% of max ADC value

#define MAXGAIN DL_OPA_GAIN_N7_P8 // Maximum GAIN level of OPA wanted

#define MINGAIN DL_OPA_GAIN_N1_P2 // Minimum GAIN level of OPA wanted.

//For non-inverting PGA mode this is an OPA GAIN of 2x.See advisory in TRM for MIN GAIN.

以下代码片段显示了在何处添加自定义代码以在获取 ADC 结果后执行有用的操作。这通常是某种数学运算,将多个结果放入数组、过滤或查找表访问。

while (1) {

//This while loop waits until the next ADC result is loaded

while (false == gCheckADC) {

__WFE();

}

gCheckADC = false;

//Grab latest ADC Result

gADCResult = DL_ADC12_getMemResult(ADC12_0_INST, DL_ADC12_MEM_IDX_0);

//Add in code to do math on ADC results.

//Scaling factors for the math will be dependent on the current OPA Gain levels.

}以下代码片段显示了在何处根据 OPA 增益设置调整 ADC 结果解释。用户需要决定采取哪些操作以及如何关联将 ADC 结果与 OPA 增益设置和输入电压相关联。

switch (DL_ADC12_getPendingInterrupt(ADC12_0_INST)) {

case DL_ADC12_IIDX_WINDOW_COMP_HIGH:

// Entered high side margin window.Decrease OPA GAIN if possible.

tempGain = DL_OPA_getGain(OPA_0_INST);

if(tempGain > MINGAIN){

//Update OPA gain.

DL_OPA_decreaseGain(OPA_0_INST);

//For full applications, at this point you would want to adjust any math factors or

//look up tables to the new voltage ranges being captured by the ADC, or set a flag to do so in main while loop.

}

break;

case DL_ADC12_IIDX_WINDOW_COMP_LOW:

// Entered low side margin window.Increase OPA GAIN if possible.

tempGain = DL_OPA_getGain(OPA_0_INST);

if(tempGain < MAXGAIN){

//Update OPA gain.

DL_OPA_increaseGain(OPA_0_INST);

//For full applications, at this point you would want to adjust any math factors or

//look up tables to the new voltage ranges being captured by the ADC, or set a flag to do so in main while loop.

}

break;

default:

break;

}结果

下图显示了 OPA 输入变化和相应增益输出的屏幕截图。OPA 增益水平如下:2x、4x、8x。

图 3 增大 OPA PGA 增益

图 3 增大 OPA PGA 增益 图 4 减小 OPA PGA 增益

图 4 减小 OPA PGA 增益