JAJSC44B August 2015 – March 2017 UCC27714

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1 Selecting HI and LI Low Pass Filter Components (RHI, RLI, CHI, CLI)

- 8.2.2.2 Selecting Bootstrap Capacitor (CBOOT)

- 8.2.2.3 Selecting VDD Bypass/Holdup Capacitor (CVDD) and Rbias

- 8.2.2.4 Selecting Bootstrap Resistor (RBOOT)

- 8.2.2.5 Selecting Gate Resistor RHO/RLO

- 8.2.2.6 Selecting Bootstrap Diode

- 8.2.2.7 Estimate the UCC27714 Power Losses (PUCC27714)

- 8.2.2.8 Application Example Schematic Note

- 8.2.2.9 LO and HO Overshoot and Undershoot

- 8.2.3 Application Curves

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

1 特長

- それぞれ独立した入力を備えたハイサイドおよびローサイド構成

- 最大600Vで動作可能(HSピン)

- ブートストラップ動作用に設計されたフローティング・チャネル

- ピーク出力電流能力:4Aシンク、4Aソース(VDD = 15V時)

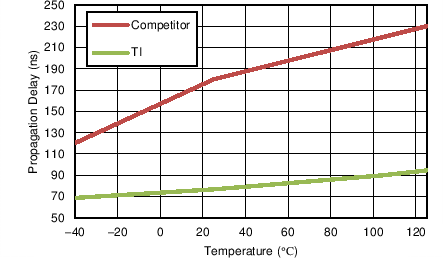

- クラス最小の伝播遅延(最大125ns)

- クラス最高の遅延マッチング性能(最大20ns)

- TTLおよびCMOS互換の入力ロジック

- VDDバイアス電源範囲:10V~20V

- 両方のチャネルに対するバイアスUVLO保護

- レール・ツー・レール駆動

- 負の過渡電圧時にも堅牢な動作

- 高いdv/dt耐性(HSピン)

- ロジック用(VSS)とドライバ用(COM)に個別のグランドを備え、電圧差に対応

- オプションのイネーブル機能(ピン4)

- 入力フローティング時に出力をLowに保持

- 入力およびイネーブル・ピンの電圧レベルがVDDピンのバイアス電源電圧に制限されない

- ハイサイドとローサイドの電圧ピンを個別に備えることで、沿面距離と空間距離を最大化

- 入力ピンとイネーブル・ピンに負電圧処理機能を搭載

2 アプリケーション

- オフラインのACおよびDC電源で使用されるハーフブリッジおよびフルブリッジ・コンバータ

- サーバ、通信、IT、および産業用インフラストラクチャ向けの高密度スイッチング電源

- ソーラー・インバータ、モーター・ドライブ、UPS

3 概要

UCC27714は、4Aのソース電流能力および4Aのシンク電流能力を持つ600Vのハイサイド/ローサイド・ゲート・ドライバであり、パワーMOSFETやIGBTの駆動に適しています。1つのグランド基準チャネル(LO)と、ブートストラップ電源で動作するよう設計された1つのフローティング・チャネル(HO)から構成されています。優れた堅牢性とノイズ耐性を備え、HSピンでは最大–8VDCの負電圧に対しても動作ロジックを保持できます(VDD = 12V時)。

10V~20Vの幅広いバイアス電源入力に対応し、VCCとHBの両方のバイアス電源ピンに対してUVLO保護を備えています。UCC27714は、SOIC-14パッケージで供給され、–40°C~125°Cの温度範囲で仕様が規定されています。

製品情報(1)

| 型番 | パッケージ | 本体サイズ(公称) |

|---|---|---|

| UCC27714 | SOIC (14) | 3.91mm×8.65mm |

(1) 提供されているすべてのパッケージについては、巻末の注文情報を参照してください。

概略回路図

標準的な伝播遅延の比較