SNAS187D February 2003 – January 2016 LMX2430 , LMX2433 , LMX2434

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description continued

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

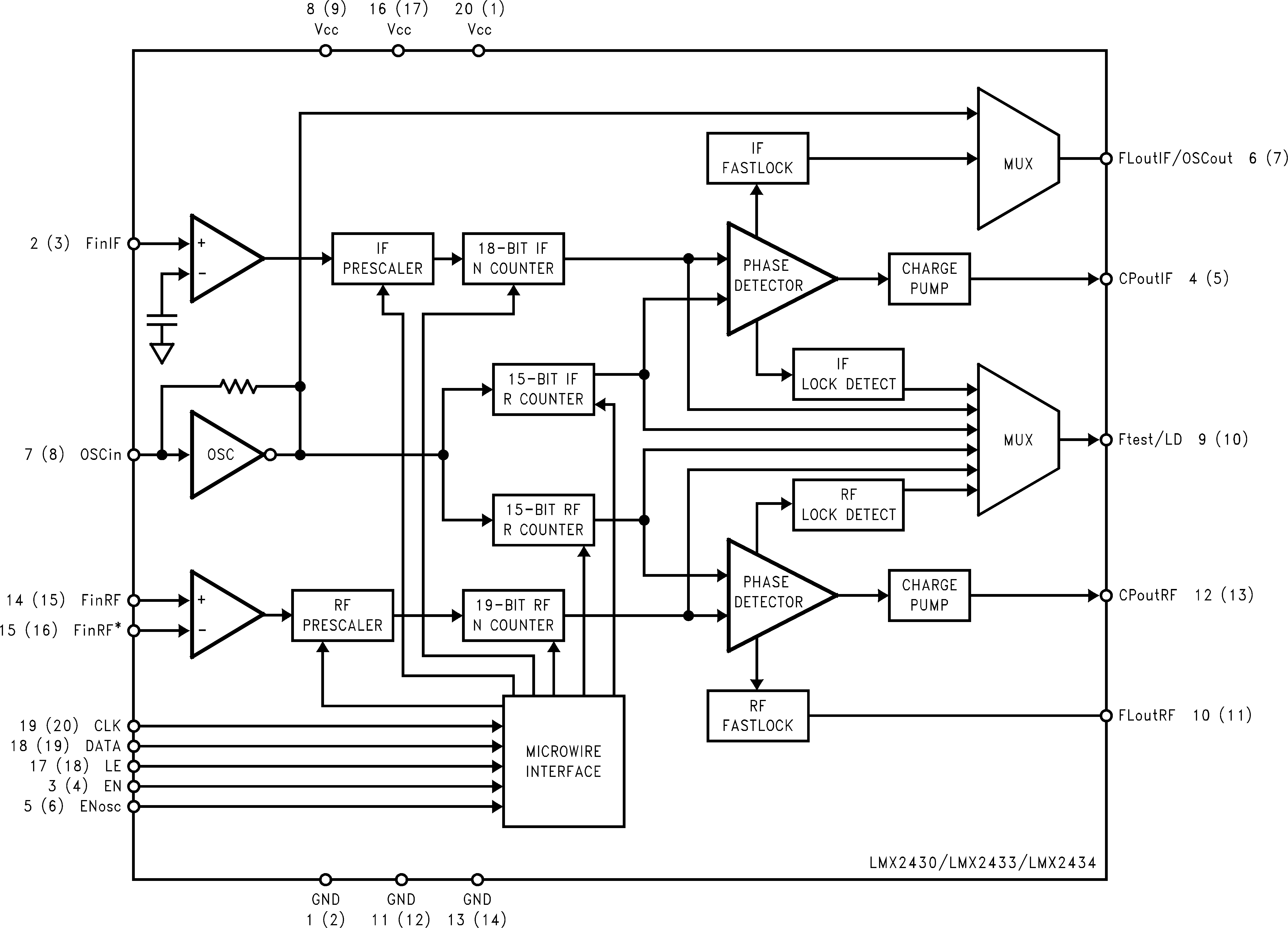

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4 Device Functional Modes

- 9.5 Programming

- 9.6

Register Maps

- 9.6.1 Control Register Content Map

- 9.6.2

R0 Register

- 9.6.2.1 RF_R[14:0] - RF Synthesizer Programmable Reference Divider (R Counter) (R0[17:3])

- 9.6.2.2 RF_CPP - RF Synthesizer Phase Detector Polarity (R0[18])

- 9.6.2.3 RF_CPG - RF Synthesizer Charge-Pump Current Gain (R0[19])

- 9.6.2.4 RF_CPT - RF Synthesizer Charge-Pump Tri-State (R0[20])

- 9.6.2.5 RF_RST - RF Synthesizer Counter Reset (R0[21])

- 9.6.3 R1 Register

- 9.6.4

R2 Register

- 9.6.4.1 RF_TOC[0:11] - RF Synthesizer Time-Out Counter (R2[14:3])

- 9.6.4.2

R3 Register

- 9.6.4.2.1 IF_R[14:0] - IF Synthesizer Programmable Reference Divider (R Counter) (R3[17:3])

- 9.6.4.2.2 IF_CPP - IF Synthesizer Phase Detector Polarity (R3[18])

- 9.6.4.2.3 IF_CPG - IF Synthesizer Charge-Pump Current Gain (R3[19])

- 9.6.4.2.4 IF_CPT - IF Synthesizer Charge-Pump Tri-State (R3[20])

- 9.6.4.2.5 IF_RST - IF Synthesizer Counter Reset (R3[21])

- 9.6.5 R4 Register

- 9.6.6 R5 Register

- 9.6.7 MUX[3:0] - Multifunction Output Select (R3[23:22]:R0[23:22])

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

1 Features

- Low Current Consumption

- LMX2430 (RF/IF): 2.8 mA/ 1.4 mA

- LMX2433 (RF/IF): 3.2 mA/ 2 mA

- LMX2434 (RF/IF): 4.6 mA/ 2.4 mA

- 2.25-V to 2.75-V Operation

- Synchronous/Asynchronous Power Down

- Multiple PLL Options:

- LMX2430 (RF/IF): 3 GHz /0.8 GHz

- LMX2433 (RF/IF): 3.6 GHz /1.7 GHz

- LMX2434 (RF/IF): 5 GHz /2.5 GHz

- Programmable Charge-Pump Current Levels

- RF and IF: 1 or 4 mA

- Fastlock With Integrated Time-Out Counters

- Digital Filtered Lock-Detect Output

- Analog Lock Detect (Push-Pull / Open-Drain)

- 1.8-V MICROWIRE Logic Interface

2 Applications

- Mobile Handsets

- Cordless Handsets

- Wireless Data

- Cable TV Tuners

3 Description

Using a proprietary digital-phase, locked-loop technique, the LMX243x devices generate very stable, low-noise control signals for RF and IF voltage controlled oscillators. Both the RF and IF synthesizers include a two-level programmable charge pump. Both the RF and IF PLLs have dedicated fastlock circuitry with integrated time-out counters which require only a single word write to power up or change frequencies.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| LMX243x | ULGA (20) | 3.50 mm × 3.50 mm |

| TSSOP (20) | 6.50 mm × 4.40 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

Functional Block Diagram

NOTE:

1 (2) refers to Pin 1 of the 20-Pin ULGA and Pin 2 of the 20-Pin TSSOP