ZHCSJ89B January 2019 – July 2022 ADS8353-Q1

PRODUCTION DATA

- 1特性

- 2应用

- 3说明

- 4Revision History

- 5Pin Configuration and Functions

- 6Specifications

- 7Detailed Description

- 8Application and Implementation

- 9Device and Documentation Support

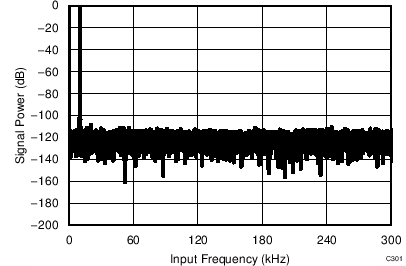

8.2.3 Application Curve

To minimize external components and to maximize the dynamic range of the ADC, the device is configured to operate with internal reference (CFR.B6 = 1) and 2x VREF_x input full-scale range (CFR.B9 = 1).

Figure 8-4 shows the FFT plot and test result obtained with the ADS8353-Q1 operating at full throughput with a 32-CLK interface and the circuit configuration of Figure 8-2.

| SNR = 83.5 dB, THD = –101.2 dB, fIN = 10.1 kHz |