-

ADS9110 18 位、2MSPS、15mW SAR ADC,具有 multiSPI 接口

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 Timing Requirements: Conversion Cycle

- 6.7 Timing Requirements: Asynchronous Reset, NAP, and PD

- 6.8 Timing Requirements: SPI-Compatible Serial Interface

- 6.9 Timing Requirements: Source-Synchronous Serial Interface (External Clock)

- 6.10 Timing Requirements: Source-Synchronous Serial Interface (Internal Clock)

- 6.11 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5

Programming

- 7.5.1 Data Transfer Frame

- 7.5.2 Interleaving Conversion Cycles and Data Transfer Frames

- 7.5.3 Data Transfer Protocols

- 7.5.4 Device Setup

- 7.6 Register Maps

- 8 Application and Implementation

- 9 Power-Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械封装和可订购信息

- 重要声明

DATA SHEET

ADS9110 18 位、2MSPS、15mW SAR ADC,具有 multiSPI 接口

本资源的原文使用英文撰写。 为方便起见,TI 提供了译文;由于翻译过程中可能使用了自动化工具,TI 不保证译文的准确性。 为确认准确性,请务必访问 ti.com 参考最新的英文版本(控制文档)。

1 特性

- 采样率:2MSPS

- 无延迟输出

- 出色的直流和交流性能:

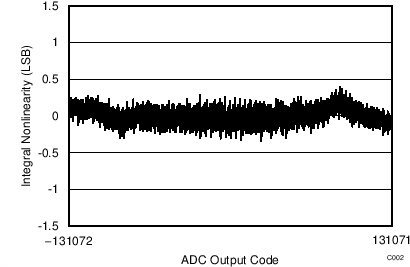

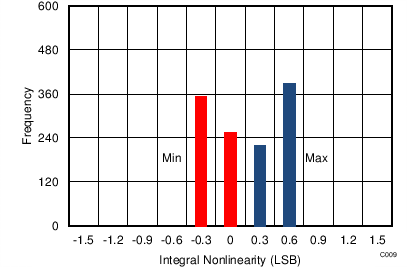

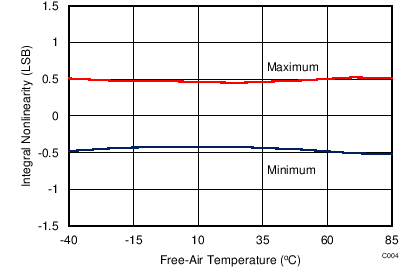

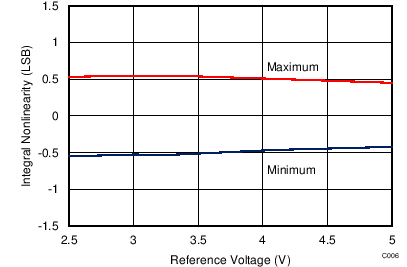

- 积分非线性 (INL):±0.5 最低有效位 (LSB)(典型值),±1.5 LSB(最大值)

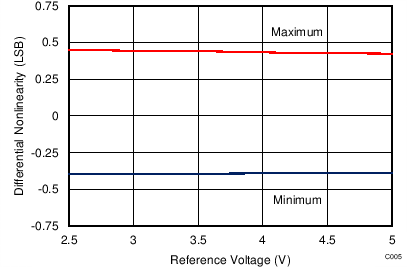

- 微分非线性 (DNL):±0.75 LSB(最大值),18 位无丢码 (NMC)

- 信噪比 (SNR):100dB

- 总谐波失真 (THD):-118dB

- 宽输入范围:

- 单极差分输入范围:±VREF

- VREF 输入范围:2.5V 至 5V,

与 AVDD 无关

- 低功耗:

- 2MSPS 时为 9mW(仅限 AVDD)

- 2MSPS 时为 15mW(总功耗)

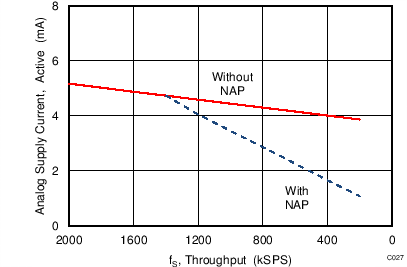

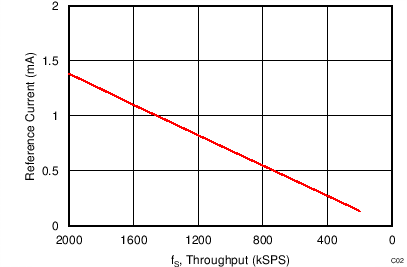

- 灵活的低功耗模式,可根据吞吐量调节功率

- multiSPI:增强型串行接口

- 符合 JESD8-7A 标准的数字 I/O(1.8V DVDD 时)

- 在 -40°C 至 +85°C 的工业温度范围内完全额定运行

- 小型封装:4mm × 4mm 超薄四方扁平无引线 (VQFN) 封装

2 应用

- 测试和测量

- 医疗成像

- 高精度、高速工业领域

3 说明

ADS9110 是一款 18 位、2MSPS、逐次逼近寄存器 (SAR) 模数转换器 (ADC),在典型工作条件下具有 ±0.5 LSB INL 和 100dB SNR 规范值。 高吞吐量使得开发者能够对输入信号进行过采样,从而提高测量的动态范围和精度。

该器件支持单极全差分模拟输入信号,并采用 2.5V 至 5V 的外部基准电压,能够提供宽输入选择范围,无需额外进行输入调节。

该器件以 2MSPS 全吞吐量运行时的功耗仅为 15mW。 吞吐量较低时,可灵活使用低功耗模式(NAP 和 PD)来降低功耗。

集成的 multiSPI 串行接口向后兼容传统 SPI™ 协议。 此外,该器件的可配置功能还能够简化电路板布局、时序和固件,并且以低时钟速度运行时能够获得高吞吐量,因此可轻松连接各种微控制器、数字信号处理器 (DSP) 以及现场可编程门阵列 (FPGA)。

该器件采用节省空间的 4mm × 4mm VQFN 封装,支持符合 JESD8-7A 标准的 I/O 和标准工业温度范围。

器件信息

| 部件号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| ADS9110 | VQFN (24) | 4.00mm x 4.00mm |

- 如需了解所有可用封装,请见数据表末尾的可订购米6体育平台手机版_好二三四附录。

典型应用图以及积分非线性度与代码间的关系图

5 Pin Configuration and Functions

RGE Package

VQFN-24

Top View

Pin Functions

| PIN | FUNCTION | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| AINM | 10 | Analog input | Negative analog input |

| AINP | 9 | Analog input | Positive analog input |

| AVDD | 13, 14 | Power supply | Analog power supply for the device |

| CONVST | 1 | Digital input | Conversion start input pin for the device. A CONVST rising edge brings the device from ACQ state to CNV state. |

| CS | 24 | Digital input | Chip-select input pin for the device; active low The device takes control of the data bus when CS is low. The SDO-x pins go to tri-state when CS is high. |

| DVDD | 16 | Power supply | Interface supply |

| GND | 11, 15 | Power supply | Ground |

| NC | 3, 6, 12 | No connection | These pins must be left floating with no external connection |

| REFM | 4, 8 | Analog input | Reference ground potential |

| REFP | 5, 7 | Analog input | Reference voltage input |

| RST | 2 | Digital input | Asynchronous reset input pin for the device. A low pulse on the RST pin resets the device and all register bits return to their default state. |

| RVS | 21 | Digital output | Multi-function output pin for the device. With CS held high, RVS reflects the status of the internal ADCST signal. With CS low, the status of RVS depends on the output protocol selection. |

| SCLK | 23 | Digital input | Clock input pin for the serial interface. All system-synchronous data transfer protocols are timed with respect to the SCLK signal. |

| SDI | 22 | Digital input | Serial data input pin for the device. This pin is used to feed the data or command into the device. |

| SDO-0 | 20 | Digital output | Serial communication: data output 0 |

| SDO-1 | 19 | Digital output | Serial communication: data output 1 |

| SDO-2 | 18 | Digital output | Serial communication: data output 2 |

| SDO-3 | 17 | Digital output | Serial communication: data output 3 |

| Thermal pad | Supply | Exposed thermal pad; connecting this pin to GND is recommended | |

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | |

|---|---|---|---|

| AVDD to GND | –0.3 | 2.1 | V |

| DVDD to GND | –0.3 | 2.1 | V |

| REFP to REFM | –0.3 | 5.5 | V |

| REFM to GND | –0.1 | 0.1 | V |

| Analog (AINP, AINM) to GND | –0.3 | REFP + 0.3 | V |

| Digital input (RST, CONVST, CS, SCLK, SDI) to GND | –0.3 | DVDD + 0.3 | V |

| Digital output (RVS, SDO-0, SDO-1, SDO-2, SDO-3) to GND | –0.3 | DVDD + 0.3 | V |

| Operating temperature, TA | –40 | 85 | °C |

| Storage temperature, Tstg | –65 | 150 | °C |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| AVDD | Analog supply voltage | 1.8 | V | ||

| DVDD | Digital supply voltage | 1.8 | V | ||

| REFP | Positive reference | 5 | V | ||

6.4 Thermal Information

| THERMAL METRIC(1) | ADS9110 | UNITS | |

|---|---|---|---|

| RGE (VQFN) | |||

| 24 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 31.9 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 29.9 | °C/W |

| RθJB | Junction-to-board thermal resistance | 8.9 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.3 | °C/W |

| ψJB | Junction-to-board characterization parameter | 8.9 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 2.0 | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

6.5 Electrical Characteristics

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V, VREF = 5 V, and fDATA = 2 MSPS, unless otherwise noted.All minimum and maximum specifications are for TA = –40°C to +85°C. All typical values are at TA = 25°C.

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| ANALOG INPUT | ||||||

| FSR | Full-scale input range (AINP – AINM)(1) |

–VREF | VREF | V | ||

| VIN | Absolute input voltage (AINP and AINM to REFGND) |

–0.1 | VREF + 0.1 | V | ||

| VCM | Common-mode voltage range (AINP + AINM) / 2 |

(VREF / 2) – 0.1 | VREF / 2 | (VREF / 2) + 0.1 | V | |

| CIN | Input capacitance | In sample mode | 60 | pF | ||

| In hold mode | 4 | |||||

| IIL | Input leakage current | ±1 | µA | |||

| VOLTAGE REFERENCE INPUT | ||||||

| VREF | Reference input voltage range | 2.5 | 5 | V | ||

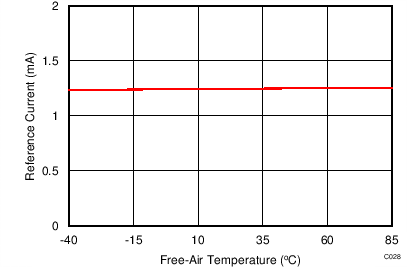

| IREF | Reference input current | Average current, VREF = 5 V, 2-kHz, full-scale input, throughput = 2 MSPS |

1.25 | mA | ||

| DC ACCURACY | ||||||

| Resolution | 18 | Bits | ||||

| NMC | No missing codes | 18 | Bits | |||

| INL | Integral nonlinearity | In LSBs | –1.5 | ±0.5(2) | 1.5 | LSB(3) |

| In ppm | –5.7 | ±2 | 5.7 | ppm | ||

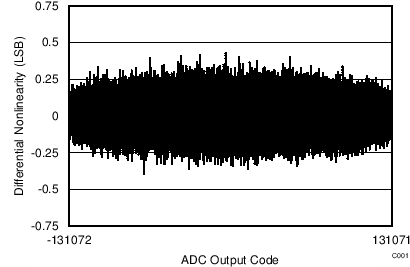

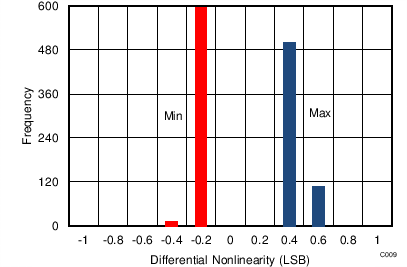

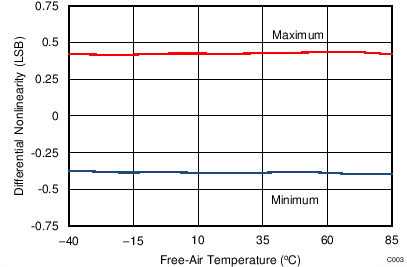

| DNL | Differential nonlinearity | –0.75 | ±0.4(2) | 0.75 | LSB(3) | |

| E(IO) | Input offset error | –1 | ±0.05(2) | 1 | mV | |

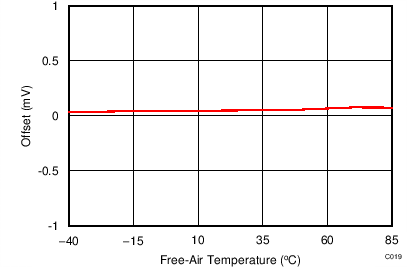

| dVOS/dT | Input offset thermal drift | 1 | μV/°C | |||

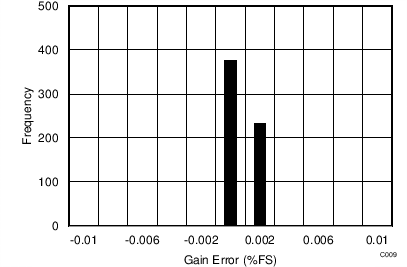

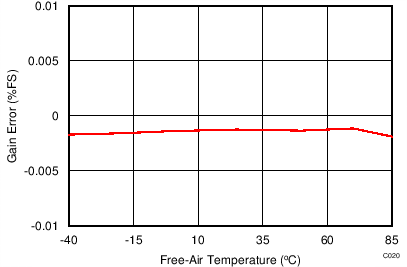

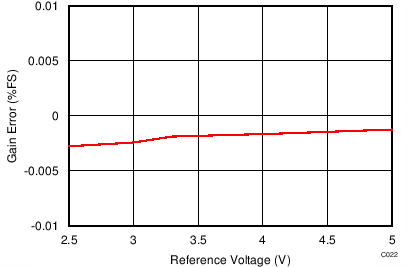

| GE | Gain error | –0.01 | ±0.005(2) | 0.01 | %FS | |

| GE/dT | Gain error thermal drift | 0.25 | ppm/°C | |||

| Transition noise | 0.9 | LSB(3) | ||||

| CMRR | Common-mode rejection ratio | At dc to 20 kHz | 80 | dB | ||

| AC ACCURACY(4) | ||||||

| SINAD | Signal-to-noise + distortion | fIN = 2 kHz | 98 | 99.9 | dB | |

| fIN = 100 kHz | 95.4 | |||||

| fIN = 500 kHz | 89 | |||||

| SNR | Signal-to-noise ratio | fIN = 2 kHz | 98.1 | 100 | dB | |

| fIN = 100 kHz | 95.5 | |||||

| fIN = 500 kHz | 89.3 | |||||

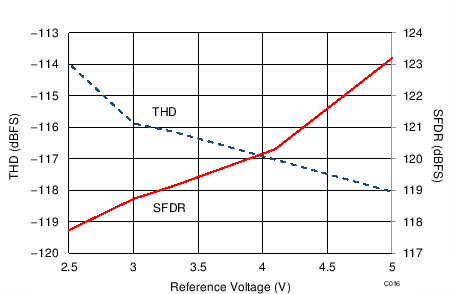

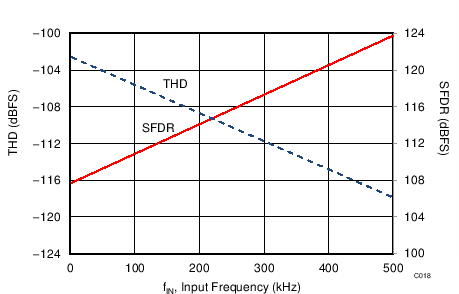

| THD | Total harmonic distortion(5) | fIN = 2 kHz | –118 | dB | ||

| fIN = 100 kHz | –111 | |||||

| fIN = 500 kHz | –101 | |||||

| SFDR | Spurious-free dynamic range | fIN = 2 kHz | 123 | dB | ||

| fIN = 100 kHz | 116 | |||||

| fIN = 500 kHz | 106 | |||||

| DIGITAL INPUTS(6) | ||||||

| VIH | High-level input voltage | 0.65 DVDD | DVDD + 0.3 | V | ||

| VIL | Low-level input voltage | –0.3 | 0.35 DVDD | V | ||

| DIGITAL OUTPUTS(6) | ||||||

| VOH | High-level output voltage | IOH = 2-mA source | DVDD – 0.45 | V | ||

| VOL | Low-level output voltage | IOH = 2-mA sink | 0.45 | V | ||

| POWER SUPPLY | ||||||

| AVDD | Analog supply voltage | 1.65 | 1.8 | 1.95 | V | |

| DVDD | Digital supply voltage | 1.65 | 1.8 | 1.95 | V | |

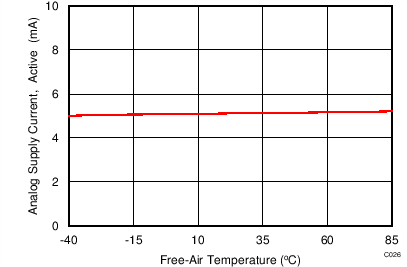

| IDD | AVDD supply current (AVDD = 1.8 V) |

Active, fastest throughput | 5 | 6.25 | mA | |

| Static, ACQ state | 3.7 | |||||

| Low-power, NAP mode | 500 | µA | ||||

| Power-down, PD state | 1 | |||||

| PD | AVDD power dissipation (AVDD = 1.8 V) |

Active, fastest throughput | 9 | 11.25 | mW | |

| Static, ACQ state | 6.6 | |||||

| Low-power, NAP mode | 900 | µW | ||||

| Power-down, PD state | 1.8 | |||||

| TEMPERATURE RANGE | ||||||

| TA | Operating free-air temperature | –40 | 85 | °C | ||

(1) Ideal input span, does not include gain or offset errors.

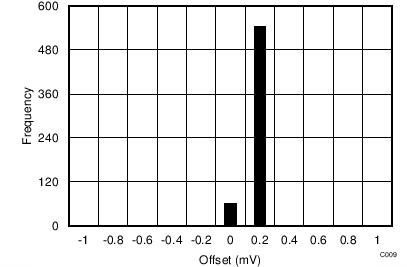

(2) See Figure 9, Figure 10, Figure 25, and Figure 26 for statistical distribution data for INL, DNL, offset, and gain error parameters.

(3) LSB = least-significant bit. 1 LSB at 18 bits is approximately 3.8 ppm.

(4) All specifications expressed in decibels (dB) refer to the full-scale input (FSR) and are tested with an input signal 0.1 dB below full-scale, unless otherwise specified.

(5) Calculated on the first nine harmonics of the input frequency.

(6) As per the JESD8-7A standard. Specified by design; not production tested.

6.6 Timing Requirements: Conversion Cycle

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V, VREF = 5 V, and fDATA = 2 MSPS, unless otherwise noted.All minimum and maximum specifications are for TA = –40°C to +85°C. All typical values are at TA = 25°C. See Figure 1.

| MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|

| TIMING REQUIREMENTS | |||||

| fcycle | Sampling frequency | 2 | MHz | ||

| tcycle | ADC cycle time period | 500 | ns | ||

| twh_CONVST | Pulse duration: CONVST high | 30 | ns | ||

| twl_CONVST | Pulse duration: CONVST low | 30 | ns | ||

| tacq | Acquisition time | 150 | ns | ||

| tqt_acq | Quiet acquisition time(1) | 25 | ns | ||

| td_cnvcap | Quiet aperture time(1) | 10 | ns | ||

| TIMING SPECIFICATIONS | |||||

| tconv | Conversion time | 300 | 340 | ns | |

(1) See Figure 48.

6.7 Timing Requirements: Asynchronous Reset, NAP, and PD

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V, VREF = 5 V, and fDATA = 2 MSPS, unless otherwise noted.All minimum and maximum specifications are for TA = –40°C to +85°C. All typical values are at TA = 25°C. See Figure 2 and Figure 3.

| MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|

| TIMING REQUIREMENTS | |||||

| twl_RST | Pulse duration: RST low | 100 | ns | ||

| TIMING SPECIFICATIONS | |||||

| td_rst | Delay time: RST rising to RVS rising | 1250 | µs | ||

| tnap_wkup | Wake-up time: NAP mode | 300 | ns | ||

| tPWRUP | Power-up time: PD mode | 250 | µs | ||

6.8 Timing Requirements: SPI-Compatible Serial Interface

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V, VREF = 5 V, and fDATA = 2 MSPS, unless otherwise noted.All minimum and maximum specifications are for TA = –40°C to +85°C. All typical values are at TA = 25°C. See Figure 4.

| MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| TIMING REQUIREMENTS | ||||||

| fCLK | Serial clock frequency | 75 | MHz | |||

| tCLK | Serial clock time period | 13.33 | ns | |||

| tph_CK | SCLK high time | 0.45 | 0.55 | tCLK | ||

| tpl_CK | SCLK low time | 0.45 | 0.55 | tCLK | ||

| tsu_CSCK | Setup time: CS falling to the first SCLK capture edge | 5 | ns | |||

| tsu_CKDI | Setup time: SDI data valid to the SCLK capture edge | 1.2 | ns | |||

| tht_CKDI | Hold time: SCLK capture edge to (previous) data valid on SDI | 0.65 | ns | |||

| tht_CKCS | Delay time: last SCLK falling to CS rising | 5 | ns | |||

| TIMING SPECIFICATIONS | ||||||

| tden_CSDO | Delay time: CS falling to data enable | 4.5 | ns | |||

| tdz_CSDO | Delay time: CS rising to SDO going to 3-state | 10 | ns | |||

| td_CKDO | Delay time: SCLK launch edge to (next) data valid on SDO | 6.5 | ns | |||

| td_CSRDY_f | Delay time: CS falling to RVS falling | 5 | ns | |||

| td_CSRDY_r | Delay time: CS rising to RVS rising |

After NOP operation | 10 | ns | ||

| After WR or RD operation | 70 | |||||

6.9 Timing Requirements: Source-Synchronous Serial Interface (External Clock)

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V, VREF = 5 V, and fDATA = 2 MSPS, unless otherwise noted.All minimum and maximum specifications are for TA = –40°C to +85°C. All typical values are at TA = 25°C. See Figure 5.

| MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|

| TIMING REQUIREMENTS | |||||

| fCLK | Serial clock frequency | 100 | MHz | ||

| tCLK | Serial clock time period | 10 | ns | ||

| TIMING SPECIFICATIONS(1) | |||||

| td_CKSTR_r | Delay time: SCLK launch edge to RVS rising | 8.5 | ns | ||

| td_CKSTR_f | Delay time: SCLK launch edge to RVS falling | 8.5 | ns | ||

| toff_STRDO_f | Time offset: RVS rising to (next) data valid on SDO | –0.5 | 0.5 | ns | |

| toff_STRDO_r | Time offset: RVS falling to (next) data valid on SDO | –0.5 | 0.5 | ns | |

(1) Other parameters are the same as the Timing Requirements: SPI-Compatible Serial Interface table.

6.10 Timing Requirements: Source-Synchronous Serial Interface (Internal Clock)

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V, VREF = 5 V, and fDATA = 2 MSPS, unless otherwise noted.All minimum and maximum specifications are for TA = –40°C to +85°C. All typical values are at TA = 25°C. See Figure 6.

| MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| TIMING SPECIFICATIONS(1) | ||||||

| td_CSSTR | Delay time: CS falling to RVS rising | 12 | 40 | ns | ||

| toff_STRDO_f | Time offset: RVS rising to (next) data valid on SDO | –0.5 | 0.5 | ns | ||

| toff_STRDO_r | Time offset: RVS falling to (next) data valid on SDO | –0.5 | 0.5 | ns | ||

| tSTR | Strobe output time period | INTCLK option | 9.9 | 11.1 | ns | |

| INTCLK / 2 option | 19.8 | 22.2 | ||||

| INTCLK / 4 option | 39.6 | 44.4 | ||||

| tph_STR | Strobe output high time | 0.45 | 0.55 | tSTR | ||

| tpl_STR | Strobe output low time | 0.45 | 0.55 | tSTR | ||

Figure 1. Conversion Cycle Timing Diagram

Figure 1. Conversion Cycle Timing Diagram

Figure 2. Asynchronous Reset Timing Diagram

Figure 2. Asynchronous Reset Timing Diagram

Figure 3. NAP Mode Timing Diagram

Figure 3. NAP Mode Timing Diagram

1. The SCLK polarity, launch edge, and capture edge depend on the SPI protocol selected.

Figure 4. SPI-Compatible Serial Interface Timing Diagram

Figure 5. Source-Synchronous Serial Interface Timing Diagram (External Clock)

Figure 5. Source-Synchronous Serial Interface Timing Diagram (External Clock)

Figure 6. Source-Synchronous Serial Interface Timing Diagram (Internal Clock)

Figure 6. Source-Synchronous Serial Interface Timing Diagram (Internal Clock)

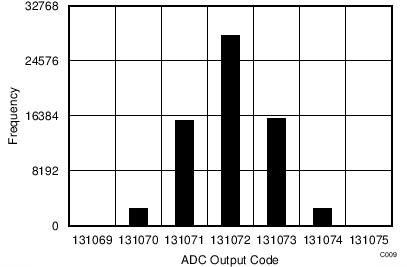

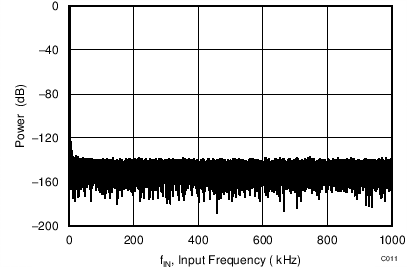

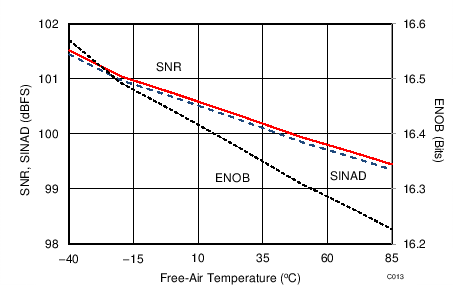

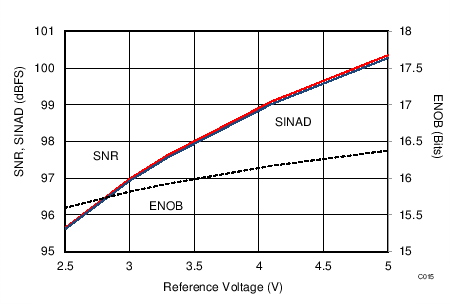

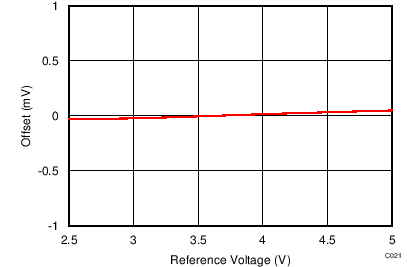

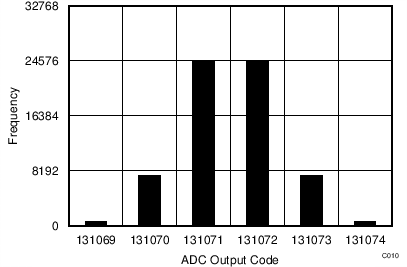

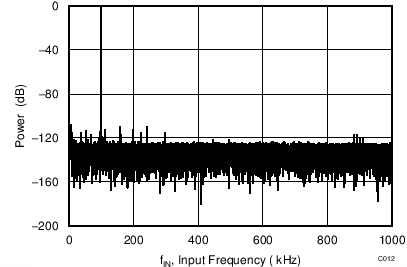

6.11 Typical Characteristics

At TA = 25°C, AVDD = 1.8 V, DVDD = 1.8 V, VREF = 5 V, and fSAMPLE = 2 MSPS, unless otherwise noted.

| Typical INL = ±0.5 LSB |

| 600 devices |

| VREF = 5 V |

| TA = 25°C |

| Standard deviation = 0.9 LSB |

| fIN = 2 kHz, SNR = 100 dB, THD = –120 dB |

| fIN = 2 kHz, VREF = 5 V |

| fIN = 2 kHz, TA = 25°C |

| VREF = 5 V, TA = 25°C |

| 600 devices |

| VREF = 5 V |

| TA = 25°C |

| 2 MSPS |

| 2 MSPS |

| Typical DNL = ±0.4 LSB |

| 600 devices |

| VREF = 5 V |

| TA = 25°C |

| Standard deviation = 0.9 LSB |

| fIN = 100 kHz, SNR = 97.5 dB, THD = –113 dB |

| fIN = 2 kHz, VREF = 5 V |

| fIN = 2 kHz, TA = 25°C |

| VREF = 5 V, TA = 25°C |

| 600 devices |

| VREF = 5 V |

| TA = 25°C |

| TA = 25°C |

| TA = 25°C |