ZHCSLE0B August 2021 – August 2023 JFE2140

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

- DSG|8

订购信息

3 说明

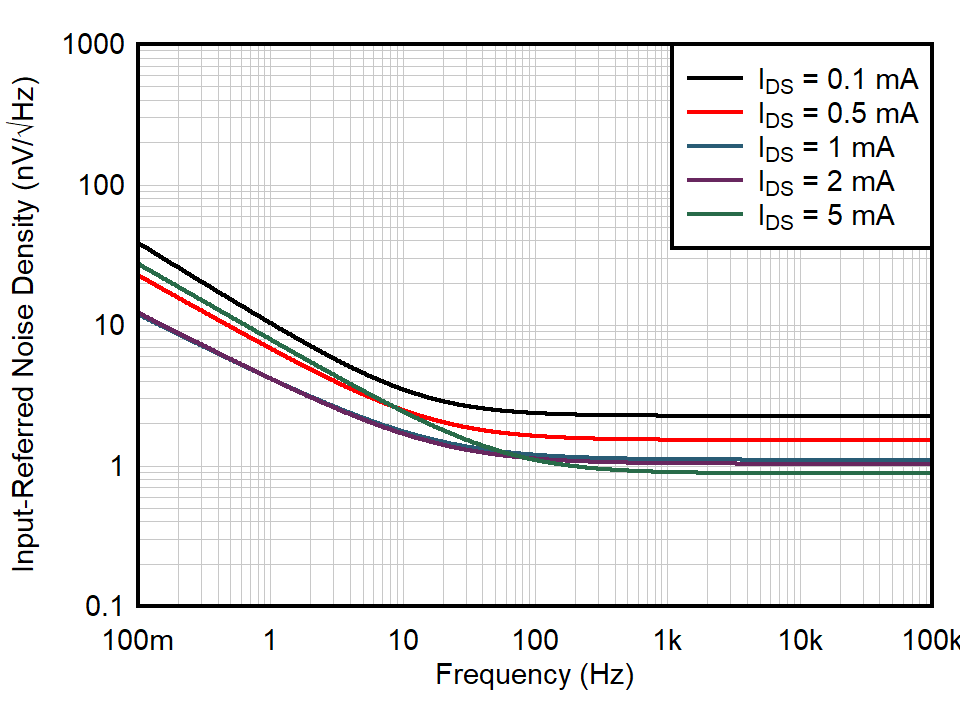

JFE2140 是使用米6体育平台手机版_好二三四 (TI) 现代高性能模拟双极工艺构建的 Burr-Brown™ 音频、匹配对分立式 JFET。JFE2140 具有以前较旧的分立式 JFET 技术所不具备的性能。JFE2140 在所有电流范围内均提供出色的噪声性能,静态电流可由用户设置,范围为 50 μA 至 20 mA。当偏置电流为 5 mA 时,该器件会产生 0.9 nV/√Hz 的输入参考噪声,从而以极高的输入阻抗 (>1TΩ) 提供超低噪声性能。此外,按照 ±4mV 测试 JFET 之间的匹配,可为差分对配置提供低失调电压和高 CMRR 性能。JFE2140 还具有连接到独立钳位节点的集成二极管,无需添加高泄漏、非线性外部二极管即可提供保护。

JFE2140 可承受 40V 的高漏源电压,以及低至 –40V 的栅源电压和栅漏电压。该器件额定工作温度范围为 –40°C 至 +125°C。

(1) 如需了解所有可用封装,请参阅数据表末尾的封装选项附录。

(2) 封装尺寸(长 x 宽)为标称值,并包括引脚(如适用)。

器件概要

| 参数 | 值 | |

|---|---|---|

| VGSS | 栅源击穿电压 | -40V |

| VDSS | 漏源击穿电压 | ±40V |

| CISS | 输入电容 | 13 pF |

| VGS1 – VGS2 | 差分栅源电压匹配(最大值) | ±4mV |

| TJ | 结温 | –40°C 至 +125°C |

| IDSS | 漏源饱和电流 | 18 mA |

简化版原理图

简化版原理图 超低输入电压噪声

超低输入电压噪声