-

TPS650860 Configurable Multirail PMU for Multicore Processors

- 1 Device Overview

- 2 Revision History

- 3 Pin Configuration and Functions

-

4 Specifications

- 4.1 Absolute Maximum Ratings

- 4.2 ESD Ratings

- 4.3 Recommended Operating Conditions

- 4.4 Thermal Information

- 4.5 Electrical Characteristics: Total Current Consumption

- 4.6 Electrical Characteristics: Reference and Monitoring System

- 4.7 Electrical Characteristics: Buck Controllers

- 4.8 Electrical Characteristics: Synchronous Buck Converters

- 4.9 Electrical Characteristics: LDOs

- 4.10 Electrical Characteristics: Load Switches

- 4.11 Digital Signals: I2C Interface

- 4.12 Digital Input Signals (CTLx)

- 4.13 Digital Output Signals (IRQB, GPOx)

- 4.14 Timing Requirements

- 4.15 Switching Characteristics

- 4.16 Typical Characteristics

-

5 Detailed Description

- 5.1 Overview

- 5.2 Functional Block Diagram

- 5.3 SMPS Voltage Regulators

- 5.4 LDOs and Load Switches

- 5.5 Power Goods (PGOOD or PG) and GPOs

- 5.6 Power Sequencing and VR Control

- 5.7 Device Functional Modes

- 5.8 I2C Interface

- 5.9

Register Maps

- 5.9.1 Register Map Summary

- 5.9.2 DEVICEID: PMIC Device and Revision ID Register (offset = 1h) [reset = OTP-Programmable]

- 5.9.3 IRQ: PMIC Interrupt Register (offset = 2h) [reset = 0000 0000]

- 5.9.4 IRQ_MASK: PMIC Interrupt Mask Register (offset = 3h) [reset = 1111 1111]

- 5.9.5 PMICSTAT: PMIC Status Register (offset = 4h) [reset = 0000 0000]

- 5.9.6 SHUTDNSRC: PMIC Shut-Down Event Register (offset = 5h) [reset = 0000 0000]

- 5.9.7 BUCK1CTRL: BUCK1 Control Register (offset = 20h) [reset = OTP-Programmable]

- 5.9.8 BUCK2CTRL: BUCK2 Control Register (offset = 21h) [reset = OTP-Programmable]

- 5.9.9 BUCK3DECAY: BUCK3 Decay Control Register (offset = 22h) [reset = OTP-Programmable]

- 5.9.10 BUCK3VID: BUCK3 VID Register (offset = 23h) [reset = OTP-Programmable]

- 5.9.11 BUCK3SLPCTRL: BUCK3 Sleep Control VID Register (offset = 24h) [reset = OTP-Programmable]

- 5.9.12 BUCK4CTRL: BUCK4 Control Register (offset = 25h) [reset = OTP-Programmable]

- 5.9.13 BUCK5CTRL: BUCK5 Control Register (offset = 26h) [reset = OTP-Programmable]

- 5.9.14 BUCK6CTRL: BUCK6 Control Register (offset = 27h) [reset = OTP-Programmable]

- 5.9.15 LDOA2CTRL: LDOA2 Control Register (offset = 28h) [reset = OTP-Programmable]

- 5.9.16 LDOA3CTRL: LDOA3 Control Register (offset = 29h) [reset = OTP-Programmable]

- 5.9.17 DISCHCTRL1: Discharge Control1 Register (offset = 40h) [reset = OTP-Programmable]

- 5.9.18 DISCHCTRL2: Discharge Control2 Register (offset = 41h) [reset = OTP-Programmable]

- 5.9.19 DISCHCTRL3: Discharge Control3 Register (offset = 42h) [reset = OTP-Programmable]

- 5.9.20 PG_DELAY1: Power Good Delay1 Register (offset = 43h) [reset = OTP-Programmable]

- 5.9.21 FORCESHUTDN: Force Emergency Shutdown Control Register (offset = 91h) [reset = 0000 0000]

- 5.9.22 BUCK1SLPCTRL: BUCK1 Sleep Control Register (offset = 92h) [reset = OTP-Programmable]

- 5.9.23 BUCK2SLPCTRL: BUCK2 Sleep Control Register (offset = 93h) [reset = OTP-Programmable]

- 5.9.24 BUCK4VID: BUCK4 VID Register (offset = 94h) [reset = OTP-Programmable]

- 5.9.25 BUCK4SLPVID: BUCK4 Sleep VID Register (offset = 95h) [reset = OTP-Programmable]

- 5.9.26 BUCK5VID: BUCK5 VID Register (offset = 96h) [reset = OTP-Programmable]

- 5.9.27 BUCK5SLPVID: BUCK5 Sleep VID Register (offset = 97h) [reset = OTP-Programmable]

- 5.9.28 BUCK6VID: BUCK6 VID Register (offset = 98h) [reset = OTP-Programmable]

- 5.9.29 BUCK6SLPVID: BUCK6 Sleep VID Register (offset = 99h) [reset = OTP-Programmable]

- 5.9.30 LDOA2VID: LDOA2 VID Register (offset = 9Ah) [reset = OTP-Programmable]

- 5.9.31 LDOA3VID: LDOA3 VID Register (offset = 9Bh) [reset = OTP-Programmable]

- 5.9.32 BUCK123CTRL: BUCK1-3 Control Register (offset = 9Ch) [reset = OTP-Programmable]

- 5.9.33 PG_DELAY2: Power Good Delay2 Register (offset = 9Dh) [reset = OTP-Programmable]

- 5.9.34 SWVTT_DIS: SWVTT Disable Register (offset = 9Fh) [reset = OTP-Programmable]

- 5.9.35 I2C_RAIL_EN1: VR Pin Enable Override1 Register (offset = A0h) [reset = OTP-Programmable]

- 5.9.36 I2C_RAIL_EN2/GPOCTRL: VR Pin Enable Override2/GPO Control Register (offset = A1h) [reset = OTP-Programmable]

- 5.9.37 PWR_FAULT_MASK1: VR Power Fault Mask1 Register (offset = A2h) [reset = OTP-Programmable]

- 5.9.38 PWR_FAULT_MASK2: VR Power Fault Mask2 Register (offset = A3h) [reset = OTP-Programmable]

- 5.9.39 GPO1PG_CTRL1: GPO1 PG Control1 Register (offset = A4h) [reset = OTP-Programmable]

- 5.9.40 GPO1PG_CTRL2: GPO1 PG Control2 Register (offset = A5h) [reset = OTP-Programmable]

- 5.9.41 GPO4PG_CTRL1: GPO4 PG Control1 Register (offset = A6h) [reset = OTP-Programmable]

- 5.9.42 GPO4PG_CTRL2: GPO4 PG Control2 Register (offset = A7h) [reset = OTP-Programmable]

- 5.9.43 GPO2PG_CTRL1: GPO2 PG Control1 Register (offset = A8h) [reset = OTP-Programmable]

- 5.9.44 GPO2PG_CTRL2: GPO2 PG Control2 Register (offset = A9h) [reset = OTP-Programmable]

- 5.9.45 GPO3PG_CTRL1: GPO3 PG Control1 Register (offset = AAh) [reset = OTP-Programmable]

- 5.9.46 GPO3PG_CTRL2: GPO3 PG Control2 Register (offset = ABh) [reset = OTP-Programmable]

- 5.9.47 MISCSYSPG Register (offset = ACh) [reset = OTP-Programmable]

- 5.9.48 LDOA1CTRL: LDOA1 Control Register (offset = AEh) [reset = OTP-Programmable]

- 5.9.49 PG_STATUS1: Power Good Status1 Register (offset = B0h) [reset = 0000 0000]

- 5.9.50 PG_STATUS2: Power Good Status2 Register (offset = B1h) [reset = 0000 0000]

- 5.9.51 PWR_FAULT_STATUS1: Power Fault Status1 Register (offset = B2h) [reset = 0000 0000]

- 5.9.52 PWR_FAULT_STATUS2: Power Fault Status2 Register (offset = B3h) [reset = 0000 0000]

- 5.9.53 TEMPCRIT: Temperature Fault Status Register (offset = B4h) [reset = 0000 0000]

- 5.9.54 TEMPHOT: Temperature Hot Status Register (offset = B5h) [reset = 0000 0000]

- 5.9.55 OC_STATUS: Overcurrent Fault Status Register (offset = B6h) [reset = 0000 0000]

- 6 Application and Implementation

- 7 Power Supply Coupling and Bulk Capacitors

- 8 Layout

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

TPS650860 Configurable Multirail PMU for Multicore Processors

1 Device Overview

1.1 Features

- Wide VIN Range From 5.6 V to 21 V

- Three Variable-Output Voltage Synchronous

Step-Down Controllers With DCAP2™ Topology- Scalable Output Current Using External FETs With Selectable Current Limit

- I2C DVS Control From 0.41 V to 1.67 V in 10-mV Steps or 1 V to 3.575 V in 25-mV Steps

- Three Variable-Output Voltage Synchronous Step-Down Converters With DCS-Control Topology

- VIN Range From 4.5 V to 5.5 V

- Up to 3 A of Output Current

- I2C DVS Control From 0.41 V to 1.67 V in 10-mV Steps or 0.425 V to 3.575 V in 25-mV Steps

- Three LDO Regulators With Adjustable Output Voltage

- LDOA1: I2C-Selectable Output Voltage From 1.35 V to 3.3 V for up to 200 mA of Output Current

- LDOA2 and LDOA3: I2C-Selectable Output Voltage From 0.7 V to 1.5 V for up to 600 mA of Output Current

- VTT LDO for DDR Memory Termination

- Three Load Switches With Slew Rate Control

- Up to 300 mA of Output Current With Voltage Drop Less Than 1.5% of Nominal Input Voltage

- RDSON < 96 mΩ at Input Voltage of 1.8 V

- 5-V Fixed-Output Voltage LDO (LDO5)

- Power Supply for Gate Drivers of SMPS and for LDOA1

- Automatic Switch to External 5-V Buck for Higher Efficiency

- Built-in Flexibility and Configurability by Factory OTP Programming

- Six GPI Pins Configurable to Enable (CTL1 to CTL6) or Sleep Mode Entry (CTL3 and CTL6) of Any Selected Rails

- Four GPO Pins Configurable to Power Good of Any Selected Rails

- Open-Drain Interrupt Output Pin

- I2C Interface Supports:

- Standard Mode (100 kHz)

- Fast Mode (400 kHz)

- Fast Mode Plus (1 MHz)

1.2 Applications

- Residential Gateway

- POS Terminals

- Test and Measurement

- Programmable Logic Controllers

- Embedded PCs

- Human to Machine Interfaces

1.3 Description

The TPS650860 device is a single-chip power-management IC designed for multicore processors, FPGAs, and other System-on-Chips (SoCs). The TPS650860 offers an input range of 5.6 V to 21 V, enabling a wide range of applications. The device is well suited for NVDC and non-NVDC power architecture using 2S, 3S, or 4S Li-Ion battery packs. See the Application Section for 5-V input supplies. The D-CAP2™ and DCS-Control high-frequency voltage regulators use small inductors and capacitors to achieve a small solution size. The D-CAP2 and DCS-Control topologies have excellent transient response performance, which is great for processor core and system memory rails that have fast load switching. An I2C interface allows simple control either by an embedded controller (EC) or by an SoC. The PMIC comes in an

8-mm × 8-mm, single-row VQFN package with thermal pad for good thermal dissipation and ease of board routing.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| TPS650860 | VQFN (64) | 8.00 mm × 8.00 mm |

1.4 Functional Block Diagram

2 Revision History

Changes from * Revision (March 2015) to A Revision

- Changed device status from: PRODUCT PREVIEW to: PRODUCTION DATA Go

3 Pin Configuration and Functions

Pin Functions

| NO. | NAME | I/O | DESCRIPTION |

|---|---|---|---|

| SMPS REGULATORS | |||

| 1 | FBGND2 | I | Remote negative feedback sense for BUCK2 controller. Connect to negative terminal of output capacitor. |

| 2 | FBVOUT2 | I | Remote positive feedback sense for BUCK2 controller. Connect to positive terminal of output capacitor. |

| 3 | DRVH2 | O | High-side gate driver output for BUCK2 controller. |

| 4 | SW2 | I | Switch node connection for BUCK2 controller. |

| 5 | BOOT2 | I | Bootstrap pin for BUCK2 controller. Connect a 100-nF ceramic capacitor between this pin and SW2 pin. |

| 6 | PGNDSNS2 | I | Power GND connection for BUCK2. Connect to ground terminal of external low-side FET. |

| 7 | DRVL2 | O | Low-side gate driver output for BUCK2 controller. |

| 8 | DRV5V_2_A1 | I | 5-V supply to BUCK2 gate driver and LDOA1. Bypass to ground with a 2.2-µF (TYP) ceramic capacitor. Shorted on board to LDO5P0 pin typically. |

| 10 | LX3 | O | Switch node connection for BUCK3 converter. |

| 11 | PVIN3 | I | Power input to BUCK3 converter. Bypass to ground with a 10-µF (TYP) ceramic capacitor. |

| 12 | FB3 | I | Remote feedback sense for BUCK3 converter. Connect to positive terminal of output capacitor. |

| 20 | LX5 | O | Switch node connection for BUCK5 converter. |

| 21 | PVIN5 | I | Power input to BUCK5 converter. Bypass to ground with a 10-µF (TYP) ceramic capacitor. |

| 22 | FB5 | I | Remote feedback sense for BUCK5 converter. Connect to positive terminal of output capacitor. |

| 23 | FB4 | I | Remote feedback sense for BUCK4 converter. Connect to positive terminal of output capacitor. |

| 24 | PVIN4 | I | Power input to BUCK4 converter. Bypass to ground with a 10-µF (TYP) ceramic capacitor. |

| 25 | LX4 | O | Switch node connection for BUCK4 converter. |

| 29 | FBVOUT1 | I | Remote feedback sense for BUCK1 controller. Connect to positive terminal of output capacitor. |

| 30 | ILIM1 | I | Current limit set pin for BUCK1 controller. Fit a resistor from this pin to ground to set current limit of external low-side FET. |

| 33 | DRVH1 | O | High-side gate driver output for BUCK1 controller. |

| 34 | SW1 | I | Switch node connection for BUCK1 controller. |

| 35 | BOOT1 | I | Bootstrap pin for BUCK1 controller. Connect a 100-nF ceramic capacitor between this pin and SW1 pin. |

| 36 | PGNDSNS1 | I | Power GND connection for BUCK1. Connect to ground terminal of external low-side FET. |

| 37 | DRVL1 | O | Low-side gate driver output for BUCK1 controller. |

| 38 | DRV5V_1_6 | I | 5-V supply to BUCK1 and BUCK6 gate drivers. Bypass to ground with a 2.2-µF (TYP) ceramic capacitor. Shorted on board to LDO5P0 pin typically. |

| 39 | DRVL6 | O | Low-side gate driver output for BUCK6 controller. |

| 40 | PGNDSNS6 | I | Power GND connection for BUCK6. Connect to ground terminal of external low-side FET. |

| 41 | BOOT6 | I | Bootstrap pin for BUCK6 controller. Connect a 100-nF ceramic capacitor between this pin and SW6 pin. |

| 42 | SW6 | I | Switch node connection for BUCK6 controller. |

| SMPS REGULATORS (continued) | |||

| 43 | DRVH6 | O | High-side gate driver output for BUCK6 controller. |

| 44 | FBVOUT6 | I | Remote feedback sense for BUCK6 controller. Connect to positive terminal of output capacitor. |

| 45 | ILIM6 | I | Current limit set pin for BUCK6 controller. Fit a resistor from this pin to ground to set current limit of external low-side FET. |

| 64 | ILIM2 | I | Current limit set pin for BUCK2 controller. Fit a resistor from this pin to ground to set current limit of external low-side FET. |

| LDO and LOAD SWITCHES | |||

| 9 | LDOA1 | O | LDOA1 output. Bypass to ground with a 4.7-µF (TYP) ceramic capacitor. Leave floating when not in use. |

| 17 | SWB1 | O | Output of load switch B1. Bypass to ground with a 0.1-µF (TYP) ceramic capacitor. Leave floating when not in use. |

| 18 | PVINSWB1_B2 | I | Power supply to load switch B1 and B2. Bypass to ground with a 1-µF (TYP) ceramic capacitor to improve transient performance. Connect to ground when not in use. |

| 19 | SWB2 | O | Output of load switch B2. Bypass to ground with a 0.1-µF (TYP) ceramic capacitor. Leave floating when not in use. |

| 31 | SWA1 | O | Output of load switch A1. Bypass to ground with a 0.1-µF (TYP) ceramic capacitor. Leave floating when not in use. |

| 32 | PVINSWA1 | I | Power supply to load switch A1. Bypass to ground with a 1-µF (TYP) ceramic capacitor to improve transient performance. Connect to ground when not in use. |

| 46 | PVINVTT | I | Power supply to VTT LDO. Bypass to ground with a 10-µF (MIN) ceramic capacitor. |

| 47 | VTT | O | Output of load VTT LDO. Bypass to ground with 2× 22-µF (MIN) ceramic capacitors. |

| 48 | VTTFB | I | Remote feedback sense for VTT LDO. Connect to positive terminal of output capacitor. |

| 49 | LDOA3 | O | Output of LDOA3. Bypass to ground with a 4.7-µF (TYP) ceramic capacitor. Leave floating when not in use. |

| 50 | PVINLDOA2_A3 | I | Power supply to LDOA2 and LDOA3. Bypass to ground with a 4.7-µF (TYP) ceramic capacitor. Connect to ground when not in use. |

| 51 | LDOA2 | O | Output of LDOA2. Bypass to ground with a 4.7-µF (TYP) ceramic capacitor. Leave floating when not in use. |

| 54 | LDO3P3 | O | Output of 3.3-V internal LDO. Bypass to ground with a 4.7-µF (TYP) ceramic capacitor. |

| 56 | LDO5P0 | O | Output of 5-V internal LDO or an internal switch that connects this pin to V5ANA. Bypass to ground with a 4.7-µF (TYP) ceramic capacitor. |

| 57 | V5ANA | I | External 5-V supply input to internal load switch that connects this pin to LDO5P0 pin. Bypass this pin with an optional ceramic capacitor to improve transient performance. |

| INTERFACE | |||

| 13 | CTL1 | I | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin. |

| 14 | CTL6/SLPENB2 | I | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin. Alternatively, when configured to active-low sleep enable, a group of VRs chosen can be entered into (L) or out of (H) sleep state where their output voltages may be different from those in normal state. |

| 15 | IRQB | O | Open-drain output interrupt pin. Refer to Section 5.9.3 for definitions. |

| 16 | GPO1 | O | General purpose output that can be configured to either open-drain or push-pull arrangement. Regardless of the configuration, the pin can be programmed either to reflect power good status of VRs of any choice or to be controlled by an I2C register bit by the user, which then can be used as an enable signal to an external VR. |

| 26 | GPO2 | O | General purpose output that can be configured to either open-drain or push-pull arrangement. Regardless of the configuration, the pin can be programmed either to reflect power good status of VRs of any choice or to be controlled by an I2C register bit by the user, which then can be used as an enable signal to an external VR. |

| 27 | GPO3 | O | General purpose output that can be configured to either open-drain or push-pull arrangement. Regardless of the configuration, the pin can be programmed either to reflect power good status of VRs of any choice or to be controlled by an I2C register bit by the user, which then can be used as an enable signal to an external VR. |

| 28 | GPO4 | O | Open-drain output that can be configured to reflect power good status of VRs of any choice or to be controlled by an I2C register bit by the user, which then can be used as an enable signal to an external VR. |

| 58 | CLK | I | I2C clock |

| 59 | DATA | I/O | I2C data |

| 60 | CTL2 | I | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin. |

| 61 | CTL3/SLPENB1 | I | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin. Alternatively, when configured to active-low sleep enable, a group of VRs chosen can be entered into (L) or out of (H) sleep state where their output voltages may be different from those in normal state. |

| 62 | CTL4 | I | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin. |

| 63 | CTL5 | I | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin. |

| REFERENCE | |||

| 53 | VREF | O | Band-gap reference output. Stabilize it by connecting a 100-nF (TYP) ceramic capacitor between this pin and quiet ground. |

| 52 | AGND | — | Analog ground. Do not connect to the thermal pad ground on top layer. Connect to ground of VREF capacitor. |

| 55 | VSYS | I | System voltage detection and input to internal LDOs (3.3 V and 5 V). Bypass to ground with a 1-µF (TYP) ceramic capacitor. |

| THERMAL PAD | |||

| Thermal pad | — | Connect to PCB ground plane using multiple vias for good thermal and electrical performance. | |

4 Specifications

4.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| ANALOG | ||||

| VSYS | Input voltage from battery | –0.3 | 28 | V |

| PVIN3, PVIN4, PVIN5, LDO5P0, DRV5V_1_6, DRV5V_2_A1, DRVL1, DRVL2, DRVL6 | –0.3 | 7 | V | |

| V5ANA | –0.3 | 6 | V | |

| PGNDSNS1, PGNDSNS2, PGNDSNS6, AGND, FBGND2 | –0.3 | 0.3 | V | |

| DRVH1, DRVH2, DRVH6, BOOT1, BOOT2, BOOT6 | –0.3 | 34 | V | |

| SW1, SW2, SW6 | –2(2) | 28 | V | |

| LX3, LX4, LX5 | –1(3) | 7 | V | |

| BOOTx to SWx | Differential voltage | –0.3 | 5.5 | V |

| VREF, LDO3P3, FBVOUT1, FBVOUT2, FBVOUT6, FB3, FB4, FB5, ILIM1, ILIM2, ILIM6, PVINVTT, VTT, VTTFB, PVINSWA1, SWA1, PVINSWB1_B2, SWB1, SWB2, LDOA1 | –0.3 | 3.6 | V | |

| PVINLDOA2_A3, LDOA2, LDOA3 | –0.3 | 3.3 | V | |

| DIGITAL IOs | ||||

| DATA, CLK, GPO1-GPO3 | –0.3 | 3.6 | V | |

| CTL1-CTL6, GPO4, IRQB | –0.3 | 7 | V | |

| Tstg | Storage temperature | –40 | 150 | °C |

4.2 ESD Ratings

| VALUE | UNIT | ||||

|---|---|---|---|---|---|

| VESD | Electrostatic discharge (ESD) performance | Human Body Model (HBM), per ANSI/ESDA/JEDEC JS001(1) |

±1000 | V | |

| Charged Device Model (CDM), per JESD22-C101(2) |

All pins | ±250 | V | ||

4.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| ANALOG | |||||

| VSYS | 5.6 | 13 | 21 | V | |

| VREF | –0.3 | 1.3 | V | ||

| PVIN3, PVIN4, PVIN5, LDO5P0, V5ANA, DRV5V_1_6, DRV5V_2_A1 | –0.3 | 5 | 5.5 | V | |

| PGNDSNS1, PGNDSNS2, PGNDSNS6, AGND, FBGND2 | –0.3 | 0.3 | V | ||

| DRVH1, DRVH2, DRVH6, BOOT1, BOOT2, BOOT6 | –0.3 | 26.5 | v | ||

| DRVL1, DRVL2, DRVL6 | –0.3 | 5.5 | V | ||

| SW1, SW2, SW6 | –1 | 21 | V | ||

| LX3, LX4, LX5 | –1 | 5.5 | V | ||

| FBVOUT1, FBVOUT2, FBVOUT6, FB3, FB4, FB5 | –0.3 | 3.6 | V | ||

| LDO3P3, ILIM1, ILIM2, ILIM6, LDOA1 | –0.3 | 3.3 | V | ||

| PVINVTT | –0.3 | 1.2 / 1.35 | FBVOUT6 | V | |

| VTT, VTTFB | –0.3 | FBVOUT6 / 2 | V | ||

| PVINSWA1, SWA1 | –0.3 | 3.3 | 3.6 | V | |

| PVINSWB1_B2, PVINLDOA2_A3, SWB1, SWB2 | –0.3 | 1.8 | V | ||

| LDOA2, LDOA3 | –0.3 | 1.5 | V | ||

| DIGITAL IOs | |||||

| DATA, CLK, CTL1–CTL6, GPO1–GPO4, IRQB | –0.3 | 3.3 | V | ||

| CHIP | |||||

| TA | Operating ambient temperature range | –40 | 27 | 85 | °C |

| TJ | Operating junction temperature range | –40 | 27 | 125 | °C |

4.4 Thermal Information

| THERMAL METRIC(1) | TPS650860 | UNIT | |

|---|---|---|---|

| RSK (VQFN) | |||

| 64 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 25.8 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 11.3 | °C/W |

| RθJB | Junction-to-board thermal resistance | 4.4 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.2 | °C/W |

| ψJB | Junction-to-board characterization parameter | 4.4 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 0.7 | °C/W |

4.5 Electrical Characteristics: Total Current Consumption

over recommended free-air temperature range and over recommended input voltage range (typical values are at TA = 25°C) (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| ISD | PMIC shutdown current that includes IQ for References, LDO5, LDO3P3, and digital core | VSYS = 13 V, all functional output rails are disabled | 65 | µA | ||

4.6 Electrical Characteristics: Reference and Monitoring System

over recommended free-air temperature range and over recommended input voltage range (typical values are at TA = 25°C) (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| REFERENCE | ||||||

| VREF | Bandgap reference Voltage | 1.25 | V | |||

| Accuracy | –0.5% | 0.5% | ||||

| CVREF | Bandgap output capacitor | 0.047 | 0.1 | 0.22 | µF | |

| VSYS_UVLO_5V | VSYS UVLO threshold for LDO5 | VSYS falling | 5.24 | 5.4 | 5.56 | V |

| VSYS_UVLO_5V_HYS | VSYS UVLO threshold hysteresis for LDO5 | VSYS rising above VSYS_UVLO_5V |

200 | mV | ||

| VSYS_UVLO_3V | VSYS UVLO threshold for LDO3P3 | VSYS falling | 3.45 | 3.6 | 3.75 | V |

| VSYS_UVLO_3V_HYS | VSYS UVLO threshold hysteresis for LDO3P3 | VSYS rising above VSYS_UVLO_3V |

150 | mV | ||

| TCRIT | Critical threshold of die temperature | TJ rising | 130 | 145 | 160 | °C |

| TCRIT_HYS | Hysteresis of TCRIT | TJ falling | 10 | °C | ||

| THOT | Hot threshold of die temperature | TJ rising | 110 | 115 | 120 | °C |

| THOT_HYS | Hysteresis of THOT | TJ falling | 10 | °C | ||

| LDO5 | ||||||

| VIN | Input voltage at VSYS pin | 5.6 | 13 | 21 | V | |

| VOUT | DC output voltage | IOUT = 10 mA | 4.9 | 5 | 5.1 | V |

| IOUT | DC output current | 100 | 180 | mA | ||

| IOCP | Overcurrent protection | Measured with output shorted to ground | 200 | mA | ||

| VTH_PG | Power Good assertion threshold in percentage of target VOUT | VOUT rising | 94% | |||

| VTH_PG_HYS | Power Good deassertion hysteresis | VOUT rising or falling | 4% | |||

| IQ | Quiescent current | VIN = 13 V, IOUT = 0 A | 20 | µA | ||

| COUT | External output capacitance | 2.7 | 4.7 | 10 | µF | |

| V5ANA-to-LDO5P0 LOAD SWITCH | ||||||

| RDSON | On resistance | VIN = 5 V, measured from V5ANA pin to LDO5P0 pin at IOUT = 200 mA | 1 | Ω | ||

| VTH_PG | Power Good threshold for external 5-V supply | VV5ANA rising | 4.7 | V | ||

| VTH_HYS_PG | Power Good threshold hysteresis for external 5-V supply | VV5ANA falling | 100 | mV | ||

| ILKG | Leakage current | Switch disabled, VV5ANA = 5 V, VLDO5 = 0 V |

10 | µA | ||

| LDO3P3 | ||||||

| VIN | Input voltage at VSYS pin | 5.6 | 13 | 21 | V | |

| VOUT | DC output voltage | IOUT = 10 mA | 3.3 | V | ||

| Accuracy | VIN = 13 V, IOUT = 10 mA |

–3% | 3% | |||

| IOUT | DC output current | 40 | mA | |||

| IOCP | Overcurrent protection | Measured with output shorted to ground | 70 | mA | ||

| VTH_PG | Power Good assertion threshold in percentage of target VOUT | VOUT rising | 92% | |||

| VTH_PG_HYS | Power Good deassertion hysteresis | VOUT falling | 3% | |||

| IQ | Quiescent current | VIN = 13 V, IOUT = 0 A |

20 | µA | ||

| COUT | External output capacitance | 2.2 | 4.7 | 10 | µF | |

4.7 Electrical Characteristics: Buck Controllers

over recommended input voltage range, TA = –40°C to 85°C and TA = 25°C for typical values (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| BUCK1, BUCK2, BUCK6 | |||||||

| VIN | Power input voltage for external HSD FET | 5.6 | 13 | 21 | V | ||

| VOUT | DC output voltage VID range and options | VID step size = 10 mV, BUCKx_VID[6:0] progresses from 0000001 to 1111111 | 0.41 | 1.67 | V | ||

| VID step size = 25 mV, BUCKx_VID[6:0] progresses from 0000001 to 1111111 | 1(1) | 3.575 | V | ||||

| BUCK1 output voltage | Set by BUCK1_VID[6:0], 10 mV step size selected | 1.05 | V | ||||

| BUCK2 output voltage | Set by BUCK2_VID[6:0], 25 mV step size selected | 3.3 | V | ||||

| BUCK6 output voltage | Set by BUCK6_VID[6:0], 10 mV step size selected | 1.5 | V | ||||

| DC output voltage accuracy | VOUT = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V, IOUT = 100 mA to 7 A |

–2% | 2% | ||||

| Total output voltage accuracy (DC + ripple) in DCM | IOUT = 10 mA, VOUT ≤ 1 V | –30 | 40 | mV | |||

| SR(VOUT) | Output DVS slew rate | 2.5 | 3.125 | mV/µs | |||

| ILIM_LSD | Low-side output valley current limit accuracy (programmed by external resistor RLIM) | –15% | 15% | ||||

| ILIMREF | Source current out of ILIM1 pin | T = 25°C | 45 | 50 | 55 | µA | |

| VLIM | Voltage at ILIM1 pin | VLIM = RLIM × ILIMREF | 0.2 | 2.25 | V | ||

| ΔVOUT/ΔVIN | Line regulation | VOUT = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V, IOUT = 7 A |

–0.5% | 0.5% | |||

| ΔVOUT/ΔIOUT | Load regulation | VIN = 13 V, VOUT = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V, IOUT = 0 A to 7 A, referenced to VOUT at IOUT = IOUT_MAX |

0% | 1% | |||

| VTH_PG | Power Good deassertion threshold in percentage of target VOUT | VOUT rising | 105.5% | 108% | 110.5% | ||

| VOUT falling | 89.5% | 92% | 94.5% | ||||

| RDSON_DRVH | Driver DRVH resistance | Source, IDRVH = –50 mA | 3 | Ω | |||

| Sink, IDRVH = 50 mA | 2 | Ω | |||||

| RDSON_DRVL | Driver DRVL resistance | Source, IDRVL = –50 mA | 3 | Ω | |||

| Sink, IDRVL = 50 mA | 0.4 | Ω | |||||

| RDIS | Output auto-discharge resistance | BUCK1_DIS[1:0] = 01 | 100 | Ω | |||

| BUCK1_DIS[1:0] = 10 | 200 | Ω | |||||

| BUCK1_DIS[1:0] = 11 | 500 | Ω | |||||

| CBOOT | Bootstrap capacitance | 100 | nF | ||||

| RON_BOOT | Bootstrap switch ON resistance | 20 | Ω | ||||

4.8 Electrical Characteristics: Synchronous Buck Converters

over recommended input voltage range, TA = –40°C to 85°C and TA = 25°C for typical values (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| BUCK3, BUCK4, BUCK5 | ||||||

| VIN | Power input voltage | 4.5 | 5 | 5.5 | V | |

| VOUT | DC output voltage VID range and options | VID step size = 10 mV, BUCKx_VID[6:0] progresses from 0000001 to 1111111 | 0.41 | 1.67 | V | |

| VID step size = 12.5 mV, BUCKx_VID[6:0] progresses from 0000001 to 1111111 | 0.4125 | 1.9875 | ||||

| VID step size = 25 mV, BUCKx_VID[6:0] progresses from 0000001 to 1111111 | 0.425 | 3.575 | ||||

| BUCK3 output voltage | Set by BUCK3_VID[6:0], 25-mV step size selected | 1.05 | V | |||

| BUCK4 output voltage | Set by BUCK4_VID[6:0], 25-mV step size selected | 3.3 | ||||

| BUCK5 output voltage | Set by BUCK5_VID[6:0], 25-mV step size selected | 1.5 | ||||

| DC output voltage accuracy | VOUT = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V, IOUT = 1.5 A |

–2% | 2% | |||

| VOUT = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V, IOUT = 100 mA |

–2.5% | 2.5% | ||||

| Total output voltage accuracy (DC + ripple) in DCM | IOUT = 10 mA, VOUT ≤ 1 V | –30 | 40 | mV | ||

| SR(VOUT) | Output DVS slew rate | 2.5 | 3.125 | mV/µs | ||

| IOUT | Continuous DC output current | 3 | A | |||

| IIND_LIM | HSD FET current limit | 4.3 | 7 | A | ||

| IQ | Quiescent current | VIN = 5 V, VOUT = 1 V | 35 | µA | ||

| ΔVOUT/ΔVIN | Line regulation | VOUT = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V, IOUT = 1.5 A |

–0.5% | 0.5% | ||

| ΔVOUT/ΔIOUT | Load regulation | VIN = 5 V, VOUT = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V, IOUT = 0 A to 3 A, referenced to VOUT at IOUT = 1.5 A |

–0.2% | 2% | ||

| VTH_PG | Power Good deassertion threshold in percentage of target VOUT | VOUT rising | 108% | |||

| VOUT falling | 92% | |||||

| VTH_HYS_PG | Power Good reassertion hysteresis entering back into VTH_PG | VOUT rising or falling | 3% | |||

| RDIS | Output auto-discharge resistance | BUCK3_DIS[1:0] = 01 | 100 | Ω | ||

| BUCK3_DIS[1:0] = 10 | 200 | |||||

| BUCK3_DIS[1:0] = 11 | 500 | |||||

4.9 Electrical Characteristics: LDOs

over recommended input voltage range, TA = –40°C to 85°C and TA = 25°C for typical values (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| LDOA1 | ||||||

| VIN | Input voltage | 4.5 | 5 | 5.5 | V | |

| VOUT | DC output voltage | Set by LDOAx_VID[3:0] | 3.3 | |||

| Accuracy | IOUT = 0 to 200 mA | –2% | 2% | V | ||

| IOUT | DC output current | 200 | mA | |||

| ΔVOUT/ΔVIN | Line regulation | IOUT = 40 mA | –0.5% | 0.5% | ||

| ΔVOUT/ΔIOUT | Load regulation | IOUT = 10 mA to 200 mA | –2% | 2% | ||

| IOCP | Overcurrent protection | VIN = 5 V, Measured with output shorted to ground | 500 | mA | ||

| VTH_PG | Power Good deassertion threshold in percentage of target VOUT | VOUT rising | 108% | |||

| VOUT falling | 92% | |||||

| tSTARTUP | Start-up time | Measured from EN = H to reach 95% of final value, COUT = 4.7 µF |

500 | µs | ||

| IQ | Quiescent current | IOUT = 0 A | 23 | µA | ||

| COUT | External output capacitance | 2.7 | 4.7 | 10 | µF | |

| ESR | 100 | mΩ | ||||

| RDIS | Output auto-discharge resistance | LDOA1_DIS[1:0] = 01 | 100 | Ω | ||

| LDOA1_DIS[1:0] = 10 | 190 | Ω | ||||

| LDOA1_DIS[1:0] = 11 | 450 | Ω | ||||

| LDOA2 and LDOA3 | ||||||

| VIN | Power input voltage | VOUT + VDROP (1) | 1.8 | 1.98 | V | |

| VOUT | LDOA2 DC output voltage | Set by LDOAx_VID[3:0] | 0.7 | V | ||

| LDOA3 DC output voltage | Set by LDOAx_VID[3:0] | 1.2 | V | |||

| DC output voltage accuracy | IOUT = 0 to 600 mA | –2% | 3% | |||

| IOUT | DC output current | 600 | mA | |||

| VDROP | Dropout voltage | VOUT = 0.99 × VOUT_NOM, IOUT = 600 mA |

350 | mV | ||

| ΔVOUT/ΔVIN | Line regulation | IOUT = 300 mA | –0.5% | 0.5% | ||

| ΔVOUT/ΔIOUT | Load regulation | IOUT = 10 mA to 600 mA | –2% | 2% | ||

| IOCP | Overcurrent protection | Measured with output shorted to ground | 0.65 | 1.25 | A | |

| VTH_PG | Power Good assertion threshold in percentage of target VOUT | VOUT rising | 108% | |||

| VOUT falling | 92% | |||||

| tSTARTUP | Start-up time | Measured from EN = H to reach 95% of final value, COUT = 4.7 µF | 500 | µs | ||

| IQ | Quiescent current | IOUT = 0 A | 20 | µA | ||

| LDOA2 and LDOA3 (continued) | ||||||

| PSRR | Power supply rejection ratio | f = 1 kHz, VIN = 1.8 V, VOUT = 1.2 V, IOUT = 300 mA, COUT = 2.2 µF – 4.7 µF |

48 | dB | ||

| f = 10 kHz, VIN = 1.8 V, VOUT = 1.2 V, IOUT = 300 mA, COUT = 2.2 µF – 4.7 µF |

30 | dB | ||||

| COUT | External output capacitance | 2.2 | 4.7 | 10 | µF | |

| ESR | 100 | mΩ | ||||

| RDIS | Output auto-discharge resistance | LDOA2_DIS[1:0] = 01 | 80 | Ω | ||

| LDOA2_DIS[1:0] = 10 | 180 | |||||

| LDOA2_DIS[1:0] = 11 | 475 | |||||

| VTT LDO | ||||||

| VIN | Power input voltage | 1.2 | 3.3 | V | ||

| VOUT | DC output voltage | VIN = 1.2 V, Measured at VTTFB pin | VIN / 2 | V | ||

| DC output voltage accuracy | Relative to VIN / 2, IOUT ≤ 10 mA, 1.1 V ≤ VIN ≤ 1.35 V |

–10 | 10 | mV | ||

| Relative to VIN / 2, IOUT ≤ 500 mA, 1.1 V ≤ VIN ≤ 1.35 V |

–25 | 25 | ||||

| IOUT | DC output current | sink(–) and source(+) | –500 | 500 | mA | |

| ΔVOUT/ΔIOUT | Load regulation | 1.1 V ≤ VIN ≤ 1.35 V, IOUT = –500 mA to 500 mA |

–4% | 4% | ||

| IOCP | Overcurrent protection | Measured with output shorted to ground | 0.95 | A | ||

| VTH_PG | Power Good deassertion threshold in percentage of target VOUT | VOUT rising | 110% | |||

| VOUT falling | 95% | |||||

| VTH_HYS_PG | Power Good reassertion hysteresis entering back into VTH_PG | 5% | ||||

| IQ | Total ground current | VIN = 1.2 V, IOUT = 0 A | 240 | µA | ||

| ILKG | OFF leakage current | VIN = 1.2 V, disabled | 1 | µA | ||

| CIN | External input capacitance | 10 | µF | |||

| COUT | External output capacitance | 35 | µF | |||

| RDIS | Output auto-discharge resistance | VTT_DIS = 0 | 1000 | kΩ | ||

| VTT_DIS = 1 | 60 | 80 | 100 | Ω | ||

4.10 Electrical Characteristics: Load Switches

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| SWA1 | ||||||

| VIN | Input voltage range | 0.5 | 1.8 | 3.3 | V | |

| IOUT | DC output current | 300 | mA | |||

| RDSON | ON resistance | VIN = 1.8 V, measured from PVINSWA1 pin to SWA1 pin at IOUT = IOUT,MAX | 60 | 93 | mΩ | |

| VIN = 3.3 V, measured from PVINSWA1 pin to SWA1 pin at IOUT = IOUT,MAX | 100 | 165 | ||||

| VTH_PG | Power Good deassertion threshold in percentage of target VOUT | VOUT rising | 108% | |||

| VOUT falling | 92% | |||||

| VTH_HYS_PG | Power Good reassertion hysteresis entering back into VTH_PG | VOUT rising or falling | 2% | |||

| IINRUSH | Inrush current upon turnon | VIN = 3.3 V, COUT = 0.1 µF | 10 | mA | ||

| IQ | Quiescent current | VIN = 3.3 V, IOUT = 0 A | 10.5 | µA | ||

| VIN = 1.8 V, IOUT = 0 A | 9 | |||||

| ILKG | Leakage current | Switch disabled, VIN = 1.8 V | 7 | 370 | nA | |

| Switch disabled, VIN = 3.3 V | 10 | 900 | ||||

| COUT | External output capacitance | 0.1 | µF | |||

| RDIS | Output auto-discharge resistance | SWA1_DIS[1:0] = 01 | 100 | Ω | ||

| SWA1_DIS[1:0] = 10 | 200 | |||||

| SWA1_DIS[1:0] = 11 | 500 | |||||

| SWB1_2 | ||||||

| VIN | Input voltage range | 0.5 | 1.8 | 3.3 | V | |

| IOUT | DC current per output | 400 | mA | |||

| RDSON | ON resistance | VIN = 1.8 V, measured from PVINSWB1_B2 pin to SWB1/SWB2 pin at IOUT = IOUT,MAX | 68 | 92 | mΩ | |

| VIN = 3.3 V, measured from PVINSWB1_B2 pin to SWB1/SWB2 pin at IOUT = IOUT,MAX | 75 | 125 | mΩ | |||

| VTH_PG | Power Good deassertion threshold in percentage of target VOUT | VOUT rising | 108% | |||

| VOUT falling | 92% | |||||

| VTH_HYS_PG | Power Good reassertion hysteresis entering back into VTH_PG | VOUT rising or falling | 2% | |||

| IINRUSH | Inrush current upon turning on | VIN = 3.3 V, COUT = 0.1 µF | 10 | mA | ||

| IQ | Quiescent current | VIN = 3.3 V, IOUT = 0 A | 10.5 | µA | ||

| VIN = 1.8 V, IOUT = 0 A | 9 | |||||

| ILKG | Leakage current | Switch disabled, VIN = 1.8 V | 7 | 460 | nA | |

| Switch disabled, VIN = 3.3 V | 10 | 1150 | ||||

| COUT | External output capacitance | 0.1 | µF | |||

| RDIS | Output auto-discharge resistance | SWBx_DIS[1:0] = 01 | 100 | Ω | ||

| SWBx_DIS[1:0] = 10 | 200 | |||||

| SWBx_DIS[1:0] = 11 | 500 | |||||

4.11 Digital Signals: I2C Interface

over recommended free-air temperature range and over recommended input voltage range (typical values are at TA = 25°C) (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VOL | Low-level output voltage | VPULL_UP = 1.8 V | 0.4 | V | ||

| VIH | High-level input voltage | 1.2 | V | |||

| VIL | Low-level input voltage | 0.4 | V | |||

| ILKG | Leakage current | VPULL_UP = 1.8 V | 0.01 | 0.3 | µA | |

| RPULL-UP | Pullup resistance | Standard mode | 8.5 | kΩ | ||

| Fast mode | 2.5 | |||||

| Fast mode plus | 1 | |||||

| COUT | Total load capacitance per pin | 50 | pF | |||

4.12 Digital Input Signals (CTLx)

over recommended free-air temperature range and over recommended input voltage range (typical values are at TA = 25°C) (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VIH | High-level input voltage | 0.85 | V | |||

| VIL | Low-level input voltage | 0.4 | V | |||

4.13 Digital Output Signals (IRQB, GPOx)

Over recommended free-air temperature range and over recommended input voltage range (typical values are at TA = 25°C) (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VOL | Low-level output voltage | IOL < 2 mA | 0.4 | V | ||

| ILKG | Leakage current | VPULL_UP = 1.8 V | 0.35 | µA | ||

4.14 Timing Requirements

over recommended free-air temperature range and over recommended input voltage range (typical values are at TA = 25°C) (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| I2C INTERFACE | |||||

| fCLK | Clock frequency (standard mode) | 100 | kHz | ||

| Clock frequency (fast mode) | 400 | kHz | |||

| Clock frequency (fast mode plus) | 1000 | kHz | |||

| tr | Rise time (standard mode) | 1000 | ns | ||

| Rise time (fast mode) | 300 | ns | |||

| Rise time (fast mode plus) | 120 | ns | |||

| tf | Rise time (standard mode) | 300 | ns | ||

| Rise time (fast mode) | 300 | ns | |||

| Rise time (fast mode plus) | 120 | ns | |||

4.15 Switching Characteristics

over operating free-air temperature range and over recommended input voltage range (typical values are at TA = 25°C) (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| BUCK CONTROLLERS | ||||||

| tPG | Total turnon time | Measured from enable going high to when output reaches 90% of target value. | 550 | 850 | µs | |

| TON,MIN | Minimum on-time of DRVH | 50 | ns | |||

| TDEAD | Driver dead-time | DRVH off to DRVL on | 15 | ns | ||

| DRVL off to DRVH on | 30 | ns | ||||

| fSW | Switching frequency | Continuous-conduction mode, VIN = 13 V, VOUT ≥ 1 V |

1000 | kHz | ||

| BUCK CONVERTERS | ||||||

| tPG | Total turnon time | Measured from enable going high to when output reaches 90% of target value. | 250 | 1000 | µs | |

| fSW | Switching frequency | Continuous-conduction mode, VOUT = 1 V, IOUT = 1 A | 1.7 | MHz | ||

| Continuous-conduction mode, VOUT = 1.05 V, IOUT = 1 A | 1.9 | MHz | ||||

| Continuous-conduction mode, VOUT = 1.8 V, IOUT = 1 A | 2.5 | MHz | ||||

| LDOAx | ||||||

| tSTARTUP | Start-up time | Measured from enable going high to when output reaches 95% of final value, VOUT = 1.2 V, COUT = 4.7 µF |

180 | µs | ||

| VTT LDO | ||||||

| tSTARTUP | Start-up time | Measured from enable going high to PG assertion, VOUT = 0.675 V, COUT = 40 µF |

22 | µs | ||

| SWA1 | ||||||

| tTURN-ON | Turnon time | Measured from enable going high to reach 95% of final value, VIN = 3.3 V, COUT = 0.1 µF |

0.85 | ms | ||

| Measured from enable going high to reach 95% of final value, VIN = 1.8 V, COUT = 0.1 µF |

0.63 | ms | ||||

| SWB1_2 | ||||||

| tTURN-ON | Turnon time | Measured from enable going high to reach 95% of final value, VIN = 3.3 V, COUT = 0.1 µF |

1.1 | ms | ||

| Measured from enable going high to reach 95% of final value, VIN = 1.8 V, COUT = 0.1 µF |

0.82 | ms | ||||

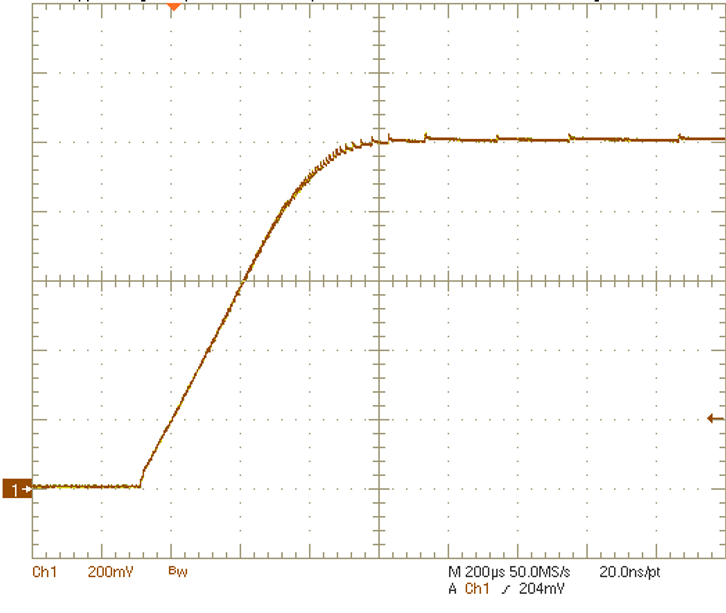

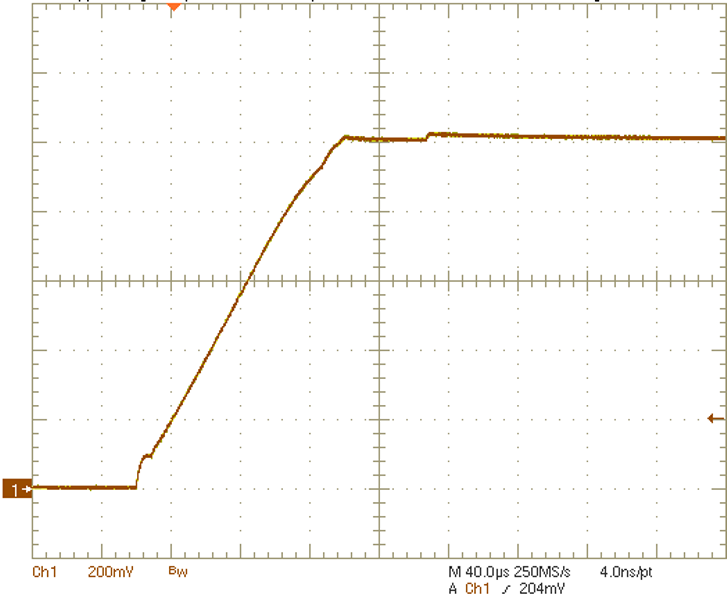

4.16 Typical Characteristics

Measurements done at 25°C. Figure 4-1 BUCK2 Controller Start Up

Figure 4-1 BUCK2 Controller Start Up

Figure 4-3 BUCK1 Efficiency at VIN = 13 V

Figure 4-3 BUCK1 Efficiency at VIN = 13 V

Figure 4-5 BUCK3 Efficiency at VIN = 5 V

Figure 4-5 BUCK3 Efficiency at VIN = 5 V

Figure 4-2 BUCK3 Converter Start Up

Figure 4-2 BUCK3 Converter Start Up

Figure 4-4 BUCK1 Efficiency at VIN = 18 V

Figure 4-4 BUCK1 Efficiency at VIN = 18 V