ZHCSSG2 june 2023 – june 2023 UCC14140-Q1

PRODUCTION DATA

9.2.2.1 电容器选型

UCC14140-Q1 器件提供隔离式输出 VDD-VEE 作为其主输出。该器件还使用 VDD-VEE 作为其电源,提供了另一个输出 COM-VEE。由于两个输出都与输入隔离,并且共用 VEE 作为公共参考点,因此 UCC14140-Q1 输出可配置为两个正输出、两个负输出或一正一负两个输出。UCC14140-Q1 输出也可用作单个正输出或单个负输出。

当模块配置为一正一负两个输出时,务必要正确选择输出电容比 COUT2 和 COUT3,来优化调节并避免导致过压或欠压故障。

| 电容器 | 值 (µF) | 说明 |

|---|---|---|

| CIN | 20 + 0.1 | 在 VIN 引脚附近并联放置一个 20μF 和一个 0.1μF 高频去耦电容器。当从电压源到 VIN 引脚的串联阻抗较大时,可以使用大于 20uF 的电容来减少电压纹波。 |

| COUT1 | 10 + 0.1 | 添加一个 10μF 和一个 0.1μF 电容器,用于对 (VDD–VEE) 进行高频去耦。应靠近 VDD 和 VEE 引脚放置。可以使用大于 10uF 的电容来降低输出电压纹波。 |

COUT1B | 请见下方 | 大容量去耦输出充电电容器需放置在栅极驱动器引脚旁边。COUT2 与 COUT3 的电容比对于在充电或放电开关周期内优化双路输出分压器精度非常重要;而 COUT1B 电容器用于最大程度地减小总电容,包括 COUT1B、COUT2 和 COUT3 电容值。 |

| COUT2 | 请见下方 | |

| COUT3 | 请见下方 |

输出电容器去耦对于实现理想的栅极驱动器运行状态非常重要。通过降低充电/放电路径中的寄生阻抗,可实现良好的高频去耦效果。使用具有低 ESR 和低 ESL 的陶瓷电容器以及尽可能减小布线阻抗很重要。

如图 9-3 所述,UCC14141-Q1 的 VVDD-VEE 输出引脚需要一个去耦电容器 COUT1,用于高频去耦。然而,栅极驱动器引脚上需要 COUT2 和 COUT3,用于 VVDD-COM 和 VVEE-COM 去耦。COUT1 和 COUT2/COUT3 组合之间的阻抗可防止 COUT1 协助栅极驱动器的高频去耦,从而要求 COUT2 和 COUT3 接受满载。阻抗可能来自 PCB 布线、插座连接、EMI 滤波器或铁氧体磁珠等。这会导致 COUT2(尤其是 COUT3)相对较大,从而实现较小的压降。

图 9-3 具有 Cout1、Cout2 和 Cout3 的双路输出原理图

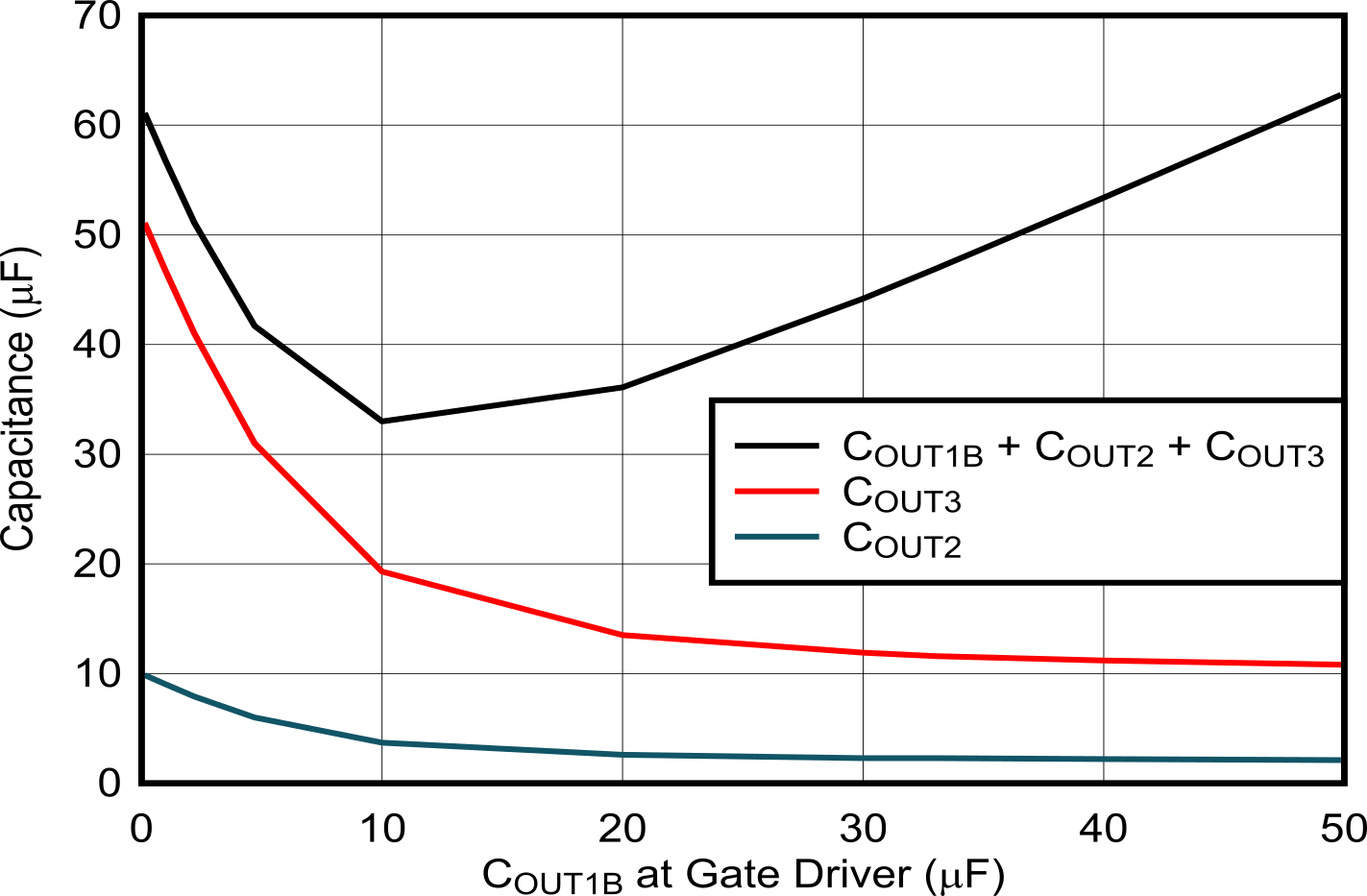

图 9-3 具有 Cout1、Cout2 和 Cout3 的双路输出原理图通过在 COUT2 和 COUT3 旁边的栅极驱动器引脚处加入一个 VVDD-VEE 的 COUT1B 电容器,可降低所需的 COUT2 和 COUT3 电容,如图 9-4 所示。COUT1B 可协助 COUT2 和 COUT3 的去耦总电容;从而降低实现所需压降需要的总电容 (COUT1B + COUT2 +COUT3)。图 9-5 显示,当 COUT1B 从“无”增加到更高的 COUT1B 值时,COUT2 和 COUT3 显著减少,总净电容减少,直至达到收益递减点(“拐点”),即任何额外的 COUT1B 都会使 COUT2 和 COUT3 降低幅度相对较小,并开始使总净电容显著增加。使用最小总净电容下的最佳 COUT1B、COUT2 和 COUT3 值,有利于减小输出电容器尺寸和降低 BOM 成本。

图 9-4 具有 Cout1、Cout1B、Cout2 和 Cout3 的双路输出原理图

图 9-4 具有 Cout1、Cout1B、Cout2 和 Cout3 的双路输出原理图 图 9-5 输出电容随 Cout1B 选择的变化

图 9-5 输出电容随 Cout1B 选择的变化为了计算 COUT1B、COUT2 和 COUT3,我们计算了等效 (VDD-COM) 电容,该电容等于 COUT1B 和 COUT3 与 COUT2 并联的串联电容。将调整该等效 (VDD-VEE) 电容的大小,以限制电源开关(SiC 或 IGBT)栅极电荷开启时的预定 (VDD-COM) 放电压降。

COUT2 与 COUT3 之比定义为 K23 的系数,它是分压器分压比与差分电流之比的乘积。分压器分压比源于两个电容器的串联配置。分流比是根据流经两个电容器的充电电流计算得出。IMAX_POWER 是突发导通时间内电源模块的最大瞬时电流,可通过将 25°C TA 下数据表 SOA 曲线上的最大功率除以 VVDD-VEE 来获得。IVDD-COM 是 VDD 和 COM 之间的总静态电流。以栅极驱动器为例,IVDD-VEE 是不进行开关时的电流消耗。ICOM-VEE 是 COM 和 VEE 之间的总静态电流。基于 KCL,在突发导通时间内对 COUT2 进行充电的差分电流为 (IMAX_POWER - IVDD-COM),而对 COUT3 进行充电的差分电流为 (IMAX_POWER - ICOM-VEE)。

其中

接下来,将上述 COUT3 表达式插入方程式 1,我们会得到

接近负载点的总去耦电容 (COUT_Total) 是 COUT1B、COUT2 和 COUT3 的总和。目标是找到最小的 COUT1B,以尽可能降低 COUT_Total,从而节省 BOM 成本和空间,同时保持所需的负载瞬态性能。可通过求解 COUT_Total 的偏导数(等于 0)来计算最优 COUT1B。

之后,求解方程式 5,包括方程式 7,COUT2 可以按下式求解