ZHCSSG2 june 2023 – june 2023 UCC14140-Q1

PRODUCTION DATA

9.5.1 布局指南

UCC14140-Q1 集成隔离式电源解决方案可简化系统设计并减少使用的电路板面积。请遵循这些指南进行正确的 PCB 布局,以便实现理想性能。为了实现热性能良好的 PCB 设计,推荐在外部层上使用 2 盎司铜的至少 4 层 PCB 层堆叠。

- 输入电容器:

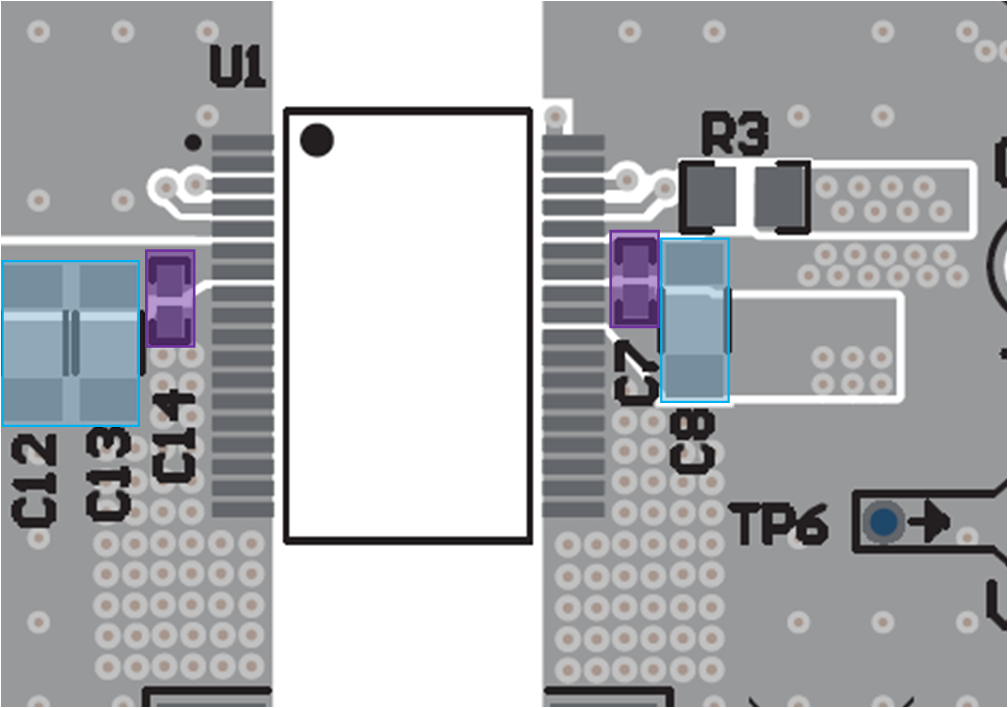

- 将 0.1µF 高频旁路电容器 (C14) 尽可能靠近引脚 6、7 (VIN) 和引脚 8–18 (GNDP) 放置,并与 IC 位于 PCB 的同一侧。0402 陶瓷 SMD 或更小尺寸是实现最佳布局所需的尺寸。请勿在旁路电容器和 IC 引脚之间放置任何过孔,以强制高频电流通过电容器。

- 将大容量 VIN 电容器(C12、C13)尽可能靠近 0.1µF 高频旁路电容器 (C14)、与之并联,并与 IC 位于 PCB 的同一侧。

- 输出电容:

- 将 0.1µF 高频旁路电容器 (C7) 尽可能靠近引脚 28、29 (VDD) 和引脚 30、31 (VEE) 放置,并与 IC 位于 PCB 的同一侧。0402 陶瓷 SMD 或更小尺寸是实现最佳布局所需的尺寸。请勿在旁路电容器和 IC 引脚之间放置任何过孔,以强制高频电流通过电容器。

- 将大容量 VDD-VEE 电容器 (C8) 尽可能靠近 0.1µF 高频旁路电容器 (C7)、与之并联,并与 IC 位于 PCB 的同一侧。

图 9-10

图 9-10

- 栅极驱动器输出电容器:COUT2 和 COUT3 是 Excel 计算器工具中引用的参考位号。COUT2 是 VDD-COM 之间的电容器,COUT3 是 COM-VEE 之间的电容器。COUT2 和 COUT3 是栅极驱动器 IC 所需的电容器。正确选择并放置 COUT2 和 COUT3 对于实现 UCC14140-Q1 和栅极驱动器 IC 的出色性能至关重要。

-

COUT2 和 COUT3 应放置在栅极驱动器 IC 旁边,以实现出色的去耦和栅极驱动器开关性能

- 在 VDD-VEE 之间添加一个 COUT1B,但与 COUT2 和 COUT3 并联放置在栅极驱动器上,这将减少所需的总电容,降低对电容器变化的敏感度,并允许使用更高的 RLIM 电阻值。

-

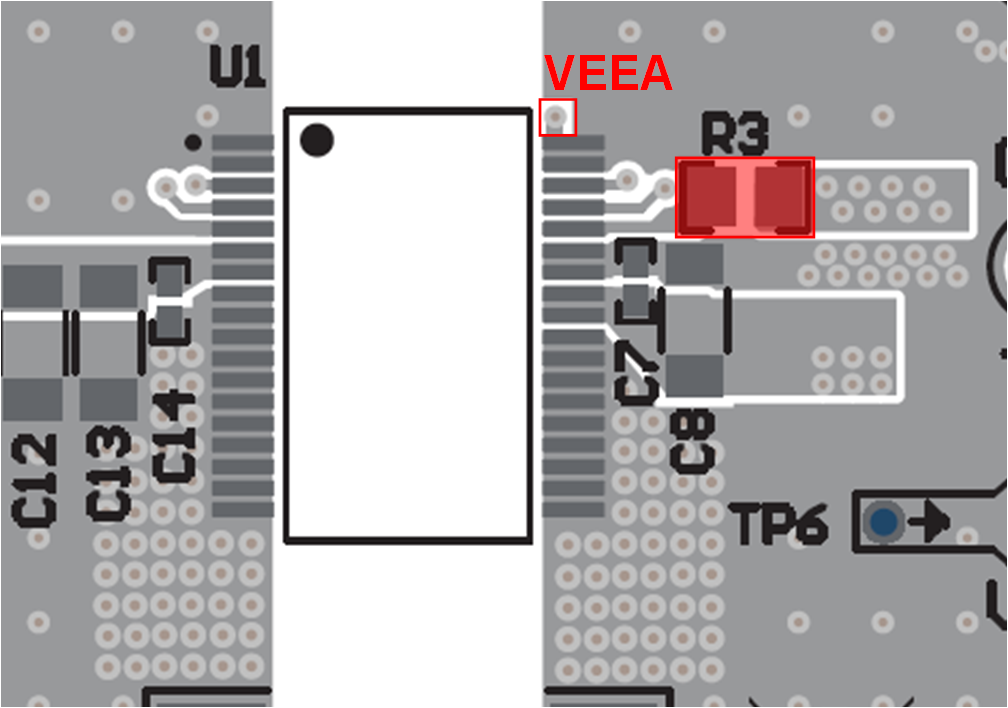

- RLIM:将 RLIM (R3) 靠近引脚 32 放置,使其位于输出电容分压器的 COM 中点之间。R3 右侧显示的过孔布局连接到 COM。

图 9-11

图 9-11 -

反馈:

-

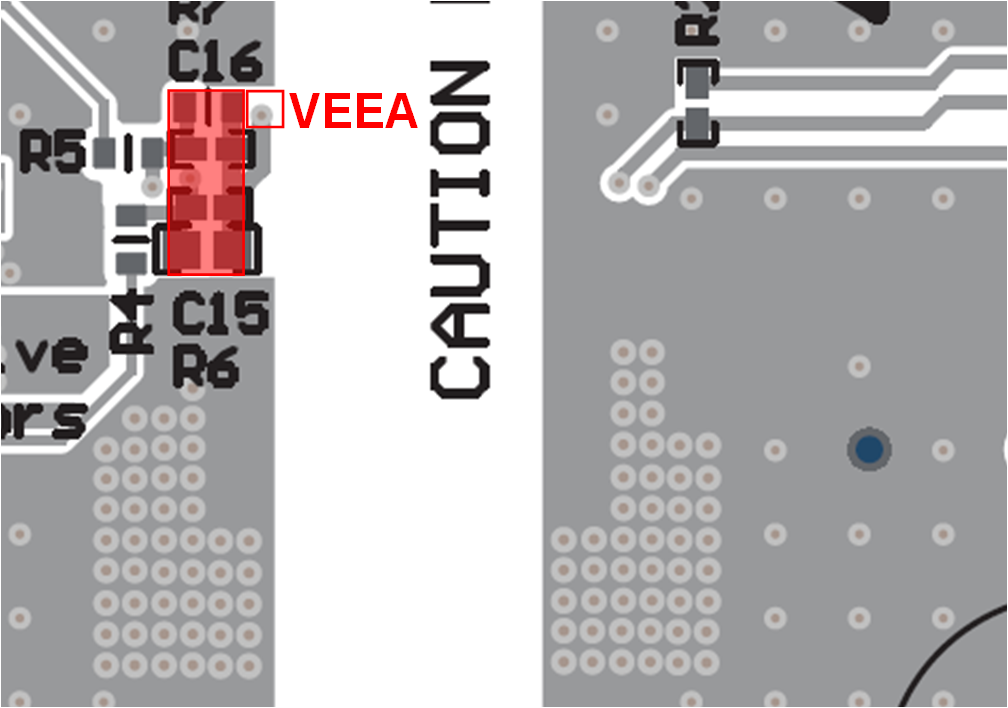

VEEA(引脚 35)应通过所有 PCB 层与 VEE 平面隔离,如下图红框所示。使用一个过孔直接连接到 FBVDD 和 FBVEE 低侧电阻器和电容器(C15-16、R6-7),如 PCB 底部所示。

-

将反馈电阻器 (R4-7) 和 330pF 陶瓷电容器与低侧电阻器 (R6-7) 并联放置在 IC 附近,最好放置在 IC 的另一侧(如 EVM 所示),或者放置在与 IC 靠近引脚 36 的同一层上。

-

顶层反馈电阻器应放置在低侧电阻器旁边,两个电阻器之间具有较短的直接连接,并具有与 FBVDD 的单一连接。用于检测稳压轨 (VDD-VEE) 的顶部连接应进行布线并连接到栅极驱动器引脚附近的 VDD 偏置电容器远程位置,以便获得出色的精度和瞬态响应。

-

顶层反馈电阻器应放置在低侧电阻器旁边,两个电阻器之间具有较短的直接连接,并具有与 FBVEE 的单一连接;而用于检测稳压轨 (COM-VEE) 的顶部连接应进行布线并连接到栅极驱动器引脚附近的 COM 偏置电容器远程位置,以便获得出色的精度和瞬态响应。

图 9-12

图 9-12

-

-

散热通孔:UCC14140-Q1 内部变压器直接连接到引线框。因此,如以下步骤所述,为 PCB 设计提供足够的空间和适当的散热至关重要。

-

TI 建议通过多个通孔将 VIN、GNDP、VDD 和 VEE 引脚连接到内部接地平面或电源平面。或者,使连接到这些引脚的多边形尽可能宽。

-

使用多个散热过孔将 PCB 顶层 GNDP 铜连接到底部 GNDP 铜。如果可能,建议在外部顶部和底部 PCB 层上使用 2 盎司铜。

-

使用多个散热过孔将 PCB 顶层 VEE 铜连接到底部 VEE 铜。如果可能,建议在外部顶部和底部 PCB 层上使用 2 盎司铜。

-

连接顶部和底部铜的散热过孔也可以连接到内部铜层,以进一步改善散热效果。

-

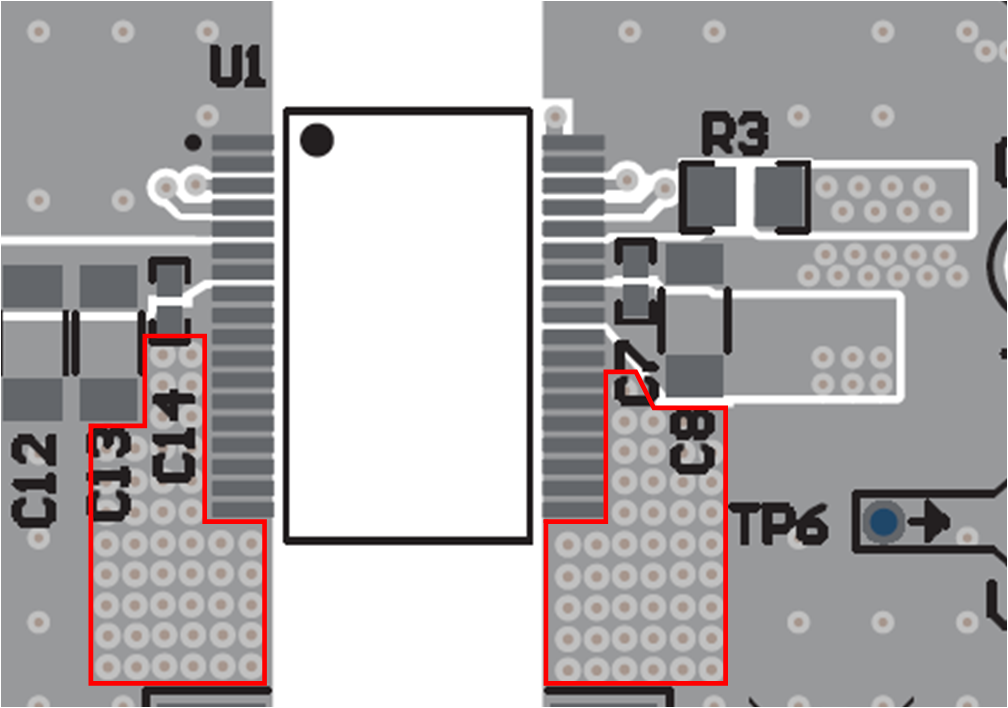

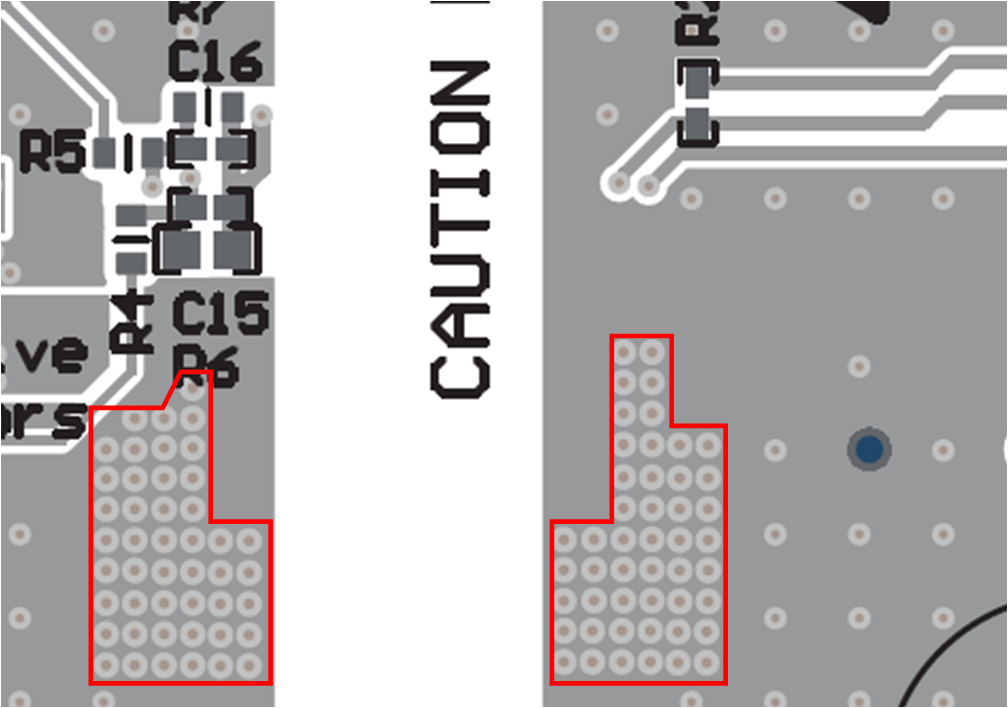

散热过孔类似于下图所示,但应在覆铜区允许的范围内尽可能多地使用散热过孔。UCC14141EVM-068 使用大约 220mil x 350mil 的散热过孔阵列(GNDP 初级侧 48 个散热过孔,VEE 次级侧 54 个散热过孔)。散热过孔直径为 30mil,孔大小为 12mil。

图 9-13

图 9-13  图 9-14

图 9-14 -

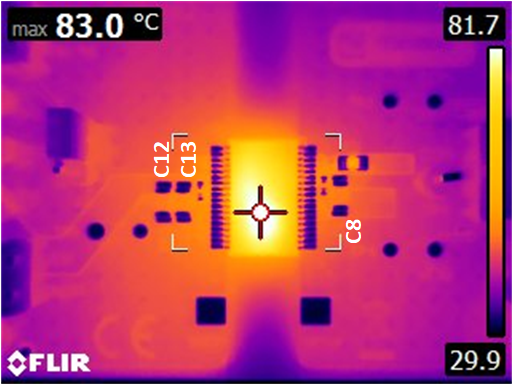

如热像图中所示,对于过孔数量和散热过孔阵列的尺寸,存在一个收益递减点。对于 1.5W 的输出功率,热传递在 C12 和 C8 之外迅速减弱。U1 到 C12 的内部焊盘线的距离为 320mil。

图 9-15 热像图

图 9-15 热像图 -

-

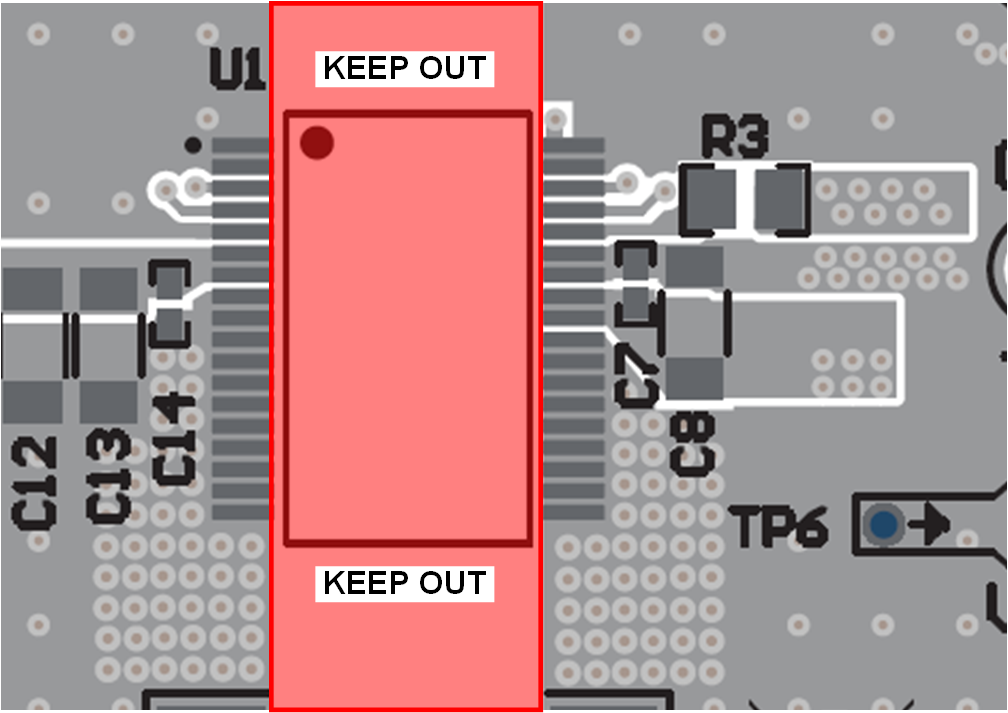

爬电间隙:避免在 UCC14140-Q1 下连接铜线,以保持数据表中指明的完整爬电距离、间隙和基本电压隔离额定值。在整个定义的隔离栅中,保持以红色突出显示的间隙宽度。基础型隔离的排除间隙可以比增强型隔离要求 (8mm) 小 50%。使用 8mm 可提供额外的裕度。

图 9-16

图 9-16 -

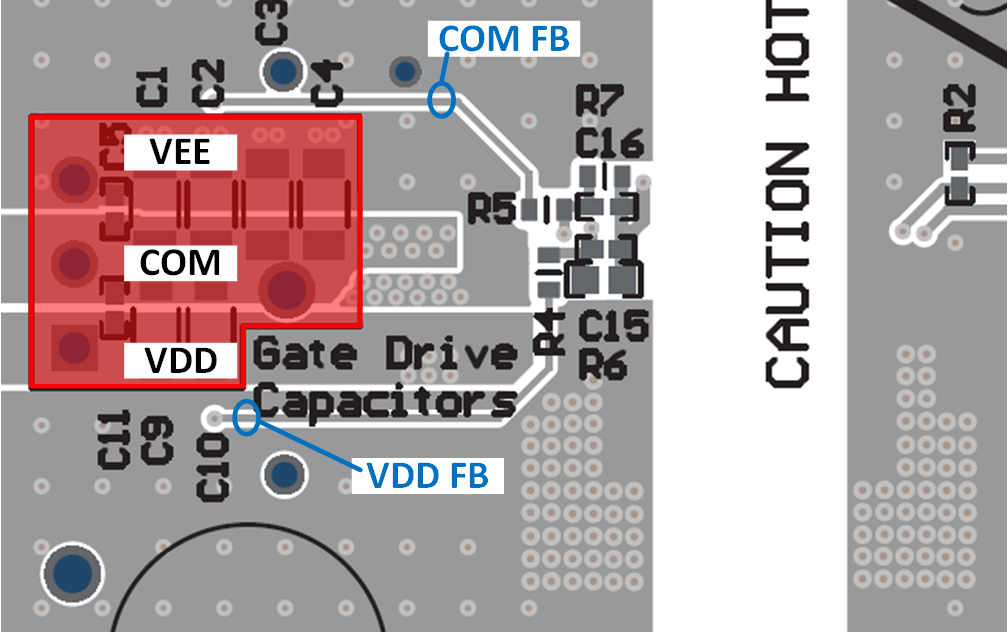

栅极驱动器电容器和反馈布线:

- UCC14141EVM-068 上安装了 VDD-COM 和 VEE-COM 电容器,但这些电容器需要尽可能靠近相关的栅极驱动器引脚放置。

- 为了更好地调节电压,COM (COM FB) 和 VDD (VDD FB) 的反馈布线应尽可能直接,以便直接在栅极驱动器 IC 附近的 VDD 和 COM 电容器处检测电压反馈。

图 9-17

图 9-17