SPRUIM6A October 2018 – November 2020

- 1Introduction

- 2AM65x IDK Overview

-

3Common Processor Board

- 3.1 Key Features

- 3.2 Functional Block Diagram

- 3.3

Overview of Common Processor Board

- 3.3.1 Clocking

- 3.3.2 Reset

- 3.3.3 Power Requirements

- 3.3.4 Configuration

- 3.3.5 Memory Interfaces

- 3.3.6 Ethernet Interface

- 3.3.7 LCD Display Interface

- 3.3.8 USB 2.0 Interface

- 3.3.9 CSI-2 Interface

- 3.3.10 Application Card Interface

- 3.3.11 SERDES Interface

- 3.3.12 GPMC/DSS Interface

- 3.3.13 I2C Interface

- 3.3.14 SPI Interface

- 3.3.15 Timer and Interrupt

- 3.3.16 Fan Connector

- 4IDK Application Card

- 5x2 Lane PCIe Personality Card

-

6Known Issues

- 6.1 Determining the Revision and Date Code for the EVM

- 6.2 Known Issues for the A, E4, and E3 Revision

- 6.3 Known Issues for the E4 & E3 Revision

- 6.4

Known Issues for the E3 Revision

- 6.4.1 Resonance Observed on the SoC Side of Some Filters Associated with VDDA_1V8

- 6.4.2 Additional LDO Power Supply Needed for VDDA_1P8_SERDES0

- 6.4.3 Length of the RESET Signal to the PCIE Connectors on the SERDES Daughter Card

- 6.4.4 The PORz_OUT and MCU_PORz_OUT Signals Go High During Power Sequencing

- 6.4.5 Orientation of the Current Monitoring Shunt Resistors

- 6.4.6 SD Card IO Supply Capacitance

- 6.4.7 PHY Resistor Strapping Changed to Disable EEE Mode

- 6.4.8 The I2C Address for the I2C Boot Memory changed to 0x52

- 7Configuring the PRG0 and PRG1 Ethernet Interface to MII

- 8Revision History

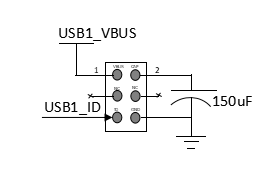

3.3.8 USB 2.0 Interface

The SoC supports two USB 2.0 ports – USB0 and USB1. The USB0 port is routed to the SERDES daughter card connector along with USB0 ID pins and DRVVBUS0 for host / slave detect and power enable. The USB1 port is terminated to a uAB connector (J3) and supports both host and slave mode. In the host mode, up to 500 mA, 5 V is supported for the slave device. A power switch is included which is controlled by DRV_VBUS signal from the AM65x processor. A 2x3 header (J4) is provided to install the 2-position ganged shunt to configure the port for host mode, as shown in Figure 3-19. Place the shunt on pin 1 and 2 to enable bulk capacitance on VBUS, and place the shunt on pin 5 and 6 to connect ID pin to ground.

Figure 3-19 J4 Header for USB2.0 Host Interface

Figure 3-19 J4 Header for USB2.0 Host Interface