SSZTAP0 november 2016 SN74CB3Q3125 , TMUX1511

Many modern high-speed systems like enterprise servers or network switches require continuous operation without affecting signal integrity, especially while swapping hardware. One of the essential and basic features for isolation requirements is a partial power-down feature.

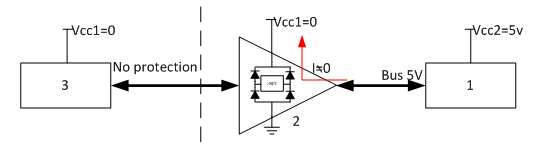

As Figure 1 shows, device No. 1 is powered up in the system with 5V, while device No. 2 and No.3 is powered down with Vcc = 0; all subsequent devices are powered down as well. The bus logic is still active with 5V. The Electrostatic Discharge (ESD) clamp diodes to Vcc will become active and start conducting, powering the system back to active. The current through the diode, unless limited by a series resistor, will be heavily forward-biased and hence will conduct tens of milliamps of current, which could lead to device damage. After this event, the reliability of the device when powered back to normal operation is questionable.

Figure 1 Device without Powered-off

Protection

Figure 1 Device without Powered-off

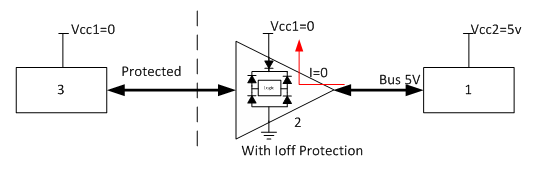

ProtectionFigure 2 shows the second device with Powered-off protection (also known as I-off protection) circuitry. The device and the system connected to Vcc1 are isolated from the active bus lines. The current through the ESD diodes is negligible due to the powered-off protection circuit inside, and the device reliability is intact. Powered-off protection ensures that no excessive current gets drawn into or out of the input, output or input /outputs (I/Os), which are biased to a voltage while the device powers down. The partial power-down mode helps avoid uncertain behavior during power down or power up.

Figure 2 Device with Powered-off

Protection

Figure 2 Device with Powered-off

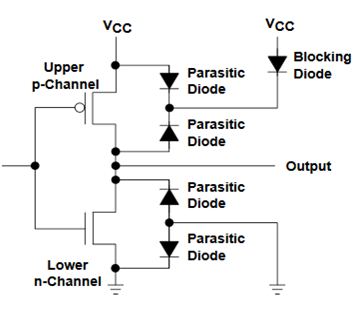

ProtectionThe basic Complementary Metal Oxide Semiconductor (CMOS) contains parasitic diodes between N-channel Metal Oxide Semiconductor (NMOS) and P-channel Metal Oxide Semiconductor (PMOS), biased such that there is minimal current leakage. The typical Ioff subcircuit consists of a blocking diode from Vcc connected to the common cathode (also known as the back gate) of the parasitic diodes to prevent current flowing back into Vcc, as shown in Figure 3.

Figure 3 Typical Powered-off Protection

Circuit

Figure 3 Typical Powered-off Protection

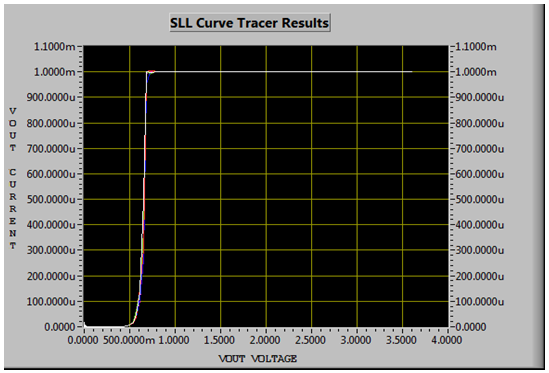

CircuitFigure 4 is a setup on the SN74CB3Q3125 device, which acts as a bidirectional switch when enabled and supports powered-off protection. The Vcc is ramping down and a constant current is pushed through the switch. As the Vcc ramps down to about 0.5V, the switch is conducting and lower than 0.5V, the device turns off and the Ioff circuit takes over.

Figure 4 Ioff Setup for Device Turn

on

Figure 4 Ioff Setup for Device Turn

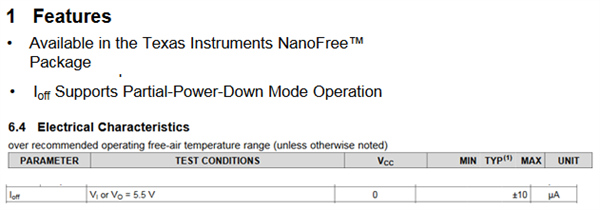

onThe device families with partial power-down list in the feature section of the datasheet as “Ioff partial-power- down mode,” and “isolation in powered off mode with V+=0,” among others. In data sheet specs, the Ioff is a separate row, mentioned along with the test conditions as shown in Figure 5.

Figure 5 Data Sheet Representation and

Electrical Specs

Figure 5 Data Sheet Representation and

Electrical SpecsTI classifies Ioff or powered-off protection as Level 1 isolation, which is a primary requirement for hot or live insertion for systems where you need to remove or insert cards in the backplane without compromising the system’s overall signal integrity. The partial power down mode helps reduce energy consumption by turning off a portion of a system and isolating the rest of the subsystem. The partial power-down feature is found in most logic familes: ABT, ALVT, AVC, AUC, AUP, CBTLV, CBT-C, GTL, GTLP LV-A, LVC, LVT and VME.

Did you know about the Ioff or powered-off protection feature and its importance in the applications you are currently using? Please comment if you’ve made a conscious decision to choose a logic device because of its powered-off protection feature rather than another device without one.

The TMUX1511 is pin-out compatible to the SN74CB3Q3125.