ZHCAA38E August 2021 – January 2023 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

5.1.3 硬件控制

- 测试条件

器件 1 发送数据 -> 器件 2 在接收数据时还使用硬件通道将数据传回器件 1 -> 器件 1 接收返回的数据,CPU 验证它是否与最初发送的 TX 数据匹配。

- 测试案例

8 个字的数据长度,2 条数据线,TXCLK = 30MHz,启用设置 ④(表 5-1)。

在此测试中,数据包在由器件 2 接收的同时,也会使用直通 Tx 通道发送出去。尽管器件 2 会验证数据包是否存在错误,但与其他传输模式不同,这些错误不会阻止数据包传递到器件 1。

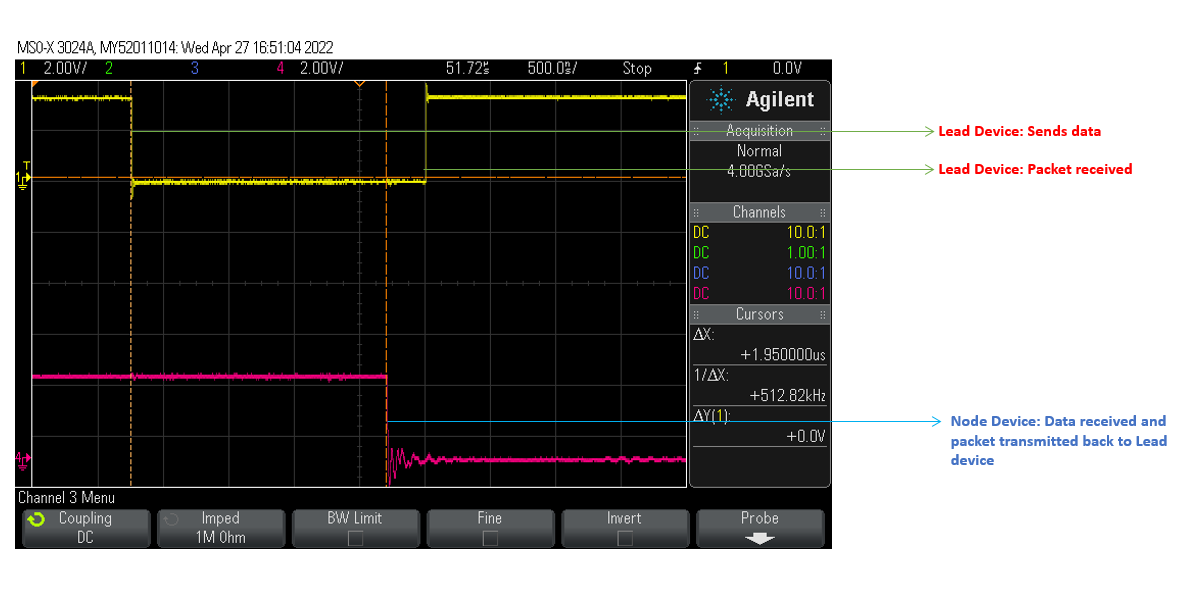

图 5-5 使用硬件控制的 FSI 通信

图 5-5 使用硬件控制的 FSI 通信在测试中,当通信期间发生特定事件时,会在软件内翻转 GPIO,并使用示波器对其进行测量以获取相应的时序数据。在#GUID-C494C962-27E1-427E-99E7-071BDCC50D08 中,黄色信号表示器件 1(主控器件)的 GPIO 翻转,品红色信号表示器件 2(节点器件)的 GPIO 翻转。根据GUID-B94A2134-E2F2-4742-A0D2-A5DA9BED9538.html#EQUATION-BLOCK_LRC_5FS_SQB 中的计算,在两条数据线上以 30MHz 发送 8 个字所花费的理论传输时间为 1.6µs。因此,主控器件上发送和接收之间的理论间隔时间也等于 1.6μs(假设不存在有线传输延迟),这是因为硬件控制模式会运用 FSI 的直通 Rx TDM 特性,除了传输延迟之外没有任何延迟。但是,在测试中观察到的 1.95µs 值包括了翻转 GPIO 所花费的时间、隔离器引入的延迟、收发器、硬件和电缆中的信号传播延迟等。

表 5-4 中给出了更多测试结果,用于比较使用 CPU 控制、DMA 控制和硬件控制的 FSI。在 FSI 数据帧结构中固定了开销位的情况下,使用更大的数据长度来最大限度地提高有效数据吞吐量是有益的。

| FSITXCLK (MHz) | 数据线路数 | 数据长度(16 位字) | 传输时间 (µs) #T5807283-24 | 缓冲区数据移动时间 (µs) #T5807283-24 | 理论传输速度 (Mbps) #T5807283-25 | 测试传输速度 (Mbps) | |

|---|---|---|---|---|---|---|---|

| CPU 控件 | 50 | 2 | 8 | 1.4 | 4.9 | 175 | 120 |

| 50 | 2 | 16 | 2.1 | 8.3 | 185 | 141 | |

| 50 | 1 | 8 | 2.1 | 4.9 | 100 | 80 | |

| 10 | 1 | 8 | 8.9 | 4.9 | 20 | 18.9 | |

| DMA 控件 | 50 | 2 | 8 | 1.9 | / | / | |

| 50 | 2 | 16 | 3.0 | / | / | ||

| 50 | 1 | 8 | 2.6 | / | / | ||

| 10 | 1 | 8 | 9.3 | / | / | ||

| 硬件控制 | 30 | 2 |

8 |

1.95 | / | / | |

| 30 | 2 | 16 | 3.05 | / | / | ||

| 12 | 1 | 8 | 7.3 | / | / | ||

在某些情况下,FSI 通信可能需要一些额外的稳健性和抗噪性,因此,还测试了较低的时钟频率。FSI 协议旨在仅在发生数据交换时进行通信。这有助于降低系统中的功耗和总体 EMI。此外,较低的 FSI 时钟频率和半双工通信可以提高整体系统级 EMI 性能,同时在相同的工作频率下继续提供比通用串行端口更高的吞吐量。通常,对于板对板连接,最好为每个信号使用一条双绞线或屏蔽线,而板载 FSI 信号布线长度应匹配,并且在布局中要格外小心,以增强抗噪性能。

在执行的测试中,在 TMDSFSIADAPEVM 板上使用了隔离和差分收发器器件,这可能会导致通道间的信号偏斜。在利用这些相同或相似器件和/或不同的信号布线长度的实际应用中,FSI 接收器模块内的集成偏斜补偿块可用于管理时钟信号和数据信号之间可能发生的信号偏斜。有关该主题的更多信息,请参阅快速串行接口 (FSI) 偏斜补偿。