ZHCAAB9E February 2021 – March 2021 TPS1H000-Q1 , TPS1H100-Q1 , TPS1H200A-Q1 , TPS1HA08-Q1 , TPS25200-Q1 , TPS27S100 , TPS2H000-Q1 , TPS2H160-Q1 , TPS2HB16-Q1 , TPS2HB35-Q1 , TPS2HB50-Q1 , TPS4H000-Q1 , TPS4H160-Q1

3.3.4 电容性浪涌期间的结温

高侧开关在容性浪涌期间承受的大量热耗散可能超过在功率耗散计算中计算出的器件平均功率耗散。如果器件结温升至 Tj(Max) 以上并可能使器件进入过热关断状态,这将引起可靠性问题。

针对平均功率耗散,我们按照Equation4 估算了结温。然而,容性浪涌事件不是稳态条件,且持续时间很短。由于热阻抗依赖于输入,高侧开关可能能够在浪涌事件期间在短时间内承受高于平均水平的功率耗散。

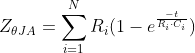

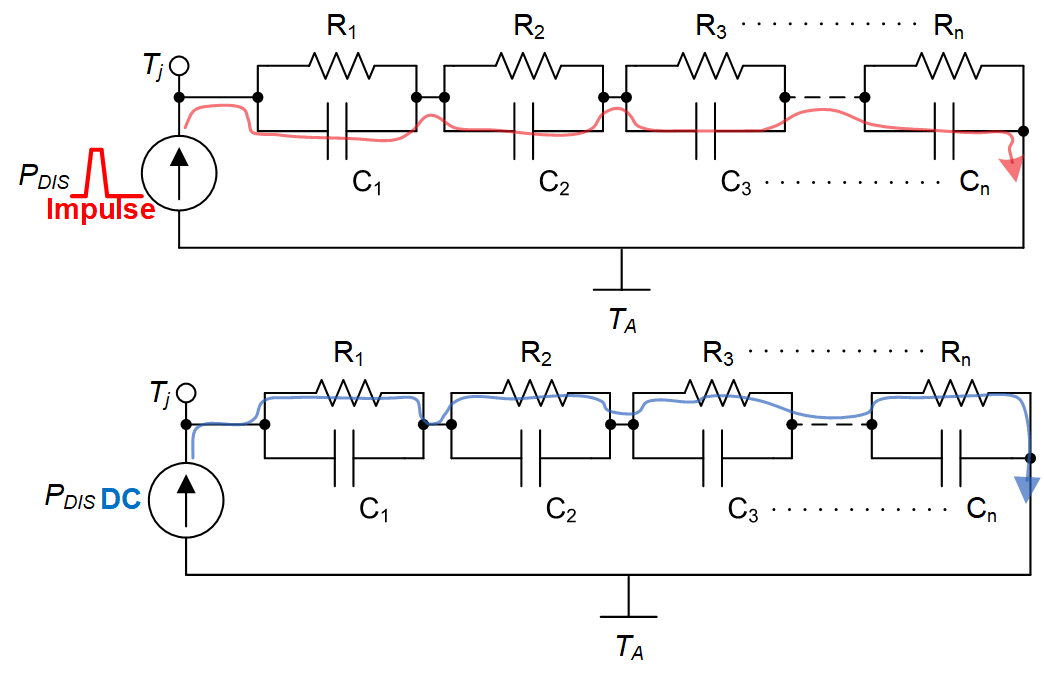

瞬态热阻抗通常通过 Foster RC 网络建模,如图 3-13 所示。该模型将高侧开关结温 TJ 与环境温度 TA 以及热 RC 网络的响应与器件 PDIS 中耗散的功率联系起来。模型中的热阻抗值在很大程度上取决于器件结构和封装。ZΘJA 的定义如Equation25 所示。

图 3-13 器件热阻抗的 Foster 网络模型

图 3-13 器件热阻抗的 Foster 网络模型该模型显示,如果周期远小于 RC 时间常数(用作高通滤波器),则功率的短脉冲对结温的影响较小。如果时间周期很长,热电容会限制功率,所有功率都会通过热阻抗 R1,2,3..n。模型中的这些热阻抗之和为 RΘJA,这一参数在器件数据表中有相关规定。对快速功率瞬变的响应的建模结果将与图 3-13 中的稳态功率耗散进行比较。

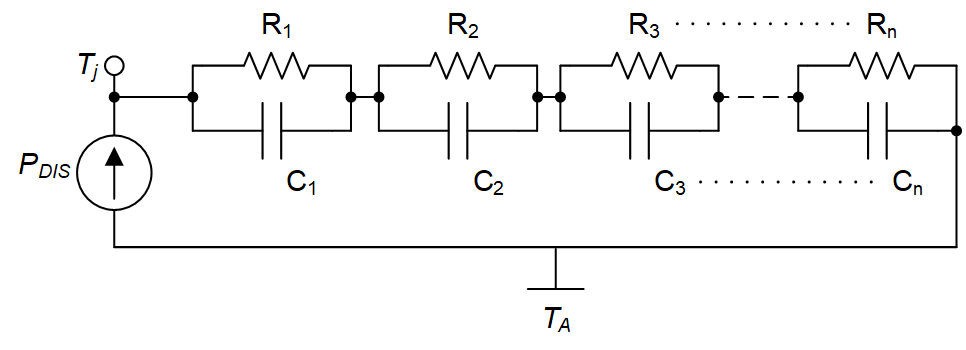

图 3-14 热时间常数对 RΘJA 和结温的影响

图 3-14 热时间常数对 RΘJA 和结温的影响在容性浪涌期间,ZΘJA、PDIS 和 TJ 是时间周期的函数,如图 3-13 所示。时间采用对数刻度,而 ZΘJA 是器件的时间相关热阻抗(基于结点和环境空气之间)。ZΘJA 根据特定器件的 Foster 模型的时间常数呈指数衰减。

图 3-15 浪涌周期内的 RΘJA 和结温

图 3-15 浪涌周期内的 RΘJA 和结温ZΘJA 在浪涌周期 Δt 期间单调增加,但由于电流限制,器件中的总功率耗散呈线性下降。峰值功率耗散 ILIM·VSUP 出现在此周期的开头,而衰减指数的总和 ZΘJA 在浪涌周期结束时达到峰值。

这种相反关系导致结温在浪涌周期大约一半(即 Δt/2)处达到峰值。只要浪涌周期 Δt 小于器件的有效热时间常数,或者在 ZΘJA 曲线变平之前,这一论断都成立。对于大多数高侧开关,此时间大约为 500s。

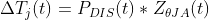

从数学角度来看,结温是 ZΘJA 和 PDIS 两者的卷积,这两者都随时间变化,如Equation26 所示。计算此卷积以获得 ΔTj 非常困难,如果器件有支持热性能的模型,最好将这个任务留给像 PSPICE 这样的仿真器。

有关瞬态热阻抗 ZΘJA 的多个图,请参阅附录 A,并且这些图针对表 3-1 中列出的每个 TI 高侧开关而提供。

Equation27 的精度在 TJ(Max) 的 PSPICE 仿真结果的 ±10% 以内,但仅适用于浪涌时间 Δt < ~500s 或 ZΘJA 曲线变平的位点。超过此位点后,随着峰值温度晚于 Δt/2 出现,该近似值开始下冲。此时应使用 PSPICE、Simulink 或其他建模工具进行更高级的热仿真。

可使用 2 通道或 4 通道导通情况下的瞬态热数据 ZΘJA 对多通道器件重复此过程。但是,此数据仅适用于两个通道同时导通且负载条件相同的情况。

除了我们的 TPS2H160-Q1 示例之外,我们还可以估算容性浪涌期间的 TJ(Max)。在此示例中,由单个通道驱动 470µF 的电容性负载,电流限值 ILIM 设置为 1A,电源电压为 24V,环境温度为 TA = 25°C。

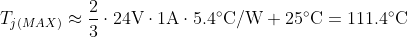

根据Equation18,我们发现浪涌周期持续时间为 Δt = 11.28ms。参考附录 A 中的 TPS2H160-Q1 数据,我们可以在 Δt = 11.28ms 处画一条线(如图 3-16 所示),找出浪涌周期 Δt 一半处的 RΘJA 值,因为我们仅在一个通道上进行驱动,得到 ZΘJA(Δt/2) = 5.4°C/W。

电流限制功能在浪涌周期内处于活动状态,并导致高侧开关中出现大量功率耗散。这是因为电流限制是通过控制 FET RON 实现的。在浪涌开始时,必须强制使 RON 比数据表规格高几个数量级,这会导致 FET 通道中的高 I2R 损耗。

一旦器件将 FET 导通,FET 上的 VDS 最初为 VSUP,并在电容器负载充电后降低至接近 0V。这个初始点正是出现峰值功率耗散的地方。在我们使用 TPS2H160-Q1 的示例中,我们已设置 ILIM = 1A,因此峰值功率为 24V·1A = 24W。现在,为了计算浪涌期间的 TJ(MAX),我们可以将 VSUP、ILIM、TA 和 ZΘJA(Δt/2) 的值代入Equation27,如Equation28 所示。

这是一个估计值,并且工作条件可能与设计时不同,因此建议在 TJ(Max) 和 150°C 之间留出足够的余量。TJ 限制不当可能会触发过热关断并降低可靠性和器件寿命。

除了保持 TJ < 150°C 外,建议保持 ΔTJ < TSW(其中的 TSW = 60°C),以便防止浪涌期间出现热振荡关断。浪涌期间会在 FET 结中出现最高温度,因此针对 ΔTJ < TSW 的设计可确保浪涌期间不会触发热振荡关断。TFET TCON 的时间在很大程度上取决于浪涌时的负载条件,因此 ΔTJ 也可能大于 TSW 而不会触发热振荡关断。

为获得准确的热结果,强烈建议对 TI 的高侧开关使用支持热性能的 PSPICE 模型,确保能够对 TJ、TCON 和热关断进行建模。更多有关在 PSPICE 中对器件热性能进行仿真的信息,请参阅《使用 PSpice 仿真器模拟 TI 智能高侧开关中的热行为》。