ZHCAE37A December 2019 – June 2024 AM67 , AM67A , AM68 , AM68A , AM69 , AM69A , DRA821U , DRA821U-Q1 , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1 , TDA4AEN-Q1 , TDA4AH-Q1 , TDA4AL-Q1 , TDA4AP-Q1 , TDA4APE-Q1 , TDA4VE-Q1 , TDA4VEN-Q1 , TDA4VH-Q1 , TDA4VL-Q1 , TDA4VM , TDA4VM-Q1 , TDA4VP-Q1 , TDA4VPE-Q1

3.1.2 布线规格

这些参数仅供参考,旨在使设计在仿真之前接近成功。为了确保 PCB 设计满足所有要求,需要对设计进行仿真并将这些结果与节 4中定义的仿真结果进行比较。

表 3-3 USB3.1(超高速)布线规格

| 参数 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|

| USB3.1 Gen1 运行速度 (超高速信号) | 2.5 (1) | GHz | ||

| USB3.1 信号布线长度 | 5000 (2) | Mil | ||

| USB3.1 差分对延迟差 | 1 | ps | ||

| USB3.1 差分阻抗 | 85.5 | 90 | 94.5 | Ω |

| USB3.1 布线上允许的残桩数 | 0 | 个残桩 | ||

| 每条 USB3.1 引线上的过孔数 | 2 | 个过孔 | ||

| 过孔残桩长度 (3) | 20 | Mil | ||

| USB3.1 差分对与任何其他引线之间的间距 (4) | 2×DS | 3×DS |

(1) 如需了解受支持的数据速率,请参阅特定于器件的数据手册。

(2) 最大值基于保守的信号完整性方法。仅当详细信号完整性分析确认运行和预期一致时,才能扩展该值。

(3) 在较高数据速率下运行时,可能需要过孔残桩控制。

(4) DS = 引线的差分间距。SoC 封装 BGA 区域可能存在例外情况。

表 3-4 USB2.0布线规格

| 参数 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|

| USB2.0 运行速度 | 240 | MHz | ||

| USB2.0 信号布线长度 | 7000 (1) | Mil | ||

| USB2.0 差分对延迟差 | 5 | ps | ||

| USB2.0 差分阻抗 | 81 | 90 | 99 | Ω |

| USB2.0 布线上允许的残桩数 | 0 | 个残桩 | ||

| 每条 USB2.0 引线上的过孔数 | 4 | 个过孔 | ||

| USB2.0 差分对与任何其他引线之间的间距 (2) | 2×DS | 3×DS |

(1) 最大值基于保守的信号完整性方法。仅当详细信号完整性分析确认运行和预期一致时,才能扩展该值。

(2) DS = 引线的差分间距。SoC 封装 BGA 区域可能存在例外情况。

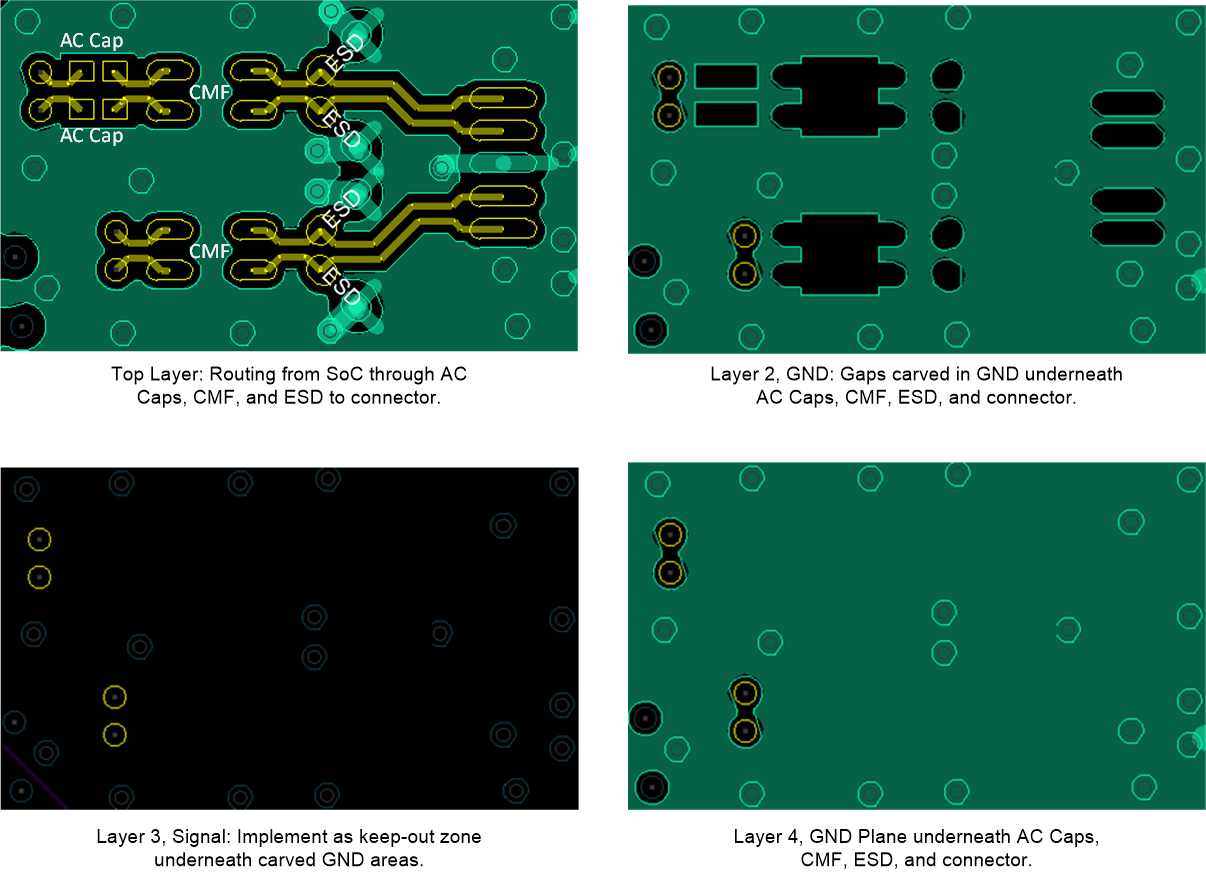

由于焊盘宽度增加,元件焊盘会产生阻抗不连续性。为了最大限度地减小阻抗不连续性,在元件焊盘下方的参考平面中形成空隙。图 3-3 提供了一个布局示例,说明“切割 GND”概念。在 TDR 图和仿真结果中可以看到参考平面空隙的前后影响。

图 3-3 USB 3.1 示例“切割 GND”布局

图 3-3 USB 3.1 示例“切割 GND”布局