ZHCAE37A December 2019 – June 2024 AM67 , AM67A , AM68 , AM68A , AM69 , AM69A , DRA821U , DRA821U-Q1 , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1 , TDA4AEN-Q1 , TDA4AH-Q1 , TDA4AL-Q1 , TDA4AP-Q1 , TDA4APE-Q1 , TDA4VE-Q1 , TDA4VEN-Q1 , TDA4VH-Q1 , TDA4VL-Q1 , TDA4VM , TDA4VM-Q1 , TDA4VP-Q1 , TDA4VPE-Q1

4.5.3 仿真方法

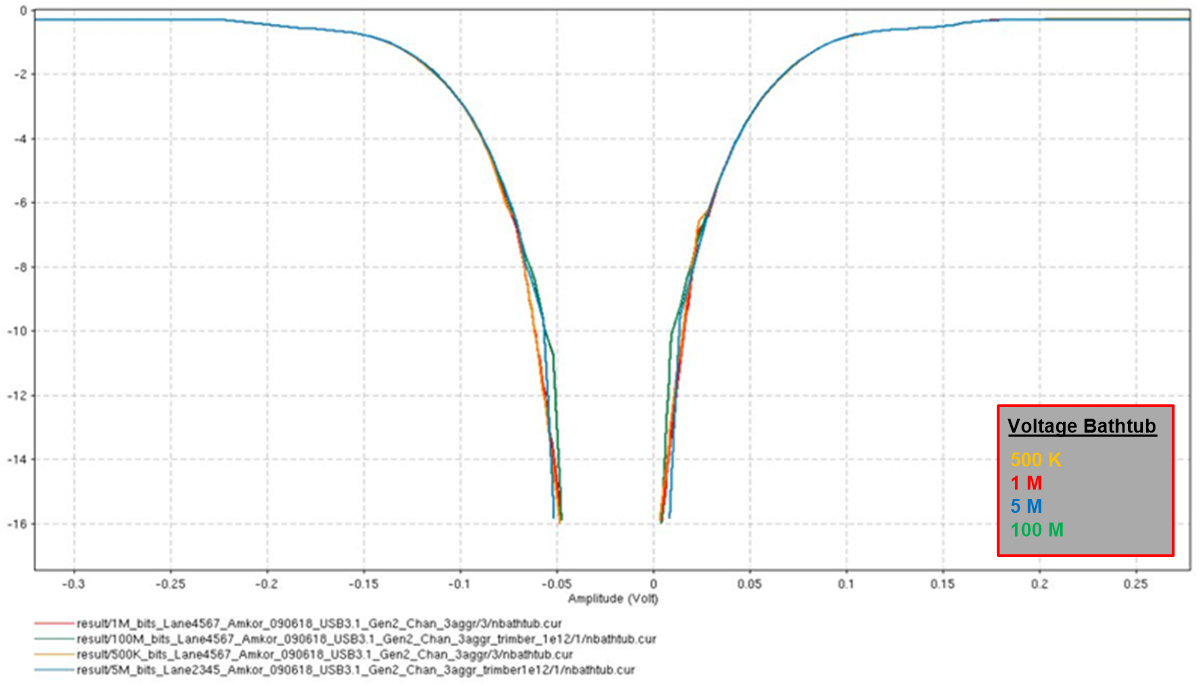

对于根据 BER 目标指定眼罩的接口,建议运行大约 100K 位的初始通道仿真,并观察模拟器报告的相应目标 BER 的推断浴盆曲线。可以重新运行另一个大约 500K 和 1M 位的仿真,并且可以叠加浴盆曲线,以观察运行更大位序列的影响。图 4-3 显示了叠加的电压浴盆曲线示例。可以对抖动浴盆曲线执行类似的叠加。

图 4-3 浴盆曲线叠加

图 4-3 浴盆曲线叠加通常,应该在仿真的前 100K 位中考虑所有 ISI,并且在此点之后,如果模型中的随机抖动 (Rj) 足够小,则所有浴盆曲线应该汇聚在一起。建议通过对 100K、500K 和 1M 位序列分别运行至少一组系统级通道仿真来预先确认该汇聚。如果每个仿真的电压和抖动浴盆曲线几乎相同,则其余仿真可在 100K 位下运行以优化运行时间。

对于没有为任何特定 BER 目标指定眼罩的接口,100K 位仿真应该足够了。