ZHCAE59 June 2024 AM623 , AM625

4 基于设计的方法与 HTOL 方法的比较

大多数情况下,精心设计的 HTOL 应力计划必须充分评估 TDDB 机制(如 GOI、ILD 故障)的寿命。这还可能包括检测导致 TDDB 过早故障的非固有缺陷。许多情况下,TDDB 机制并不是寿命可靠性的最终限制因素。

在 HTOL 过程中,即使在动态应力条件下(处理器的常规情况),通道热载波 (CHC) 和电迁移一般也不会明显加速。就 CHC 而言,(动态)HTOL 应力期间的时钟速率和压摆条件通常不利于 CHC 加速降级。偏置热不稳定性 (BTI) 会在 HTOL 中加速,这主要是由于高温和高电压造成,但 HTOL 期间在最坏情况电路上发生的动态开关活动并不能充分代表功能使用条件,特别是在考虑整体老化时,可以将 BTI 和 CHC 元件结合起来。

在 HTOL 偏置过程中,电迁移电流密度(也是时钟速率的一个重要函数)通常并不高,不足以证明在典型的 1000-2000 小时测试时间内(即使在电压升高的情况下),电迁移电流密度可达到 10 年以上的使用寿命。这需要更长的持续时间。通常情况下,结构应力模式(即基于 ATPG 的模式)与 HTOL 以及存储器或其他适用的 BIST 一起应用,时钟频率通常远低于最大工作频率。

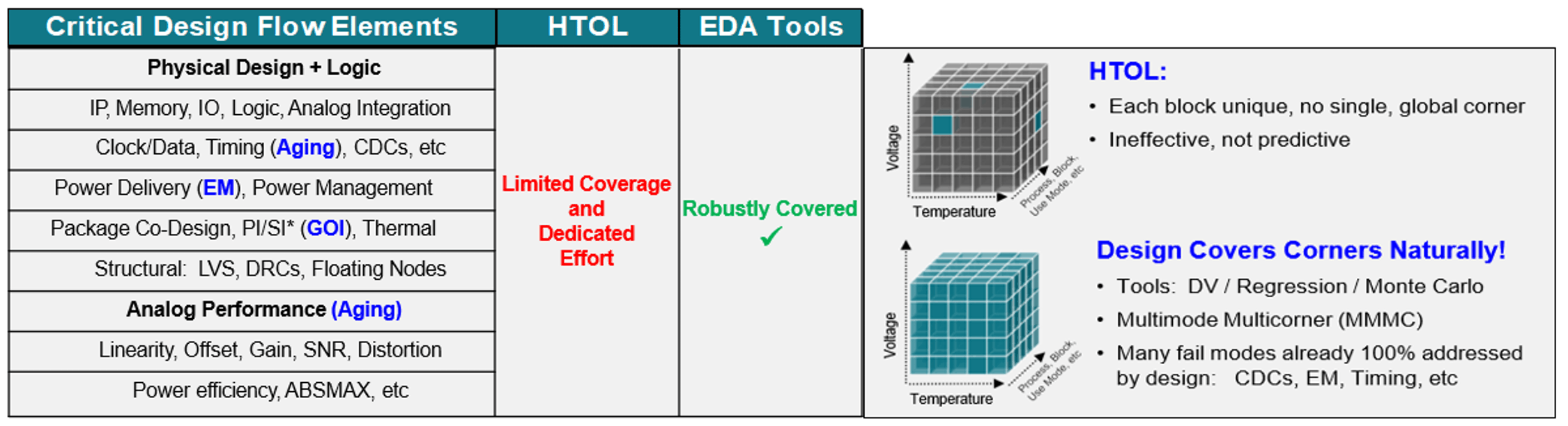

HTOL 覆盖的重点通常是更大限度地扩大节点的切换覆盖范围。通过磨损机制,了解设计中的相对薄弱点、最坏情况下的工作模式以及目标应力模式条件,从而更大限度地提高最坏情况下的 PVT 和频率角。不同的局部薄弱点(整个芯片上的 IP)可能有不同的最差边角。HTOL 中应用的典型 ATPG 和 BIST 模式很难加速目标电路上的所有最坏情况下的功能条件。图 6 进一步扩展了图 3,总结了 SoC 设计流程的关键方面,并比较了 HTOL 覆盖范围与 EDA 工具作为设计验证路径的有效性。指出了适用的可靠性故障机制。

图 4-1 HTOL 与 EDA 工具在关键设计流程要素设计验证中的功效对比

有关基于 HTOL 的米6体育平台手机版_好二三四可靠性估算的数学原理和缺点的更详细解释,请参阅附录 A。此外,附录 B 还介绍了电迁移可靠性的数学框架。