ZHCAE64 July 2024 TCA4307

3 串扰

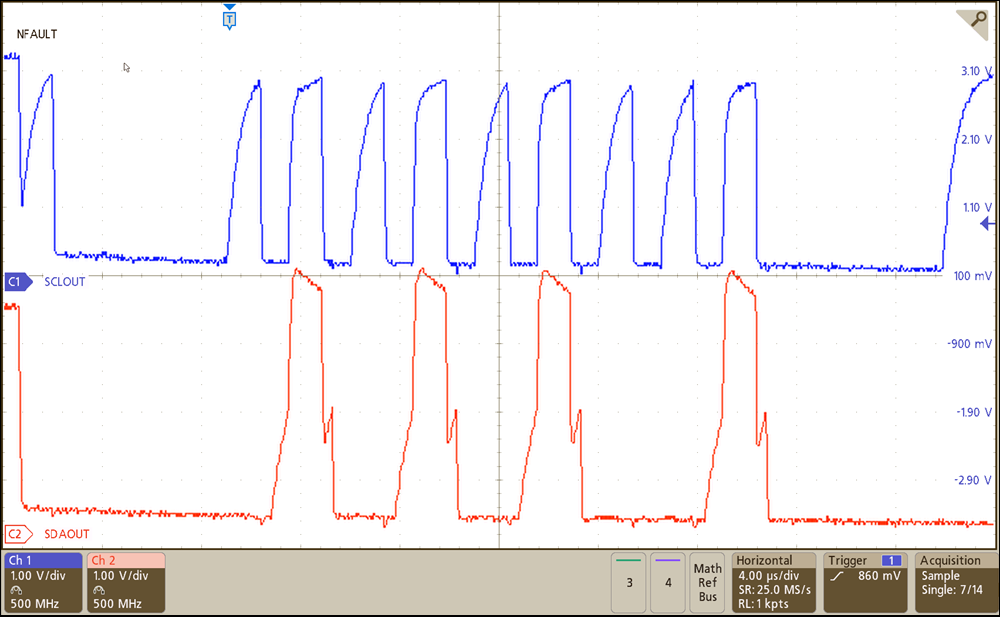

一种产生错误边沿的常见原因是串扰。通常情况下,就 I2C 而言,串扰是由两条线路(想象一下 PCB 上两条平行且间距很小的长布线)之间的共享电容和快速边沿速率产生的。正常情况下,如果 I2C 线路出现串扰,则在 SDA 或 SCL 线路处于逻辑高电平状态时便会发生串扰事件。这是因为在驱动低电平逻辑时,由于 I2C 的开漏架构,信号的偏置程度更强。逻辑高电平状态由上拉电阻器设置,但这与开漏驱动器相比弱得多。这些开漏驱动器的 Ron 比用于建立逻辑高电平信号的外部上拉电阻器强得多(具有低 Ron 值)。这意味着在大多数 I2C 事务中,SDA 线路上的信号可能出现串扰,因为除非 SCL 为低电平,否则 SDA 不会改变状态。这种情况的唯一例外是在启动条件期间,因此,如果足够严重,可能会出现错误时钟边沿。如果发生总线阻塞问题,并且 SDA 线路上似乎存在串扰,则建议在启动条件下检查 I2C 事务的开头,以排除串扰是问题根源的可能性。

图 3-1 串扰示例

图 3-1 串扰示例这并不意味着发出干净的启动条件后时钟线路就不会受到威胁,SCL 布线附近其他更快的边沿在高电平期间仍会在 SCL 总线上引起串扰。此处的一个要点是需要对 I2C 布线进行正确布局,避免 SCL 与其他具有快速边沿速率的布线(包括 SDA)靠得太近(平行)。平行也可能意味着在 SCL 布线正下方布放高频或大电流驱动的布线。