ZHCUAE4A September 2020 – October 2022 ISO1640

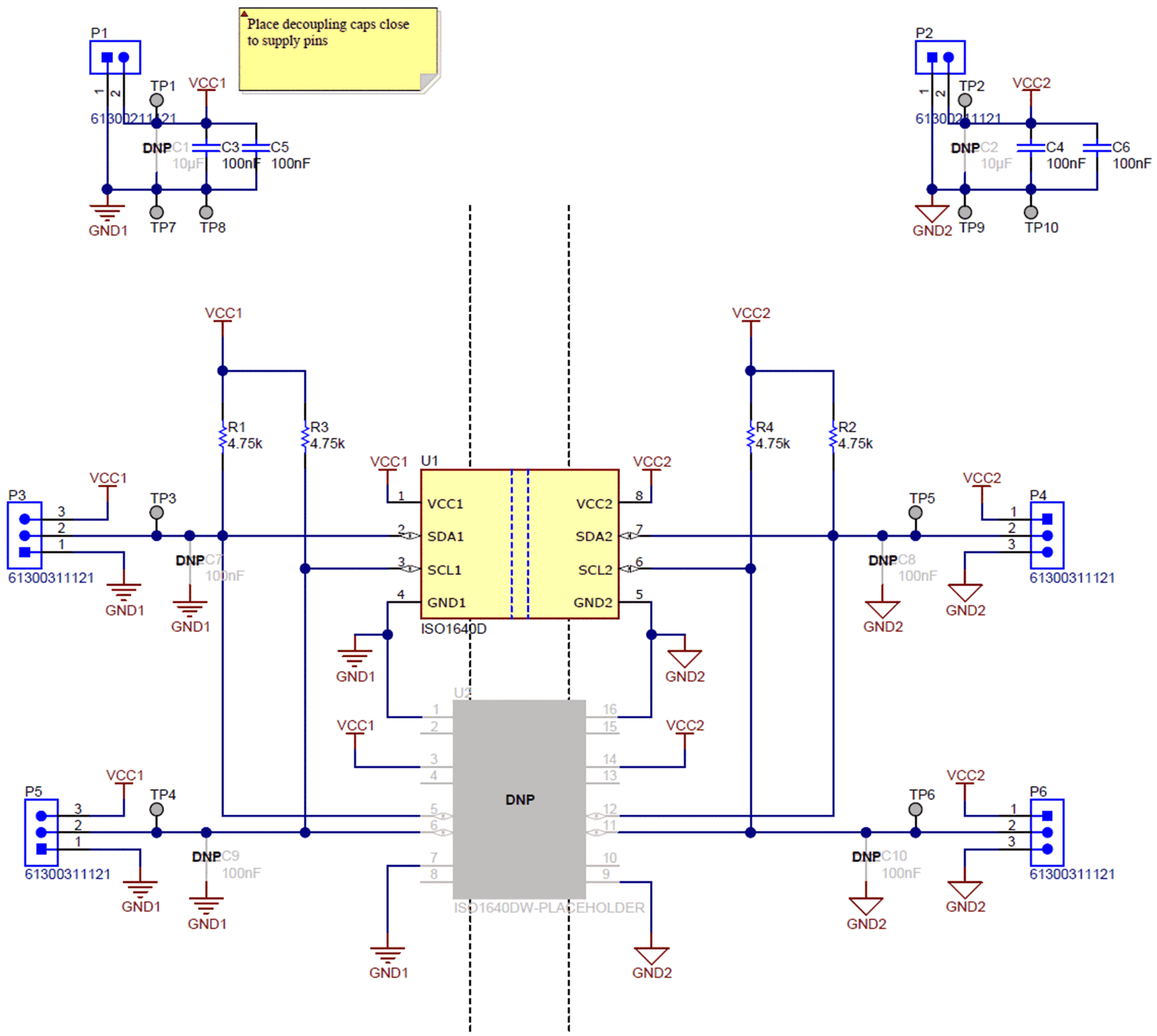

6 EVM 原理图和 PCB

ISO1640 隔离式 I2C EVM 随附一个安装在 U1 位置的 ISO1640D。该 EVM 还可以配置为与 ISO1641D、ISO1640DW 或 ISO1641DW 配合使用。

每条信号线(SDAx、SCLx)都配置有一个连接到相应电源 (Vccx) 的 4.75kΩ 上拉电阻器(R1 至 R4)。可以根据应用要求将这些电阻器替换为具有其他值的 0805 电阻器;有关计算 I2C 总线的相应上拉电阻器阻值的详细信息,请参阅 I2C 总线上拉电阻器计算 (SLVA689)。

注: ISO164x 器件用于在 1 侧和 2 侧灌入不同大小的电流,因此如果更换电阻器 R1 至 R4,请谨慎选择电阻器,确保 IOL1 和 IOL2 保持在建议工作范围内。

可以使用接地跳线(1 侧的 P3 和 P5;2 侧的 P4 和 P6)将信号引脚直接连接到接地端,以模拟将 I2C 线拉低的器件。这些线不会被主动驱动为低电平,将通过包含的上拉电阻器被上拉。不应在不使用上拉电阻器限制输入电流的情况下将信号线直接连接至电源电压。这些跳线还提供每个引脚的输入/输出信号访问(包括示波器探头)。

注: 确保 SDAx 和 SCLx 信号线没有直接连接到 Vccx。需要使用限流上拉电阻器,默认情况下已安装这些电阻器,以在器件引脚驱动低电压的情况下限制电流。

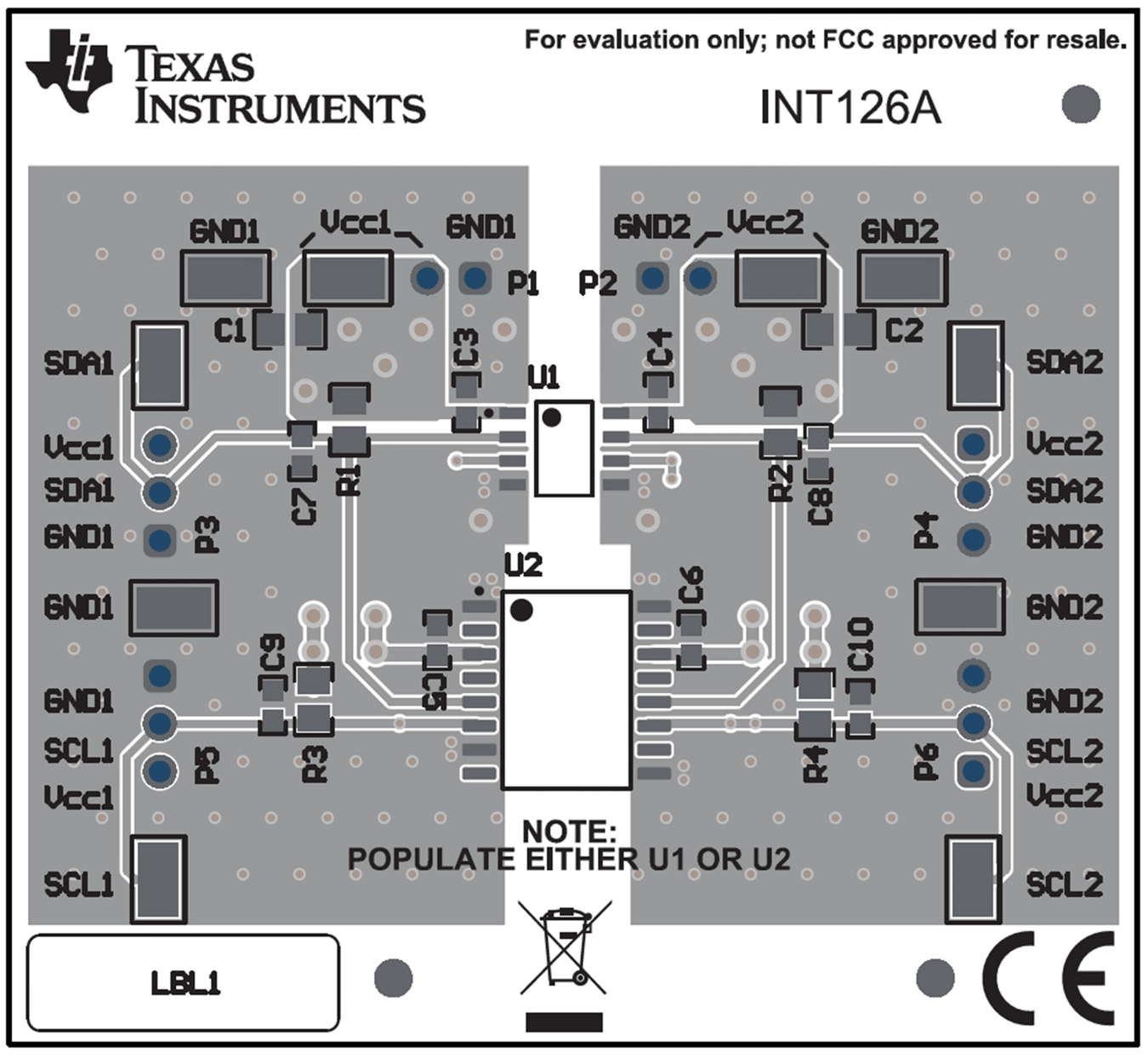

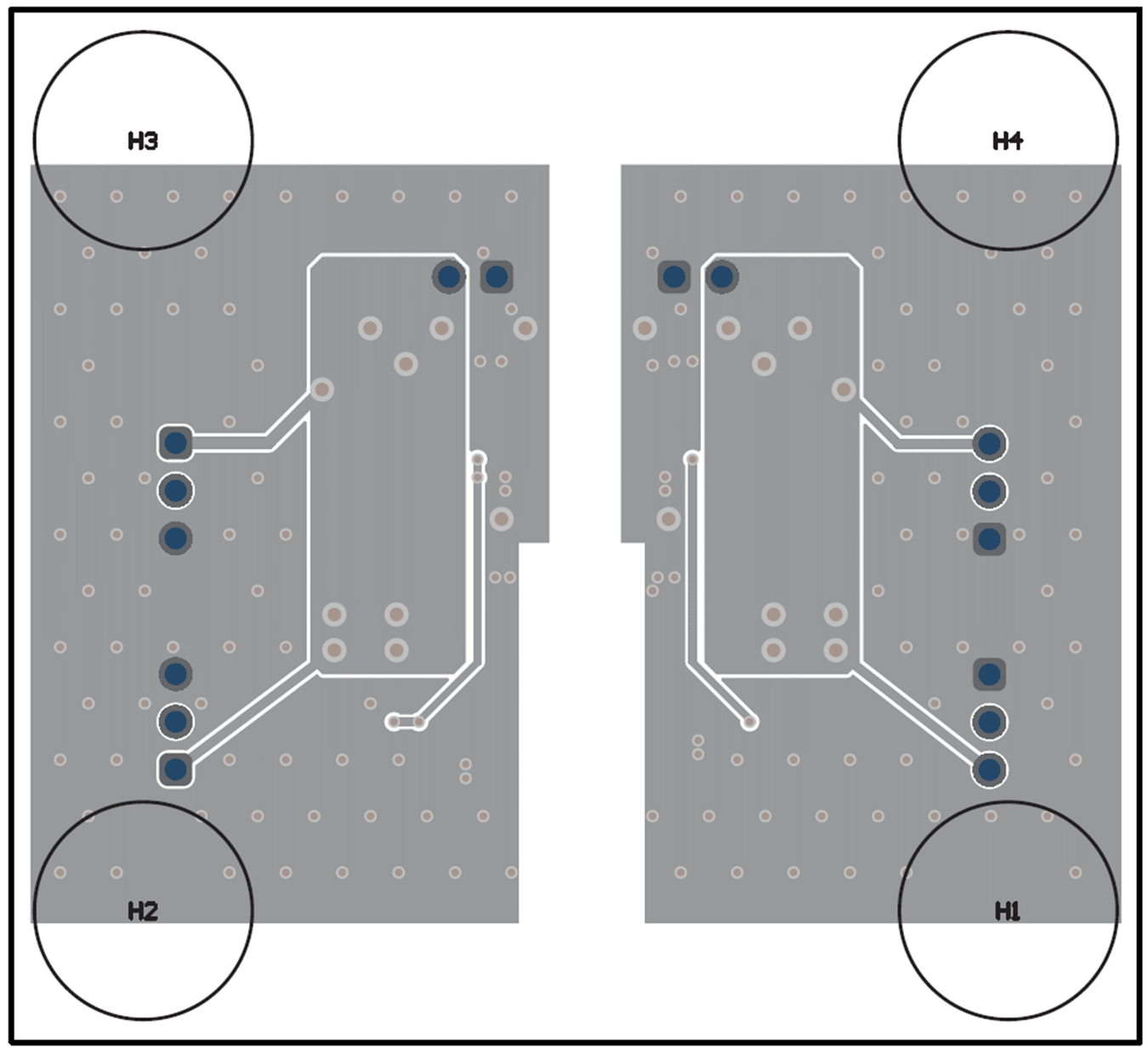

下面的图 6-1 显示了该 EVM 的原理图,图 6-2 和图 6-3 显示了印刷电路板 (PCB) 布局。

图 6-1 ISO1640DEVM 原理图

图 6-2 ISO1640DEVM 顶层 PCB 布局

图 6-2 ISO1640DEVM 顶层 PCB 布局 图 6-3 ISO1640DEVM 底层 PCB 布局

图 6-3 ISO1640DEVM 底层 PCB 布局