ZHCUC05A November 2022 – May 2024 AFE7900 , AFE7903 , AFE7906 , AFE7920 , AFE7921 , AFE7950

4 背景

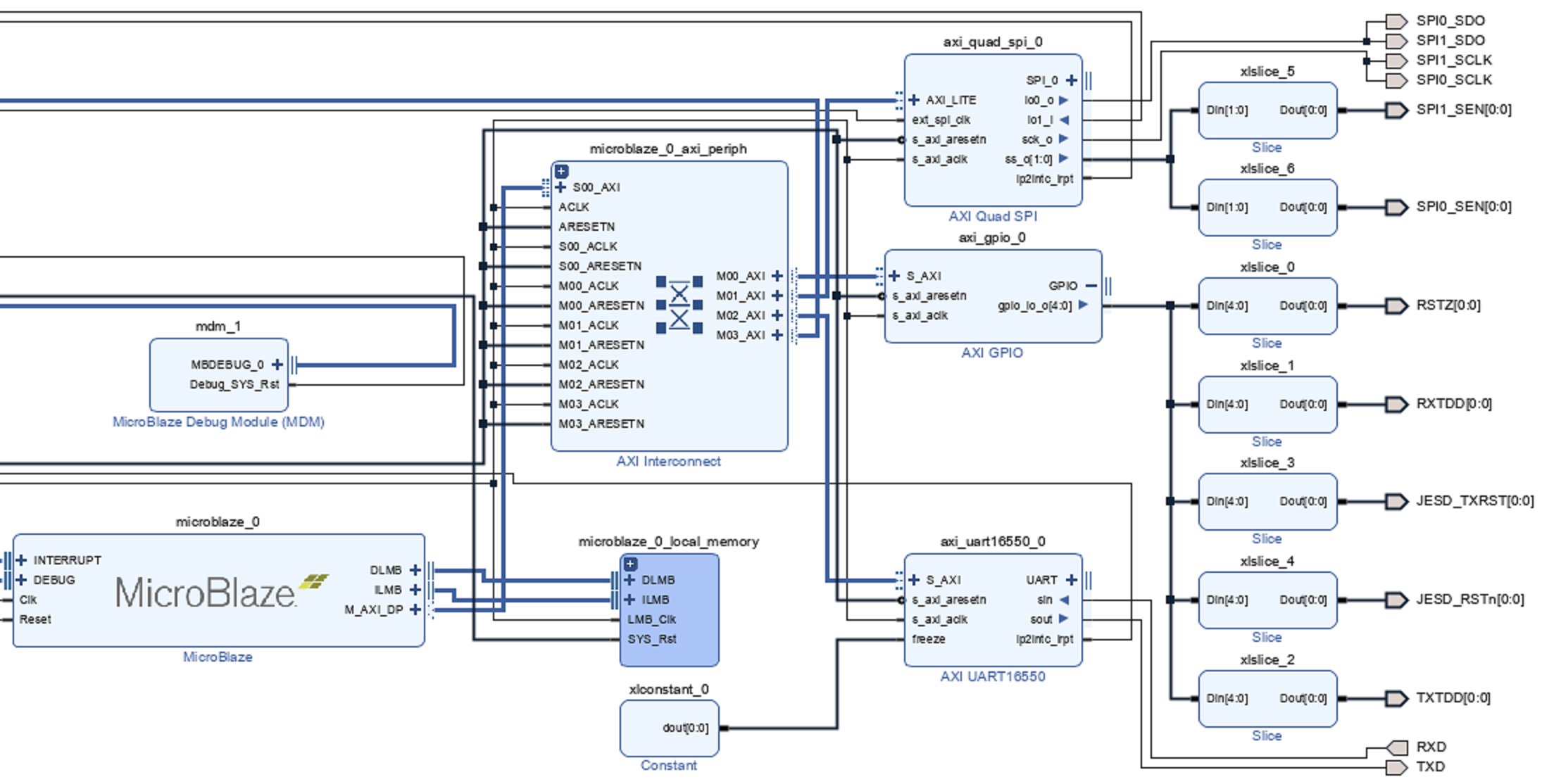

此示例使用了软核 Microblaze,因为 Microblaze 可以在大多数 Xilinx FPGA 系列中实例化。SPI、UART 和 GPIO AXI 块在频率相对较低的 AXI 时钟上运行。如图 4-1 所示,AXI 外设由 Microblaze 块通过智能互连进行控制。

图 4-1 采用 Microblaze 和 AXI 外设的典型块设计

图 4-1 采用 Microblaze 和 AXI 外设的典型块设计Microblaze 的 HP 端口驱动 AXI 外设块设计。100MHz 差分时钟源需要为整个 IP 提供时钟。此示例使用 100MHz 差分时钟源,因为该时钟在大多数 FPGA EVM 中通常作为“用户时钟”提供。所有其他时钟频率通过时钟向导在内部生成。根据系统中所需的独立 SPI 总线数量,可将更多 AXI SPI IP 添加到块设计中。