ZHCADI4A December 2023 – January 2024 UCC21220 , UCC21222-Q1 , UCC21520 , UCC21520-Q1 , UCC21530 , UCC21530-Q1 , UCC21540 , UCC21540-Q1

5 如何确定系统是否应限制窄脉冲?

下表显示了栅极驱动器内使系统设计更容易受到窄脉冲影响的一些常见场景,以及需要考虑的一些缓解策略。

| 易受窄脉冲影响的栅极驱动器场景 | 缓解 | |

|---|---|---|

| 导通电阻 (RG) | 较低的 RG 可能会导致较高的 di/dt。 | 调整 R G 有助于限制栅极驱动器的 di/dt。 |

| 外部 VDD | 具有更高的外部 VDD 会在窄脉冲超出器件的绝对最大额定值的情况下留下更小的裕度。 | 请考虑在应用中限制 VDD 范围。 |

| 去耦电容器放置 | 将去耦电容器放置在远离栅极驱动器引脚的位置会产生负面影响,并会增加系统中的寄生引线电感。 | 为了减小寄生电感,应将去耦电容器尽可能靠近栅极驱动器放置。有关布局建议,请参阅 TI 数据表。 |

如前一节所述,若要避免窄输入命令中出现电压尖峰,高 以及寄生电感是最重要且最简单的控制因素。延长脉冲宽度以确保栅极驱动电流降至接近零可有效地更大限度减小电流变化 .

确定系统最小脉冲宽度的一种方法是监测 MOSFET VGS 电压,以确定导通或关断转换是否已完成。为了确保窄脉冲的负面影响不会损坏栅极驱动器,主要建议是在再次更改状态之前使驱动器输出上升至高于 VDD 的 90%,以实现导通时的零电流开关。

如果出现关断脉冲,请在重新导通之前将输出降至 VDD 的 10% 以下。这可确保在 PCB 上和元件封装连接中存在寄生电感的情况下,不会因高电流的非零电流开关而产生较大电压尖峰。

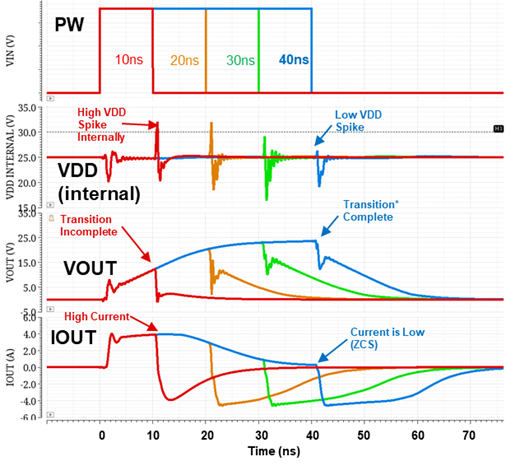

图 5-1 显示了 VOUT、IOUT、栅极驱动器的内部 VDD 和一系列脉冲宽度之间的关系,以显示完成转换所需的时间。在此示例中,40ns 的最小脉冲宽度使 IOUT 为低电平以实现 ZCS。如果是 10ns 脉冲宽度,则在接近最大输出电流的情况下为 IOUT 供电,并且 VOUT 尚未完成完整的导通转换。寄生电感可能会在栅极驱动器内部产生高电压尖峰,从而导致内部 VDD 超过栅极驱动器的绝对最大 VDD 电压。栅极驱动器损坏可能无法立即显现,但违反器件的绝对最大额定值可能会影响内部电路的完整性,从而导致集成电路因电过应力而出现故障或物理损坏。

图 5-1 Vout 和 VDD 内部电压随导通脉冲延长的变化

图 5-1 Vout 和 VDD 内部电压随导通脉冲延长的变化